# Speeding Up Hardware Verification by Automated Data Path Scaling

# Dissertation

zur Erlangung des akademischen Grades Doktor der Naturwissenschaften (Dr. rer. nat.) der Technischen Fakultät der Christian-Albrechts-Universität zu Kiel

# Peer Johannsen

Kiel, im August 2002

| 1. Gutachter:                 | Prof. Dr. Th. Wilke     |

|-------------------------------|-------------------------|

| 2. Gutachter:                 | Prof. Dr. WP. de Roever |

|                               |                         |

|                               |                         |

| Datum der mündlichen Prüfung: | 18. Dezember 2002       |

|                               |                         |

|                               |                         |

|                               |                         |

|                               |                         |

# Acknowledgments

Ask, and it will be given you, seek, and you will find, knock, and it will be opened to you.

For every one who asks receives, and he who seeks finds, and to him who knocks it will be opened.

- Matthew, Chapter 7:7 -

Per Aspera ad Astra ...

- A rough road leads to the stars -

The completion of this work brings to a close a long journey. Many have helped me along the way, but rather than thanking a great number of people, I want to thank a number of great people. People who have assisted me and without whom I could not have succeeded. This work would not have been possible without their help and support.

First of all, I want to thank my supervisors Thomas Wilke and Willem-Paul de Roever at the University of Kiel for reviewing my thesis and for agreeing to a long-distance collaboration and supervision. Their careful advice has considerably influenced my work. Furthermore, I want to thank Margrit Krause and Erich Valkema for their help and for the very pleasant atmosphere at the chair during all my visits to Kiel. In addition, I want to thank Wolfgang Thomas at the RWTH Aachen, whose teaching and guidance has been a constant source of inspiration and help over the last years.

Secondly, I want to thank Siemens Corporate Technology and Infineon Technologies for giving me the opportunity to do the research that resulted in this thesis at their research centers in Munich, Germany, and for providing a highly inspiring research environment. Working between the two worlds of academia and industry and being concerned with real world industrial applications had considerable impact on my research. My sincere thanks go to Wolfram Büttner for his great

commitment to the concerns of the PhD students at Siemens, and to the whole CVE Team and all my colleagues at Siemens and Infineon. Many of them have provided invaluable help with all steps involved in putting together a thesis. This can only be a partial list, but I want to name Markus Kaltenbach, Thomas Rudlof, Rolf Drechsler and Raik Brinkmann, with whom I have closely worked together. Special thanks go to Michael Siegel for always sparing his time to discuss countless technical questions, for proof-reading and commenting of earlier versions, and for his advice on preparing the thesis and the conference papers.

Further thanks, which I also owe to Siemens Corporation and to Infineon Technologies, are for offering me the possibility of spending one and a half years of research work at their local subsidiaries in San Jose, California. Those 18 months have deeply influenced my life in many respects. Thanks go to the designers at Infineon CNP for introducing me to the field of hardware design and for sharing their insights in the design and simulation process. Special thanks to Gabriele Miller for emotional support and for showing me the best Sushi places in the Bay Area. Further thanks to Diana for providing donuts and bagels every Friday. Additionally, I thank Natarajan Shankar from SRI International for the invitation and the inspiring day at their office in Menlo Park.

Yet, this thesis would not be as it is without the help, support and friendship of lots of people who are not directly concerned with my work. Especially, and with all my heart, I want to express my gratitude to Peggy and Andy Gouw for embracing me and taking me in with all their warmth. I still consider you family! And Daniel, I keep hoping to meet you and see you compete at the 2004 Olympic Games!

I also thank Leighton Ridgard for being a friend from the first day we met and for being a magnificent badminton doubles partner. On all those trips to the gym and to the movies you reminded me that there are more things in life than just working. Further thanks to all the players at Sun Jose State and to the guys from Gunn High (Steve, John, Jonas, Russ, Steven, Percy, Ho, Jason, Jerome, ...) for the great games on challenge court on Sunday afternoons, keep on stroking! Thanks to all the members of the Sunnyvale Badminton Club (Ben, Andy, George, ...) and to all the kids I was coaching during that time (Eva, Jordan, Daniel, Michael, ...), I miss you all! And of course thanks to Starbucks for the Extra Grande Caramel Latte Machiato, to the Mongolian Barbecue and the Kobe Restaurant for excellent food, and to Trader Joe's for a life-saving supply of Milka chocolate.

Last, but certainly not least, I owe thanks to my family, my mom and dad, and to my friends for constantly giving support. A dearest thank you goes to Mirjana Ćosić for encouraging me and giving me the strength to go on, to Elke Siwochin, and to my old pal Michael 'Micky' Packhäuser, no matter how far apart, you were always there. In particular, I also want to express my very gratitude to Mirka Stroetzel who was the one who was there for me when I really wanted to give up and pack it all in.

Finally, I am obliged to Infineon Technologies for allowing me to take time off work in order to complete my degree.

# Contents

| 1        | Intr                                          | roduction                                                           | 1  |  |

|----------|-----------------------------------------------|---------------------------------------------------------------------|----|--|

|          | 1.1                                           | High-Level Information                                              | 2  |  |

|          | 1.2                                           | Objectives of this Thesis                                           | 3  |  |

|          |                                               | 1.2.1 Scaling Down Design Sizes by Signal Width Reduction           | 3  |  |

|          |                                               | 1.2.2 Minimum-Width Reductions of Bitvector Satisfiability Problems | 4  |  |

|          |                                               | 1.2.3 One-To-One Abstraction to Speed Up Verification               | 6  |  |

|          | 1.3                                           | Annotated Table of Contents                                         | 7  |  |

| <b>2</b> | Hig                                           | h-Level Property Checking of Digital Hardware                       | 9  |  |

|          | 2.1                                           | Bounded Model Checking                                              | 9  |  |

|          | 2.2                                           | The Property Checking Framework                                     | 14 |  |

|          | 2.3                                           | Utilizing High-Level Information for Verification                   | 14 |  |

|          |                                               | 2.3.1 Integer Linear Programming                                    | 16 |  |

|          |                                               | 2.3.2 Rewriting                                                     | 16 |  |

|          |                                               | 2.3.3 Symmetry Reductions                                           | 17 |  |

|          |                                               | 2.3.4 Word-Level Decision Diagrams                                  | 18 |  |

|          |                                               | 2.3.5 Abstraction                                                   | 18 |  |

|          | 2.4                                           | Scaling Down RT-Level Designs                                       | 19 |  |

|          | 2.5                                           | Signal Width Reduction                                              | 25 |  |

| 3        | Fixed-Size Bitvectors and Bitvector Functions |                                                                     |    |  |

|          | 3.1                                           | Fixed-Size Bitvectors                                               | 29 |  |

|          | 3.2                                           | Bitvector Functions                                                 | 32 |  |

|          | 3.3                                           | Bitvector Operators                                                 | 32 |  |

|          | 3.4                                           | Bitwise Bitvector Functions                                         | 41 |  |

|          | 3.5                                           | Corresponding Bitwise Bitvector Functions                           | 44 |  |

| 4        | Red                                           | lucing Bitvector Satisfiability Problems                            | 47 |  |

|          | 4.1                                           | Preliminaries                                                       | 47 |  |

|          | 4.2                                           | The Satisfiability Problem <b>BvSAT</b> for Bitvector Functions     | 50 |  |

|          | 4.3                                           | <b>BvSAT</b> and Bitwise Bitvector Functions                        | 51 |  |

|          | 4.4                                           | Disequality Constraints                                             | 54 |  |

|   | 4.5  | The Enhanced Satisfiability Problem $BvSAT(\mathcal{F}_{[n]},I)$  | 57  |  |

|---|------|-------------------------------------------------------------------|-----|--|

|   | 4.6  | The Enhanced <b>BvSAT</b> Problem and Bitwise Bitvector Functions | 59  |  |

|   | 4.7  | Disequality Graphs                                                | 61  |  |

|   | 4.8  | Reduction Theorems and Proofs                                     | 66  |  |

|   | 4.9  | Order Constraints                                                 | 77  |  |

| 5 | Bit  | vector Terms and Systems of Bitvector Equations                   | 83  |  |

|   | 5.1  | Bitvector Terms                                                   | 83  |  |

|   | 5.2  | Interpretation of Bitvector Terms by Bitvector Functions          | 88  |  |

|   | 5.3  | Systems of Bitvector Equations                                    | 90  |  |

|   | 5.4  | Satisfiability of Bitvector Equations                             | 91  |  |

|   | 5.5  | Checking Satisfiability of Systems of Bitvector Equations         | 95  |  |

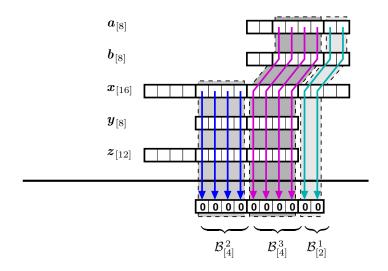

| 6 | Bity | wise Decompositions of Systems of Bitvector Equations             | 97  |  |

|   | 6.1  | Motivating Example                                                | 98  |  |

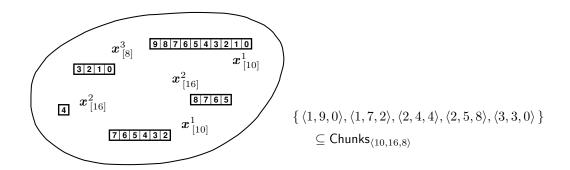

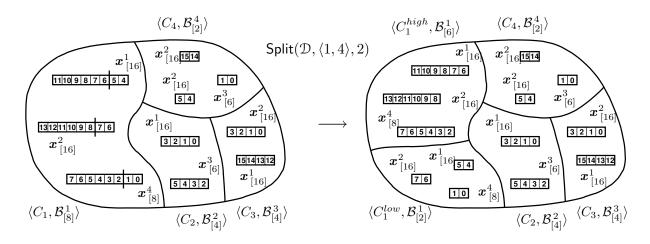

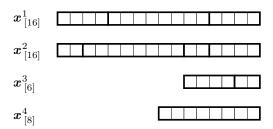

|   | 6.2  | Chunks of Bitvectors and Sets of Chunks                           | 104 |  |

|   | 6.3  | Partially Bitwise Bitvector Functions                             | 107 |  |

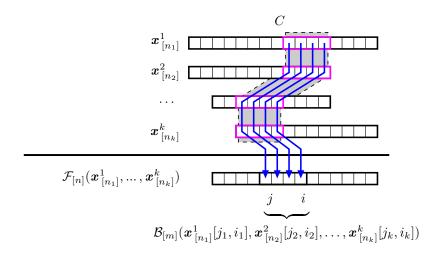

|   | 6.4  | Bitwise Decomposition                                             | 109 |  |

|   | 6.5  | Computing the Decomposition                                       | 113 |  |

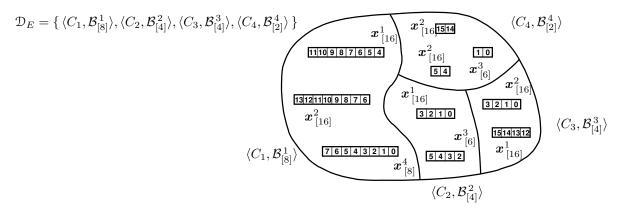

|   | 6.6  | Modifying the Decomposition                                       | 115 |  |

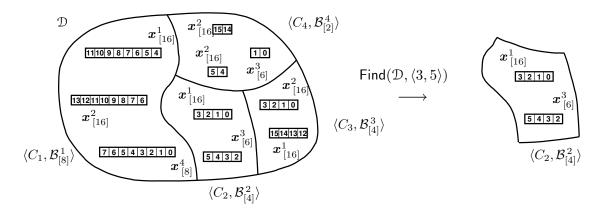

|   |      | 6.6.1 Find                                                        | 115 |  |

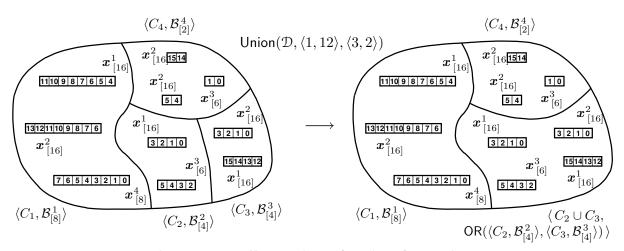

|   |      | 6.6.2 Union                                                       | 116 |  |

|   |      | 6.6.3 Split                                                       | 119 |  |

|   | 6.7  | The Central Procedure: Bitwise Slicing                            | 121 |  |

| 7 | Nor  | Normalizing Systems of Bitvector Equations 129                    |     |  |

|   | 7.1  | Characterizing Satisfiability of Bitvector Equations              | 130 |  |

|   | 7.2  | Boolean Bitvector Terms and Boolean Bitvector Equations           | 131 |  |

|   | 7.3  | Normalized Systems of Bitvector Equations                         | 134 |  |

|   | 7.4  | Normalization of Bitvector Terms and Bitvector Equations          | 135 |  |

|   |      | 7.4.1 Normalization of Bitvector Constants                        | 137 |  |

|   |      | 7.4.2 Normalization of non Boolean Expressions                    | 139 |  |

|   |      | 7.4.3 Normalization of Extractions                                | 142 |  |

|   | 7.5  | Preprocessing                                                     | 144 |  |

|   |      | 7.5.1 Elimination of Concatenations                               | 144 |  |

|   |      | 7.5.2 Elimination of If-Then-Else Expressions                     | 145 |  |

|   |      | 7.5.3 Elimination of Arithmetic Expressions                       | 146 |  |

|   |      | 7.5.4 Evaluation of Constant Expressions                          | 146 |  |

|   | 7.6  | A Note on Computational Complexity                                | 146 |  |

| 8 | Har  | ndling Dynamic Data Dependencies 1                                | .51 |  |

|   | 8.1  | Motivation – Separating Control Flow and Data Flow                | 152 |  |

|   | 8.2  | Extending the Decomposition Technique                             | 156 |  |

| 9            | <b>App</b> 9.1                                  | Olying the Width Reduction Technique Generating Equivalent Systems of Bitvector Equations with Reduced Bitvector | 159 |  |

|--------------|-------------------------------------------------|------------------------------------------------------------------------------------------------------------------|-----|--|

|              | 9.2                                             | Widths                                                                                                           |     |  |

| 10           | Exp                                             | erimental Results                                                                                                | 169 |  |

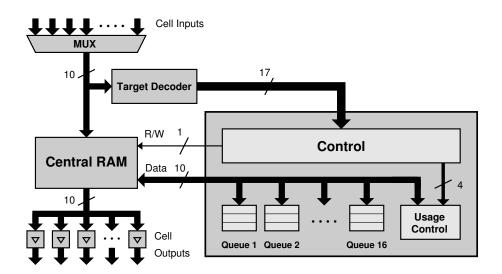

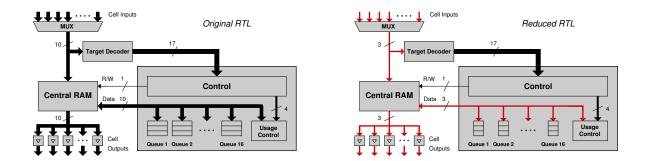

|              | 10.1                                            | Central Buffer Address Management Unit                                                                           | 169 |  |

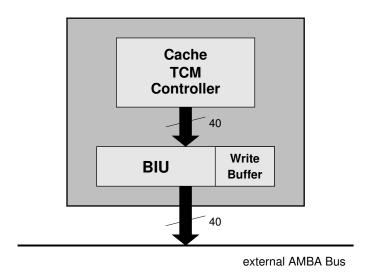

|              | 10.2                                            | Bus Interface Unit                                                                                               | 172 |  |

| 11           | 11 Conclusion and Directions of Future Research |                                                                                                                  |     |  |

|              | 11.1                                            | Summary                                                                                                          | 177 |  |

|              | 11.2                                            | Ongoing and Future Research                                                                                      | 178 |  |

|              |                                                 | 11.2.1 Tweaking the Amount of Scaling                                                                            | 178 |  |

|              |                                                 | 11.2.2 Improved Scaling of Memory Arrays                                                                         | 179 |  |

|              |                                                 | 11.2.3 Bitvector Arithmetics                                                                                     | 179 |  |

|              |                                                 | 11.2.4 High-Level Equivalence Checking and High-Level Simulation $\ \ldots \ \ldots \ \ldots$                    | 180 |  |

| Bibliography |                                                 | 181                                                                                                              |     |  |

| Lis          | List of Figures                                 |                                                                                                                  | 187 |  |

| Lis          | List of Tables                                  |                                                                                                                  |     |  |

| Lis          | st of                                           | Algorithms                                                                                                       | 193 |  |

# Chapter 1

# Introduction

Hardware verification has become one of the most important steps in digital circuit design. Today's hardware designs are highly integrated application specific circuits (ASICs), which are used in a wide-spread field of implementations, ranging from entertainment electronics and domestic appliances to business-relevant industrial production lines and safety-critical systems, like for example cars, airplanes or medical devices. Circuit designs need to be checked in order to ensure that manufactured chips operate correctly according to their specifications.

The average time-to-market for custom chip designs presently is about 18 months, and approximately between 60–70% of project costs result from error detection and correction. Production of faulty circuits requires redesigns and enlarges the number of design cycles. Each redesign of an averagely sized ASIC and each further design cycle causes additional costs of several hundred thousands of dollars. Efficient testing for correct behavior becomes more and more important and a major economical issue. It is desirable to detect design faults before manufacturing and thus to keep the number of design cycles and redesign costs as small as possible. Yet, fabricating hardware prototype chips, which can be used for testing already during the design phase, is time-consuming and expensive.

In the past, simulation was the common way to validate functionality of circuit designs, and still is today. But even for relatively small and plain designs exhaustive simulation almost always is impossible due to the immense number of input-stimuli that need to be checked. In practice, pure simulation can be used only for a partial validation of circuit functionality and cannot prove complete functional correctness.

Formal methods for functional hardware verification are becoming increasingly attractive in Electronic Design Automation (EDA), since they prove correct design behavior before manufacturing and without exhaustively simulating a design. Over the past years, a variety of formal verification techniques and methodologies has been proposed for hardware verification. However, only rather few techniques have shown to be suitable for application in an industrial environment. In the first place, this is caused by insufficient performance on large industrial designs, and secondly by the fact that the use of most techniques still requires expert knowledge of formal verification, which is normally not present in hardware design teams of chip manufacturing companies. Replacing simulation by formal verification especially is difficult if verification techniques

are not fully automated. Full automation of formal verification methods and the possibility for an easy integration into existing hardware design flows are required in order to be effectively applied in industrial hardware development processes, as well as a fairly ease of use and the capability of coping with real world design sizes.

Recently, Bounded Model Checking (BMC, see e.g. [BCC<sup>+</sup>99, BCCZ99, BCRZ01]), also referred to as Property Checking (see Chapter 2), has proven to be highly applicable for circuit verification. In BMC, a formal property is verified which describes an intended behavior of a given digital design within a finite bounded interval of time. BMC problems can be mapped onto instances of the satisfiability problem for Boolean formulae (SAT), which can be tackled by Boolean constraint solvers and Boolean function manipulation techniques. Recent advances in work on data structures, like Binary Decision Diagrams (BDDs, see e.g. [Bry86, Bry92, Bry95]), and advances in work on SAT solver technologies (see e.g. [LS01, MMM<sup>+</sup>01, Sht00, Sht01, SS96, SS99]) have made BMC a key technology to quality assurance in modern industrial hardware development processes, as is surveyed in [SS00]. The majority of today's most powerful industrial hardware verification tools is based upon multi-engine concepts of the above-mentioned technologies.

However, the SAT problem is known to be NP-complete, and design sizes are ever increasing. Nowadays, digital circuit designs frequently contain up to several million transistors. Verification of such large designs becomes more and more difficult, time-consuming and expensive. Formal verification methods are pushed to their limits, and verification tasks often cannot be completed due to design sizes and complexity issues, or simply cannot be executed because of resource limitations of today's computing machinery. Reducing runtimes and the amount of memory needed for computations is the priority objective in order to match today's sizes of real world designs in hardware verification. At the same time, ever improving verification techniques are required.

In this thesis a specific type of Bounded Model Checking problems is considered, and a new one-to-one abstraction technique for formal hardware verification of digital circuits is presented. The proposed abstraction technique exploits high-level design information in order to reduce the sizes of the BMC problems and thus to speed up the runtimes of SAT and BDD based hardware verification.

## 1.1 High-Level Information

Verification techniques for Bounded Model Checking of digital hardware are usually based on bit-level methods and bit-level formalisms (see [BCC<sup>+</sup>99, BCRZ01, SS00]). All variables occurring in a BMC problem are Boolean variables, representing single-bit signals of the circuit design. Circuit functionality is described by Boolean logic operations, and the verification task is solved in the Boolean domain. However, hardware designers normally specify digital circuits on a higher level of design abstraction, called Word-Level or Register-Transfer-Level (RTL). On this level of abstraction, collections of one-bit signals are grouped into semantic units (words, registers) with respect to circuit functionality. High-level data structures, like for example multi-bit signals, and high-level operators (i.e. operational units on high-level data structures) are available to describe circuit functionality.

Industrial design specifications are written in *Hardware Description Languages* (HDLs), like VHDL or Verilog, which allow to conceptualize the control flow and data flow of digital circuits on word-level. HDLs support common word-level data types (like for example registers), word-level data structures (like for example arrays and busses) and typical high-level operations performed in digital hardware, like for example shifting, addition and multiplication. A variety of standard tools is used in the design flow which read and further process HDL source code, like tools for simulation, timing analysis and physical layout. For verification purposes, HDL circuit design specifications must be transformed (*synthesis*) into bit-level models (e.g. Boolean formulae) before BMC techniques can be applied.

ASIC designs generally consist of hierarchies of building blocks. Often, designs, like for example ALUs, memory arrays or bus interfaces, have very regular structures that can easily be described on a higher level of abstraction. Likewise, higher levels of design abstraction allow an easy recognition of those structures. Complex structural information can conveniently be deduced from high-level specifications, whereas bit-level descriptions lack adequate means to syntactically reflect semantic information on such structural regularities. RTL specifications of digital circuits explicitly contain structural information which can be exploited to simplify hardware verification. This type of high-level information is not available in plain bit-level descriptions and cannot be utilized by verification tools if verification procedures operate on the basis of bit-level descriptions only. The information is lost during the transformation of RTL specifications into bit-level models while synthesis.

Recently, several approaches to formal circuit verification have been proposed which are based on RTL specification formalisms and which make use of structural high-level information. Examples are high-level verification techniques, like Word-Level Decision Diagrams (see e.g. [BC94, DBR97, CKRZ01, HD99, AH97, WAH01, Dre00]), Integer Linear Programming (e.g. [FDK98, BD02, ZKCR01, ZKC01]), Symmetry Reductions (e.g. [CEJS98, ET99]) and Term Rewriting (e.g. [DJ90]), to survey only a few. Other promising approaches to enhance the capabilities of existing formal verification tools are based on Uninterpreted Functions (see e.g. [BGV99, VB99, VB98, HIKB96, PRSS99]) or on Automated Abstraction Techniques (see e.g. [Joh01a, CGL92]).

### 1.2 Objectives of this Thesis

This thesis proposes a new word-level abstraction technique which speeds up property checking of digital hardware by reducing design sizes before verification. The proposed technique was first presented in [Joh01a]. Further details were presented in [Joh01b, Joh01c, JD01] and [JD02a, JD02b]. The technique exploits structural high-level information in RTL circuit specifications and automatically scales down the width of data path signals with respect to the property which is to be verified while trying to achieve a maximum degree of scaling.

### 1.2.1 Scaling Down Design Sizes by Signal Width Reduction

The core functionality of this approach is based on a simple and straightforward idea. High-level design specifications of digital circuits contain the structural information on how single bits are arranged to represent word-level signals and which individual bits belong to the same word-level

signal. The information about the widths of data path signals and about word-level data flow is available and can be exploited. Under specific conditions, it is possible to replace an n-bit data path of a circuit design by an m-bit data path, with m < n, and then to use the scaled and smaller version of the design for verification instead of the original one without altering verification results.

By now, data path scaling is a classical means for attacking the state space explosion problem. Reduction of data path widths is typically tried if verification of an ASIC which includes an n-bit data path takes too long or cannot be completed due to reasons of computational complexity, but up to now this technique has lacked full automation and a clear methodology on a formal basis. Still, many EDA companies today perform such reductions manually to speed up verification runtimes. Data path scaling is done based on experience and intuition of the circuit designer, very often without having the (formal) guarantee that the property which is considered and has to be verified really is independent of the width of the data path and that the chosen amount of scaling does not falsify verification results. Moreover, such manual modifications usually require intensive rewriting of the HDL code as shrinking the width of a data path causes additional side-effects. If, for example, a 32-bit bus is replaced by a bus of smaller width, say 16-bit, then the width of each signal which accesses the bus by read or write operations must be scaled too. Side-effects can go even farther if such a signal is the concatenation of several other smaller signals. Consider a design where a 24-bit signal reads information from the 24 most-significant bits of the bus while another 8-bit signal reads the 8 least-significant bits. At the outset, it is not clear how reducing the bus-width to 16 bits affects the two signals which read from the bus and how scaling has to be applied to them.

This thesis formalizes a new methodology which allows for a fully automated scaling of data path widths. The proposed technique efficiently analyzes word-level data flow in RTL descriptions with respect to a specified property. Designs are automatically scaled down by reducing signal widths before property checking, while guaranteeing that the property holds for the scaled model if and only if it holds for the original design. The reduced model of the circuit is used as input to existing hardware verification methods instead of the original design, thus speeding up property checking runtimes and allowing larger design sizes to be verified.

### 1.2.2 Minimum-Width Reductions of Bitvector Satisfiability Problems

The proposed abstraction technique is based on data flow specification by means of formal bitvector theories (see e.g. [CMR96, MR98]). Bitvector theories have proven to be an adequate means of describing digital hardware and related Bounded Model Checking problems at a higher level of design abstraction. Bitvectors are array-like structures of finite width over a two-valued domain, which can be used to model multi-bit circuit signals (see Chapter 3). Word-level data flow and control flow aspects of digital designs can be characterized by bitvector equations (see Chapter 5) in a way, such that design properties can be verified by determining satisfiability of such equations. Several decision procedures have been investigated which determine satisfiability or validity of bitvector equations, see e.g. [BDL96, BDL98, BP98, CMR96, CMR97, MR98, Joh99]. However, either the expressiveness of the term languages and the bitvector theories which are used is rather limited, or the performance of the decision procedures cannot compete with SAT and BDD based property checking when applied to large real world circuit designs.

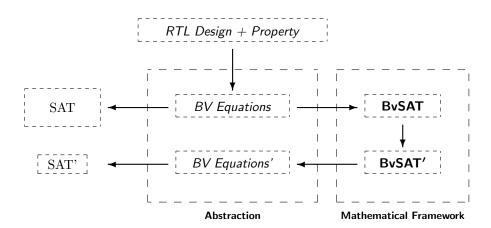

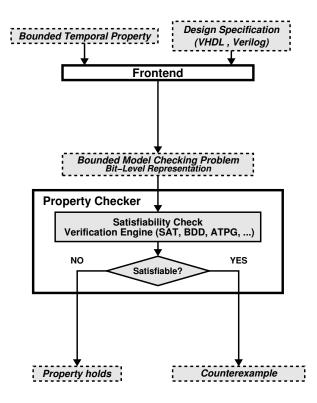

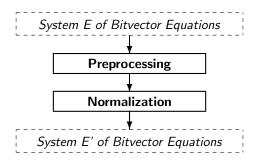

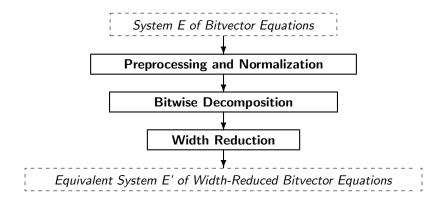

This thesis proposes a different approach to deciding satisfiability of a system of bitvector equations. Instead of trying to directly solve the equations, the high-level information contained in the bitvector terms is used to compute a second corresponding and equivalent system of bitvector equations for which then satisfiability is determined by using conventional SAT and BDD based methods. Thus, a high-level abstraction technique for systems of bitvector equations is established, which is characterized in the way that the SAT problem which is related to the second system is smaller than the SAT problem related to the original system and therefore generally can be decided much faster and with less effort (see Figure 1.1 for an illustration of the basic concept).

Figure 1.1: Basic Concept

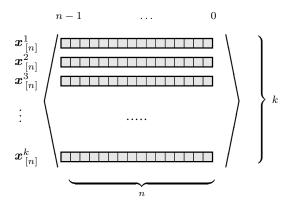

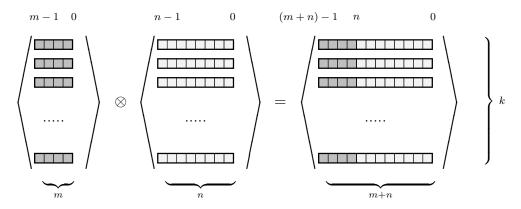

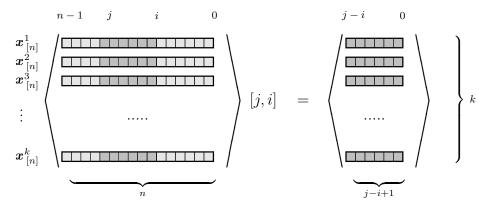

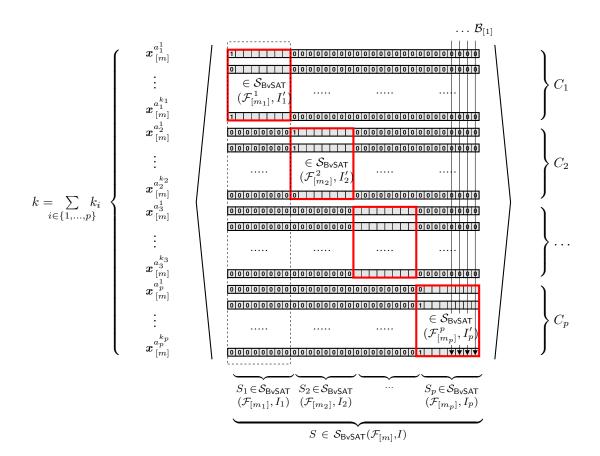

One of the primary foci of this work is the investigation of satisfiability problems for an enhanced theory of fixed-size bitvectors which allows to describe complete real world BMC problems on RT-Level. We introduce the formal satisfiability problem BvSAT for bitvector functions and bitvector disequalities, which was first presented in [Joh01c] and which is a generalization of the SAT problem from Boolean variables to bitvectors of finite width (see Chapter 4). Satisfiability of systems of bitvector equations can be reduced to satisfiability of instances of BvSAT (see Chapter 6). The BvSAT problem constitutes the mathematical framework which we use to study satisfiability of systems of bitvector equations. We investigate in detail how satisfiability of BvSAT depends on the widths of the bitvector domains.

From the theoretical point of view, the main contribution of this thesis is a size reduction of **BvSAT** problems by means of a formal one-to-one correspondence between given instances of **BvSAT** and related instances over bitvector domains of *smaller* width. This correspondence maps satisfiable instances onto smaller satisfiable instances, and unsatisfiable ones onto smaller unsatisfiable instances. The correspondence is characterized by two theorems which prove correctness (i.e. the correspondence preserves satisfiability in a one-to-one fashion) and show optimality of the reductions (i.e. the correspondence yields minimal bitvector widths, see Chapter 4). The second contribution of this thesis is a high-level abstraction technique which utilizes the results stated by this correspondence in order to reduce a system of equations over bitvectors of certain widths into an equivalent system over bitvectors of smaller widths, while preserving satisfiability of the equations in a one-to-one fashion. The reduction is based on symbolic analysis

of word-level data flow and detection of uniform data dependencies. The proposed reduction technique furthermore provides an efficient way to compute satisfying solutions of the original system from satisfying solutions found for the reduced system.

Satisfiability of bitvector equations can be checked in the Boolean domain by transforming systems of bitvector equations into Boolean formulae, i.e. into instances of propositional SAT, and afterwards applying bit-level satisfiability checks, like SAT and BDD based procedures. Thus, bitvector formalisms are ideally suited for combining BMC and high-level verification techniques. The complexity of determining satisfiability of Boolean formulae generally depends on the number of Boolean variables occurring in the formulae. When systems of bitvector equations are transformed into SAT problems, Boolean variables are generated for each bit of each bitvector variable. Thus, the complexity of checking satisfiability of systems of bitvector equations directly depends on the overall number of bits of all input, internal and output signals occurring in a design, i.e. on the sum of the widths of all bitvectors occurring in the equations. As a consequence, width reductions can have a significant impact on the runtimes of satisfiability checkers as can be seen in the sections on experimental results in Chapter 10.

### 1.2.3 One-To-One Abstraction to Speed Up Verification

From the practical point of view, the main contribution of this thesis is a new and fully automated word-level abstraction technique, which operates as a preprocess for property checking of digital hardware (see Chapter 2). The proposed method computes a one-to-one RTL abstraction of a digital design in which the widths of word-level signals are reduced with respect to a property. Given an RTL specification of a digital design and a property  $\varphi$ , a reduced RTL model is generated in which each word-level signal  $\boldsymbol{x}$  is replaced by a corresponding shrunken signal of width  $m_{\boldsymbol{x}} \leq n$ , where n denotes the original width of  $\boldsymbol{x}$ . The proposed technique establishes a one-to-one abstraction, i.e.  $\varphi$  holds for the original design if and only if  $\varphi$  holds for the reduced model. False-negatives cannot occur.

Design and abstract model differ from each other only as far as signal widths are concerned. Each  $m_x$  is the minimum number of bits for x which is necessary and sufficient in order to establish a one-to-one abstraction for  $\varphi$  and a reduced model of the abovementioned type. The width of each signal in the abstract RTL model is minimal with respect to the design, the property  $\varphi$ , and the abstraction technique we propose (i.e. by solely changing signal widths).

Furthermore, a post-processing of counterexamples is provided. If  $\varphi$  does not hold for the abstract RTL, and if a verification tool returns a counterexample in terms of value assignments to its input signals, then a counterexample for the original circuit is computed. The verification task itself is completely carried out on the scaled-down version of the design. If the property fails, then counterexamples for the original design are computed from counterexamples found on the reduced model (again see Chapter 2). The proposed method also strictly separates the pre-/postprocessing of design and counterexample and the property checking process itself. Thus, the approach is independent of the concrete realization of the property checker and can be combined with a variety of property checking techniques and can easily be integrated into existing verification flows. Moreover, if preprocessing yields that no reduction is possible for a given design and a property, then abstract model and original design are identical. Thus, the verification task itself is not impaired by using the proposed abstraction.

Linear signal width reductions result in exponentially smaller state spaces. A linear reduction of a signal's width from n bits down to m bits, m < n, causes an exponential reduction of the size of the induced state space from  $2^n$  down to  $2^m$ . Hence, the proposed abstraction to a great extent can have influence on the runtimes of verification tools and can significantly speed up verification. Furthermore, state space reductions allow larger design sizes to be verified. Experimental results on large industrial circuits have demonstrated the applicability and efficiency of the proposed method (see Chapter 10).

### 1.3 Annotated Table of Contents

The primary concern of this thesis is not hardware, but the proposal and formalization of a new verification methodology which automatically scales data path widths. Only very little knowledge about hardware is required as this work is not concerned with computer architecture on transistor level. Hardware is only considered at the behavioral level, and verification is always understood as functional verification. Throughout this thesis, the practical facets of the proposed method are used to motivate and illustrate the presentation of the theoretical aspects of this work. The remainder of this thesis comprises the following chapters:

Chapter 2 introduces the main aspects of Bounded Model Checking of digital circuits and the verification framework which is considered in this thesis. A short overview on high-level verification techniques is given, and the basic idea of signal width reductions is motivated. Furthermore, it is explained how the proposed abstraction technique is incorporated into existing standard BMC flows.

**Chapter 3** gives a detailed introduction to the theory of fixed-size bitvectors and bitvector functions which form the mathematical background of the proposed abstraction technique. As a central item, the notion of *bitwise bitvector functions* is defined.

Chapter 4 introduces the formal satisfiability problem BvSAT for bitvector functions and bitvector disequalities. The central aspect, how satisfiability of instances of BvSAT problems is related to the width of the bitvector domains, is investigated in detail. A one-to-one correspondence with respect to satisfiability of bitwise BvSAT problems of different widths is pinpointed, and the fundamental theorems on width reductions are presented.

Chapter 5 defines bitvector terms and systems of bitvector equations, which provide a textual representation of bitvector functions and BvSAT problems. Systems of bitvector equations are used to represent the control flow and data flow of digital circuits and Bounded Model Checking problems on word-level.

Chapters 6, 7, 8 and 9 contain the computational details of the proposed abstraction technique. It is explained how satisfiability of a system of bitvector equations is reduced to satisfiability of a collection of BvSAT problems by syntactical analysis of the bitvector terms, and it is shown how the theoretical results on width reduction of Chapter 4 are applied to compute a modified system of bitvector equations which is equivalent (with respect to satisfiability) to the initial system and which represents a scaled RTL version of the original property checking problem. Chapter 8 in detail presents the most crucial aspect of the proposed abstraction technique, consisting of a separate handling of structural and dynamic data dependencies. This separation

greatly improves the reduction results and the amount of scaling that can be achieved. It is the reason why the proposed abstraction can effectually be applied to large real world circuit designs and Bounded Model Checking problems.

Chapter 10 contains case studies and experimental results which have been achieved on industrial chip designs and which document the successful practical application of the proposed method.

Chapter 11 concludes the thesis and considers some future directions of research.

# Chapter 2

# High-Level Property Checking of Digital Hardware

This chapter provides a detailed introduction to the hardware verification process and to the property checking framework which is considered in this thesis. It shall provide guidance and motivate the remaining chapters. The formal concepts of Bounded Model Checking and automated data path scaling are presented, and the idea of using high-level information to simplify verification is motivated.

## 2.1 Bounded Model Checking

The problem of verifying that digital circuit behavior is in accordance with the intention of the circuit designer is a problem of checking whether design behavior meets specific properties. The behavior of digital circuit designs is described by the variation of the values of input, output and internal signals over a period of time. Circuits which do not contain any data-storing components (such as registers, latches or memories) are called *combinational circuits*. Otherwise, they are called *sequential circuits*.

For functional simulation and verification, a discrete and linear model of time is used. Time is modeled as an infinite countable sequence of discrete points  $t \in \mathbb{N}$  of time which represent the values of a global clock by which the timing of a circuit is determined. The period between two points of time t and t+1 is called a *clock cycle*. The input-output behavior of sequential digital circuit designs is formally described by *Mealy automata*. A Mealy automaton is a deterministic finite state-machine M = (S, I, O, f, g) with a finite set S of states, a finite alphabet I of input values, a finite set O of output values, a state-transition function  $f: I \times S \longrightarrow S$  and an output function  $g: I \times S \longrightarrow O$ .

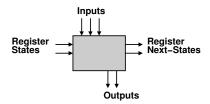

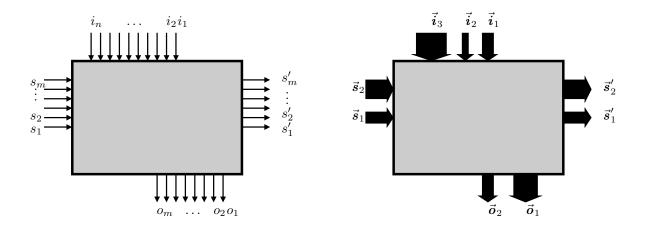

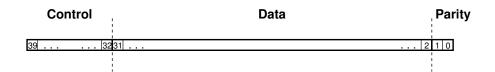

In this thesis, a circuit design is characterized by a finite collection  $\vec{i} = \langle i_1, \dots, i_n \rangle$  of input signals, a finite collection  $\vec{o} = \langle o_1, \dots, o_m \rangle$  of output signals, and a finite collection  $\vec{s} = \langle s_1, \dots, s_p \rangle$  of state signals (or registers), where  $i_1, \dots, i_n, o_1, \dots, o_m$  and  $s_1, \dots, s_p$  are bit-valued variables modeling the bits of the circuit signals. The sets of input values, output values, and of states

are then given by  $I=\{0,1\}^n,\ O=\{0,1\}^m$  and  $S=\{0,1\}^p$ , and the functional behavior of the circuit is given by two vector-valued Boolean functions f and g which characterize state-transitions and output-values of the design for a single clock cycle. If  $\vec{i}(t)=\langle i_1^t,\ldots,i_n^t\rangle$  are the values of the input signals at some point of time t, and  $\vec{s}(t)=\langle s_1^t,\ldots,s_p^t\rangle$  are the states of the circuit registers at t, then the values  $\vec{o}(t)=\langle o_1^t,\ldots,o_m^t\rangle$  of the output signals at t are given by

$$\vec{o}(t) = f(\vec{i}(t), \vec{s}(t)) \tag{2.1}$$

The next state values  $\vec{s'}(t) = \langle s'_1^t, \dots, s'_p^t \rangle$  of the registers at the end of the clock cycle are determined by

$$\vec{s'}(t) = g(\vec{i}(t), \vec{s}(t))$$

(2.2)

The state space for all signals as a whole is finite; the collections  $\vec{i}$ ,  $\vec{o}$ ,  $\vec{s}$  of Boolean variables and the two functions f, g are sufficient to completely specify the sequential functional behavior of the design. Figure 2.1 gives a schematic illustration of a functional circuit specification.

Figure 2.1: Functional Circuit Specification

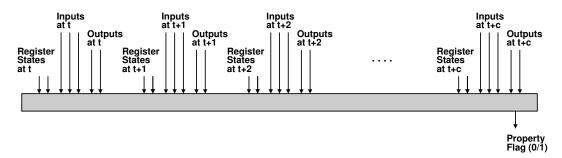

A bounded temporal property defines an intended behavior of a design within a finite bounded interval of time [t, t + c]. A bounded temporal property can be specified by a propositional formula

$$\varphi(\vec{i}(t), \vec{o}(t), \vec{s}(t), \dots, \vec{i}(t+c), \vec{o}(t+c), \vec{s}(t+c))$$

(2.3)

over variables  $\vec{i}(t), \vec{o}(t), \vec{s}(t), \dots, \vec{i}(t+c), \vec{o}(t+c), \vec{s}(t+c)$  for the sequence of the circuit input, output and state signals for all clock cycles of the considered window of time, where  $c \in \mathbb{N}_+$  is a constant and t is a free variable. Its semantics is given by a Boolean function

$$h_{\varphi}: (\{0,1\}^n \times \{0,1\}^m \times \{0,1\}^p)^{c+1} \longrightarrow \{0,1\}$$

(2.4)

If  $h_{\varphi}$  evaluates to true, then we say that the property holds for the regarded sequence of valuations of  $\vec{i}$ ,  $\vec{o}$  and  $\vec{s}$  at  $t, t+1, t+2, \ldots, t+c$ , otherwise  $\varphi$  is said to fail. A schematic view of bounded temporal properties is given in Figure 2.2.

Figure 2.2: Bounded Temporal Property

Properties for Bounded Model Checking of digital circuits are usually specified in formal languages which describe propositional linear time logics over finite bounded intervals of time, similar to formulae used in *symbolic trajectory evaluation* (see e.g. [SHS97]). Such languages consist of bounded temporal operators and state expressions which can be augmented with time points and specify relationships among the values of registers, input and output signals. In practice, properties are often subdivided into an assumption part implying a commitment part:

$$Property \equiv Assumptions \Longrightarrow Commitments$$

As a typical example consider:

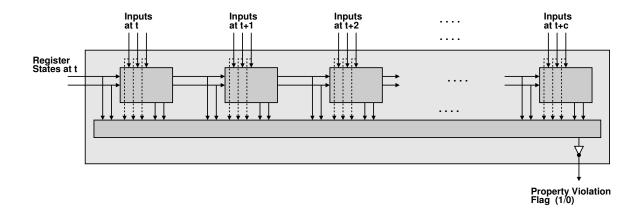

Hardware development is an error-prone process. It is likely that design specifications are not completely met by early implementations. Bounded Model Checking is intended to be applied already in early design stages in order to detect design errors as soon as possible. Instead of trying to validate a property  $\varphi$ , BMC performs a check for faulty behavior of a given design D (falsification of  $\varphi$ ). Of interest is whether there exists a situation which contradicts  $\varphi$ , i.e. a sequence of values for all circuit signals of D for each clock-cycle of [t,t+c] for which  $h_{\varphi}$  evaluates to false. The functional behavior of D within the window of time which is specified by  $\varphi$  depends on the sequence of values  $\vec{i}(t), \vec{i}(t+1), \vec{i}(t+2), \ldots, \vec{i}(t+c)$  of the input signals, on the initial values  $\vec{s}(t)$  of the states at the beginning of the time frame, and on the output function f and the state-transition function f of f and the state-transition function f of f and the state of circuit input, output and state signals describes a behavior of f if equations (2.1) and (2.2) and the next state relation

$$\vec{s}(t+1) = \vec{s'}(t) \tag{2.5}$$

hold for all clock cycles of [t, t+c]. This concept is called *unrolling* of the design and corresponds to creating separate instances  $D_0, \ldots, D_c$  of the design D, one for each clock cycle, and then linking state and next state signals according to (2.5).

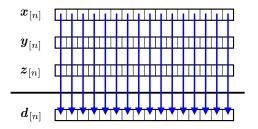

The initial property checking problem considers *sequential* design behavior. By unrolling the design it is turned into a problem for a *combinational* circuit. Compare Figures 2.1 and 2.3 for a visualization.

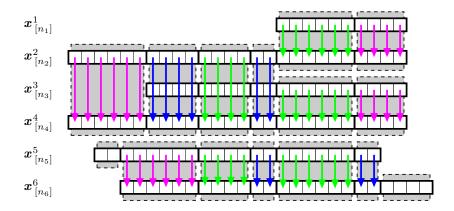

Figure 2.3: Unrolling

Whether or not the property  $\varphi$  holds for D can be determined by substituting the design specifications f and g into the negation of formula (2.3) according to equations (2.1), (2.2) and (2.5) for each clock cycle t+i within the specified interval of time. The result is a propositional formula  $\hat{\varphi}(\vec{i}(t), \vec{i}(t+1), \dots, \vec{i}(t+c), \vec{s}(t))$  in which only the state signals for the very first clock cycle and all input signals are free variables. The semantics of  $\hat{\varphi}$  is then given by the Boolean function

$$h_{\hat{\varphi}} : (\{0,1\}^n)^{c+1} \times \{0,1\}^p \longrightarrow \{0,1\}$$

(2.6)

which is defined by

The formula  $\hat{\varphi}$  is unsatisfiable if for all bounded windows of time of length c and for initial states  $\vec{s}(t)$  and all input sequences  $\vec{i}(t), \ldots, \vec{i}(t+c)$  the property  $\varphi$  holds for the design. If  $\hat{\varphi}$  is satisfiable, then this is an indication that the circuit does not function in the way intended by the designer. Satisfiability of  $\hat{\varphi}$  corresponds to a violation of the property:

$$\hat{\varphi}$$

is satisfiable  $\iff$  property  $\varphi$  does not hold for design  $D$  (2.7)

A satisfying solution of  $\hat{\varphi}$  yields value assignments for the state registers in the initial clock cycle t and a sequence of value assignments for all input signals in the clock cycles t to t+c. For this initial state  $\vec{s}(t)$  and the input sequence  $\vec{i}(t), \vec{i}(t+1), \vec{i}(t+2), \ldots, \vec{i}(t+c)$  a violation of the

property occurs. A satisfying solution of  $\hat{\varphi}$  is called a *counterexample* for  $\varphi$  and D, and we say that property  $\varphi$  holds for D if  $\hat{\varphi}$  is unsatisfiable. The question, whether or not  $\hat{\varphi}$  is satisfiable, is called a *Bounded Model Checking Problem* (see [BCC<sup>+</sup>99, BCCZ99, BCRZ01]). The schematic relationship between design, property, unrolling and the Bounded Model Checking problem is shown in Figure 2.4.

Figure 2.4: Bounded Model Checking Problem

Falsification is the preferred technique to find design errors as fast and as early as possible. Counterexamples yield assignments of values to the circuit inputs for which a violation of the desired behavior, which is described by the property, can be observed. Circuit designers use counterexamples for error-location and design debugging. If no counterexample exists, then the property holds for the design:

design

$$D$$

has property  $\varphi \iff \hat{\varphi}$  is unsatisfiable (2.8)

On the technical side, there are two main approaches to checking satisfiability of  $\hat{\varphi}$  in Bounded Model Checking. In general, BDD techniques tend to prove unsatisfiability of  $\hat{\varphi}$  more efficiently than SAT based techniques. Unsatisfiability corresponds to functional equivalence of  $\hat{\varphi}$  with a constant false. In contrast to that, SAT solvers employ guided-search (see [Stå95, DP60]) and pruned search-space techniques and are better suited for quickly finding satisfying solutions of  $\hat{\varphi}$  (see [BCCZ99, CFF<sup>+</sup>01, Sht00, Sht01]). Some prominent SAT solvers are, for example, Chaff (see [MMM+01]), SATO (see [Zha97]), Relsat (see [BS97]) and GRASP (see [Sil95, SS96, SS99]). Another successful technique for quickly finding satisfying solutions is Automatic Test Pattern Generation (ATPG), which is closely related to SAT techniques (see e.g. [HC00, Lar92, Che91, GAK99, CGPR90, BRTF99, SS97). The majority of today's industrial hardware verification tools for Bounded Model Checking rely on multi-engine concepts of SAT, ATPG and BDD based techniques and try to partition the BMC problem in a divide-and-conquer approach into smaller problems. Based on heuristics, these smaller instances then are either split up again or tackled by BDD and SAT procedures. Computational limits depend on a tradeoff between circuit complexity, complexity of the logic of the properties, and the number of clock cycles specified in the property.

## 2.2 The Property Checking Framework

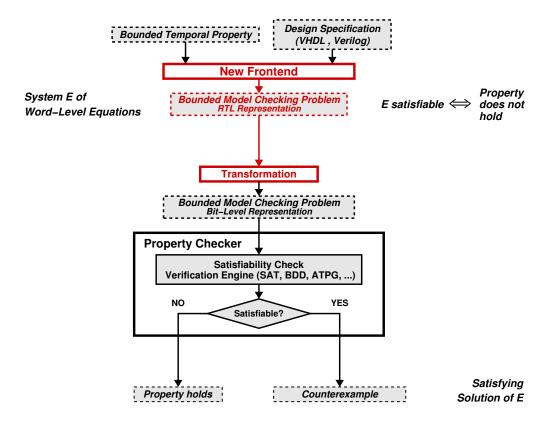

The Bounded Model Checking framework which is considered in this thesis is illustrated in Figure 2.5 and is characterized as follows.

Figure 2.5: Property Checking Flow

Initially, the formal specification of a bounded temporal property and the HDL source code of a circuit design are read by a frontend which generates a bit-level representation of the corresponding Bounded Model Checking problem. The bit-level representation is then handed to a property checker, which determines satisfiability of the Bounded Model Checking problem and either, if the Bounded Model Checking problem is not satisfiable, confirms that the property holds, or, if the Bounded Model Checking problem is satisfiable, presents a counterexample in terms of value-assignments to the input signals of the design. The counterexample is generated from the satisfying solution that has been found and indicates a violation of the property.

## 2.3 Utilizing High-Level Information for Verification

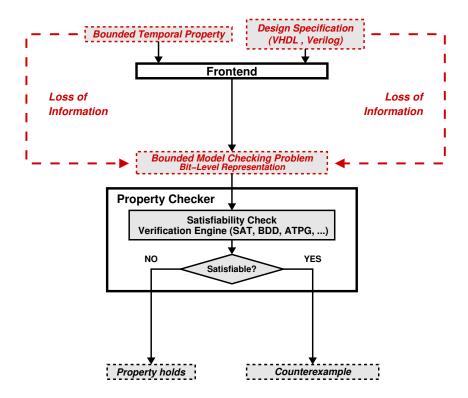

Deciding satisfiability of Boolean formulae is known to be an NP-complete problem and has been well investigated. A variety of decision procedures has been proposed, and especially SAT procedures (see e.g. [Sil95]) have shown to be particularly useful in Bounded Model Checking (see also [SS00]). However, these procedures operate on bit-level. The problem, whether or

not a specific property holds for a circuit design, is solved in the Boolean domain. This means that all variables occurring in the Bounded Model Checking problem are Boolean variables. Each variable corresponds to a specific bit of one of the circuit signals. Yet, circuit designs are usually given in terms of RTL specifications, and RTL specifications contain explicit structural high-level information which is not contained in the Bounded Model Checking problem anymore and thus cannot be used in the satisfiability checks. The standard property checking flow thus includes a natural loss of structural information.

Figure 2.6: Word-Level Information vs. Bit-Level Information

Hardware description languages offer word-level data structures (e.g. multi-bit signals, arrays, memories) as well as high-level operators to describe circuit functionality on RT-Level. Many circuit designs have very regular structures that can easily be described on this level of abstraction. To give an example, consider addition of two 2-bit signals  $\mathbf{x}_{[2]} = \langle x_1, x_0 \rangle$ ,  $\mathbf{y}_{[2]} = \langle y_1, y_0 \rangle$ , and a 1-bit carry-in  $\mathbf{c}_{[1]} = \langle c_0 \rangle$ . Sample bit-level equations describing the data path dependencies for the result signal  $\mathbf{z}_{[2]} = \langle z_1, z_0 \rangle$  are:

$$z_{0} = ((x_{0}\overline{y_{0}} \vee \overline{x_{0}}y_{0}) \wedge \overline{c_{0}}) \vee ((x_{0}y_{0} \vee \overline{x_{0}y_{0}}) \wedge c_{0})$$

$$c_{1} = x_{0}y_{0} \vee y_{0}c_{0} \vee c_{0}x_{0}$$

$$z_{1} = ((x_{1}\overline{y_{1}} \vee \overline{x_{1}}y_{1}) \wedge \overline{c_{1}}) \vee ((x_{1}y_{1} \vee \overline{x_{0}y_{1}}) \wedge c_{1})$$

$$c_{2} = x_{1}y_{1} \vee y_{1}c_{1} \vee c_{1}x_{1}$$

$$(2.9)$$

The connotation that, for example,  $x_1$  and  $x_0$  resemble a 2-bit signal, is not visible on bit-level and thus not visible to a bit-level satisfiability checker. Furthermore, it is rather difficult to

conclude from (2.9) that a 2-bit adder is represented. Contrasting that, 2-bit addition can easily be described on word-level by a single bitvector equation:

$$z_{[2]} = x_{[2]} + y_{[2]} + c_{[1]}$$

(2.10)

Such a representation allows special high-level decision procedures (here for high-level arithmetics, see e.g. [CZ95]) to be evoked by a verification tool. Several approaches to formal circuit verification are known which are based on word-level formalisms and which make use of RTL information. A selection of the most important ones is briefly surveyed in the following sections (see also [JD02b]). Several explanatory examples are given which illustrate that RTL and bit-level contain different levels of structural information and which motivate how additional word-level information can be used in order to simplify verification tasks for digital hardware.

### 2.3.1 Integer Linear Programming

One approach to RTL based verification is to treat arithmetic units by Integer Linear Programming (ILP) methods (see e.g. [ZKCR01, FDK98, BD02]). Word-level arithmetic is transformed into a linear program, i.e. a collection of arithmetic equations and inequalities over integer valued variables.

Linear programs are solved in the integer domain by ILP solvers. Equation (2.10), for example, can be transformed into the following ILP (note that solutions of Equation (2.11) and Equation (2.10) have a one-to-one correspondence):

$$D = x + y + c$$

$$D = 4 \cdot d + z$$

$$0 \le x < 4$$

$$0 \le y < 4$$

$$0 \le c < 2$$

$$0 \le z < 4$$

$$0 \le d$$

$$0 < D$$

$$(2.11)$$

Integer Linear Programming is suitable for data path verification of arithmetic circuits but lacks adequate modeling of the control path. Another drawback is that efficient ILP solvers often restrict integers and thus data path signals to be words of fixed, machinery-dependent width, e.g. 32 bits. Furthermore, bit-level addition and multiplication of n-bit signals in digital circuit corresponds to modulo-arithmetic in the ring  $\mathbb{Z}_n$  and requires caution when generating the ILP (cf. [ZKC01]). In the example given above, the second equation and all the inequalities are used to model modulo-arithmetic on 2-bit bitvectors.

#### 2.3.2 Rewriting

Term-rewriting techniques (see e.g. [BN98, DJ90]) can be used to simplify verification tasks. RTL rewriting can utilize high-level information on operators, which is not present on bit-level.

Let  $m{x}_{[2]}, m{y}_{[2]}$  and  $m{z}_{[2]}$  be signals of 2-bit width, and consider checking if the following equation

$$(\boldsymbol{x}_{[2]} + \boldsymbol{y}_{[2]}) + \boldsymbol{z}_{[2]} = \boldsymbol{y}_{[2]} + (\boldsymbol{z}_{[2]} + \boldsymbol{x}_{[2]})$$

(2.12)

is satisfiable. Due to associativity and symmetry of addition, the left and right side of Equation (2.12) can be rewritten to

$$x_{[2]} + y_{[2]} + z_{[2]} = x_{[2]} + y_{[2]} + z_{[2]}$$

(2.13)

and easily be recognized as a tautology. However, a sample bit-level representation of (2.12) is

$$a_{0} = (x_{0}\overline{y_{0}} \vee \overline{x_{0}}y_{0})$$

$$c_{00} = x_{0}y_{0}$$

$$a_{1} = ((x_{1}\overline{y_{1}} \vee \overline{x_{1}}y_{1}) \wedge \overline{c_{00}}) \vee ((x_{1}y_{1} \vee \overline{x_{1}}y_{1}) \wedge c_{00})$$

$$c_{01} = x_{1}y_{1} \vee y_{1}c_{00} \vee c_{00}x_{0}$$

$$b_{0} = ((z_{0}\overline{a_{0}} \vee \overline{z_{0}}a_{0}) \wedge \overline{c_{01}}) \vee ((z_{0}a_{0} \vee \overline{z_{0}}a_{0}) \wedge c_{01})$$

$$c_{10} = z_{0}a_{0} \vee a_{0}c_{01} \vee c_{01}z_{0}$$

$$b_{1} = ((z_{1}\overline{a_{1}} \vee \overline{z_{1}}a_{1}) \wedge \overline{c_{10}}) \vee ((z_{1}a_{1} \vee \overline{z_{1}}a_{1}) \wedge c_{10})$$

$$d_{0} = (z_{0}\overline{x_{0}} \vee \overline{z_{0}}x_{0})$$

$$e_{00} = z_{0}x_{0}$$

$$d_{1} = ((z_{1}\overline{x_{1}} \vee \overline{z_{1}}x_{1}) \wedge \overline{e_{00}}) \vee ((z_{1}x_{1} \vee \overline{z_{1}}x_{1}) \wedge e_{00})$$

$$e_{01} = z_{1}x_{1} \vee x_{1}e_{00} \vee e_{00}z_{0}$$

$$f_{0} = ((y_{0}\overline{d_{0}} \vee \overline{y_{0}}d_{0}) \wedge \overline{e_{01}}) \vee ((y_{0}d_{0} \vee \overline{y_{0}}\overline{d_{0}}) \wedge e_{01})$$

$$e_{10} = y_{0}d_{0} \vee d_{0}e_{01} \vee e_{01}y_{0}$$

$$f_{1} = ((y_{1}\overline{d_{1}} \vee \overline{y_{1}}d_{1}) \wedge \overline{e_{10}}) \vee ((y_{1}d_{1} \vee \overline{y_{1}}\overline{d_{1}}) \wedge e_{10})$$

$$b_{0} = f_{0}$$

$$b_{1} = f_{1}$$

introducing auxiliary variables for carry bits and for temporary results of the additions. Syntactically deducing equality of  $\langle b_1, b_0 \rangle$  and  $\langle f_1, f_0 \rangle$  from (2.14) is far from being easy. Term rewriting techniques are, for example, applied in proof systems which automatically deduce equality of terms, and in preprocessors which simplify high-level expressions before other high-level verification techniques are applied.

### 2.3.3 Symmetry Reductions

Another approach to exploit regular structures of high-level operators is to restrict the sizes of signal domains by symmetry reduction. Symmetries, for instance, occur when operator arguments are commutable. As an example, consider addition of 16-bit signals:

$$x_{[16]} + y_{[16]} = z_{[16]}$$

(2.15)

Both signals  $\boldsymbol{x}_{[16]}$  and  $\boldsymbol{y}_{[16]}$  are used symmetrically with respect to addition. Here, without loss of generality, it is possible to assume  $\boldsymbol{x}_{[16]} \leq \boldsymbol{y}_{[16]}$ , because a satisfying solution of Equation (2.15) exists if and only if a satisfying solution exists which additionally satisfies  $\boldsymbol{x}_{[16]} \leq \boldsymbol{y}_{[16]}$ . Such

additional constraint on  $\boldsymbol{x}_{[16]}$  and  $\boldsymbol{y}_{[16]}$  can help to significantly decrease the size of search spaces in guided-search algorithms (cf. [Sil95]) as employed in most SAT procedures. Obviously, it is impossible to automatically deduce such constraints from bit-level representations like (2.14). For further details on symmetry reductions see e.g. [CEJS98, ET99, Bri01, CGLR96, ID93, CFJ93].

### 2.3.4 Word-Level Decision Diagrams

For representation and manipulation of Boolean functions, Binary Decision Diagrams (BDDs) have been proposed (see e.g. [Bry86, Bry92, Bry95]) and are used successfully in many industrial verification tools. Several extensions of BDDs to the word-level have been suggested. These approaches are based on Word-Level Decision Diagrams (WLDDs), which are graph-based representations of functions that allow for the representation of functions with a Boolean range and an integer domain (see e.g. [BC94, AH97, DBR97, HD98, HD99, Dre00, WAH01, CKRZ01]). WLDDs have received a lot of attention, since based on these data structures for the first time large arithmetic circuits, including multipliers, have been formally verified. But, in contrast to BDDs, the manipulation algorithms can be more expensive and often have exponential worst-case behavior.

### 2.3.5 Abstraction

Abstraction techniques (cf. e.g. [CGL92]) implement the following general approach. Instead of directly solving a given verification problem P, a smaller or simpler instance  $P' := \mathcal{T}(P)$  is computed in which information that is not relevant for solving the verification problem is abstracted and which is then solved by conventional methods. Depending on the degree of reduction or simplification between P and P', solving P' can possibly be done faster and might require significantly less resources. It has to be ensured that computing P' from P preserves certain criteria as far as solvability is concerned. In this context, an abstraction technique  $\mathcal{T}$  is said to be one-to-one if, for all problem instances P, solvability of  $P' := \mathcal{T}(P)$  is related to solvability of P in a one-to-one fashion, i.e. if the abstract problem is solvable if and only if the original problem is solvable. Since we consider satisfiability problems, we have:

$$\mathcal{T}$$

is a one-to-one abstraction: (  $P'$  satisfiable  $\iff P$  satisfiable )

If the domains of abstract and original problem differ, then abstractions usually provide an additional transformation  $\tau$  which computes solutions of the original problem from solutions found on the abstract problem instance, i.e. if s is a satisfying solution of  $P' := \mathcal{T}(P)$ , then  $\tau(s)$  yields a satisfying solution of P. Thus, solving the original problem can completely and efficiently be replaced by solving the abstract problem instance, provided that the total amount of time for computing the abstract instance and then solving it is still faster than solving the original problem. For example, conversion of Boolean SAT formulae from CNF to DNF yields a one-to-one abstraction with respect to satisfiability. As far as complexity is concerned, deciding satisfiability of CNF formulae is NP-complete, whereas satisfiability of DNF formulae can be determined in polynomial time. However, whether there exists an efficient computation of the abstraction itself, is still an open problem which is equivalent to the P=NP problem.

If an abstraction is not one-to-one, then for each solution s found for P', an additional consistency check has to be performed which inspects if  $\tau(s)$  indeed is a solution of P or not (a so-called false-negative). Such an abstraction still might be of interest if establishing a one-to-one abstraction is not possible, but finding solutions s of P' and performing the consistency check for  $\tau(s)$  is fast. In such a case, abstraction is usually combined with guided-search techniques on the solution space of P'. For each solution that is found, a consistency check is performed, and the search is continued if this check fails. Yet, the amount of reduction of the problem size achieved by such an abstraction must justify the additional costs for validating solutions found for the abstract problem instance.

One-to-one abstractions are highly attractive in digital hardware verification because reduced or simplified problem instances can significantly increase the performance of existing verification tools. If the abstract problem instance is specified in the same formalism which is used for the original problem, then one-to-one abstractions can easily be embedded in existing verification flows without having to modify the underlying verification techniques. Additionally, abstractions which operate on RT-Level can incorporate and utilize all high-level information which is available in the problem specification.

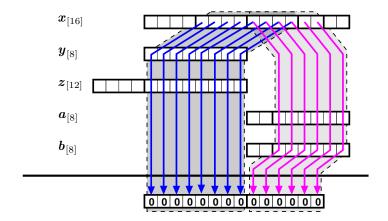

### 2.4 Scaling Down RT-Level Designs

The improvement of formal verification of digital hardware which is contributed by this thesis consists of a high-level one-to-one abstraction technique which is used as a preprocessing step in the hardware verification flow. The proposed method exploits structural high-level design information and absorbs the informational gap between RTL and bit-level by establishing a fully automated scaling of the design.

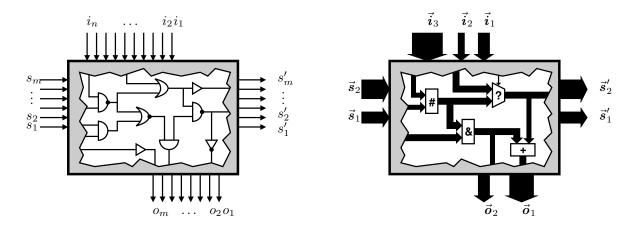

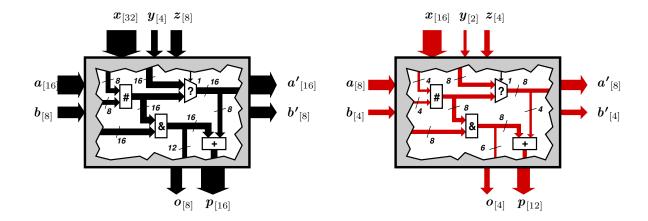

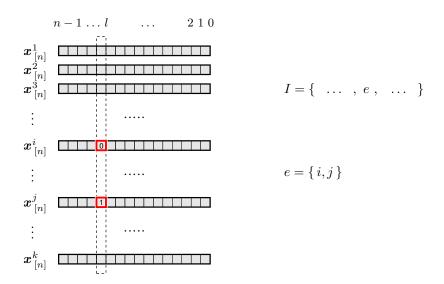

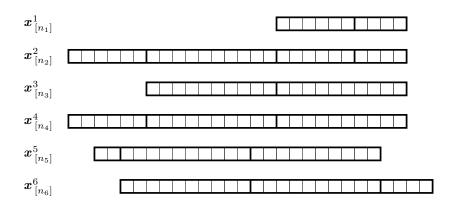

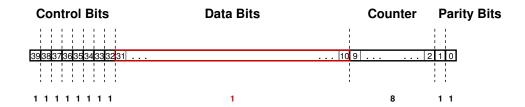

Figure 2.7: Bit-Level Design Specification vs. Word-Level Design Specification

Figure 2.7 demonstrates one of the differences between high-level and bit-level specifications of digital designs. The information which collections of single bits resemble high-level circuit signals is present in RTL specifications, but is lost on bit-level. As a consequence, the specification of

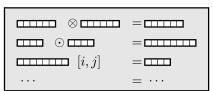

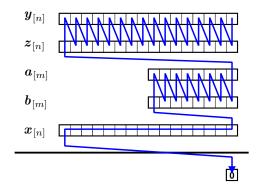

data flow on bit-level lacks this information, too. Data flow can only be specified in terms of single-bit signals and Boolean logic gates, whereas on RT-Level the data paths of a design are characterized by multi-bit busses and high-level operators and modules, as indicated in Figure 2.8.

Figure 2.8: Bit-Level Data Flow vs. Word-Level Data Flow

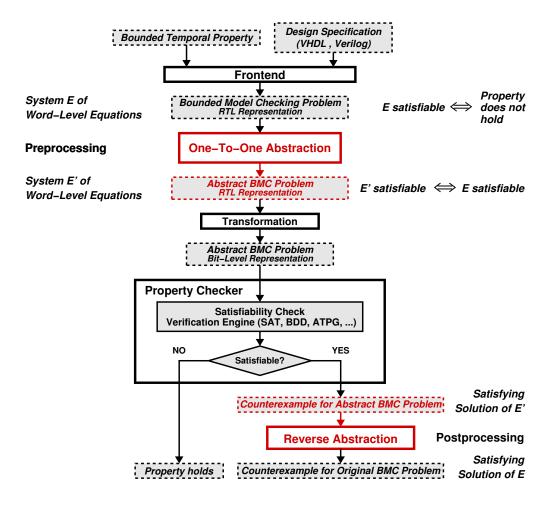

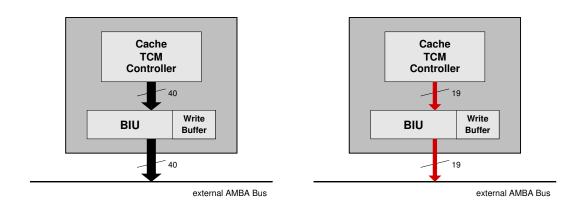

The proposed abstraction technique exploits high-level information on multi-bit signals and high-level information on multi-bit data flow. In order to be able to do so, a prerequisite is to make this type of information available in an intermediate preprocessing stage of the verification flow. Therefore, in a first conceptual step, the conventional frontend is replaced by a new frontend which, instead of a bit-level representation, generates an RTL representation of the Bounded Model Checking problem in which the structural information on high-level data flow is preserved. Then, in a successive step, this RTL representation is further processed and transformed into the traditional bit-level representation, which is then handed to the property checker. The so modified verification flow is shown in Figure 2.9.

Up to this point, high-level information was only contained in the formal specification of the bounded temporal property and in the HDL design specification (cf. again Figure 2.6). Now, this information is combined and made available in a high-level representation of the Bounded Model Checking problem. Note that the loss of information is still inherent in the modified verification flow. It is deferred and now occurs in the newly introduced transformation step.

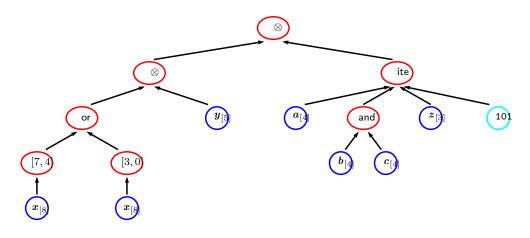

In this thesis, Bounded Model Checking problems are represented on RT-Level by formal systems of bitvector equations. For a given design D and a formal property  $\varphi$  the new frontend synthesizes a system E of bitvector equations such that the corresponding Bounded Model Checking problem  $\hat{\varphi}$  is satisfiable if and only if E is satisfiable, i.e.

$$E$$

is satisfiable  $\iff$  property  $\varphi$  does not hold for design  $D$  (2.16)

Bitvector terms, bitvector equations and systems of bitvector equations are introduced in detail in Chapter 5.

Figure 2.9: Modified Property Checking Flow

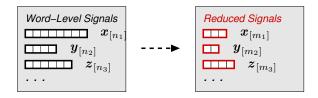

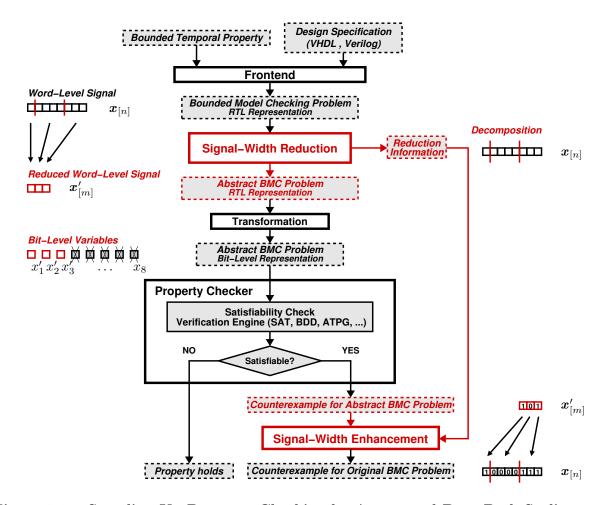

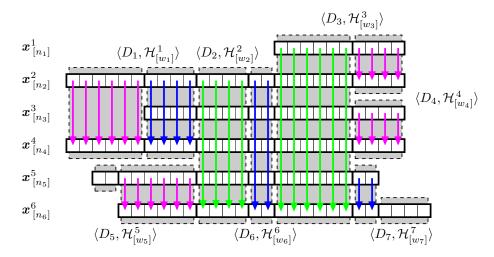

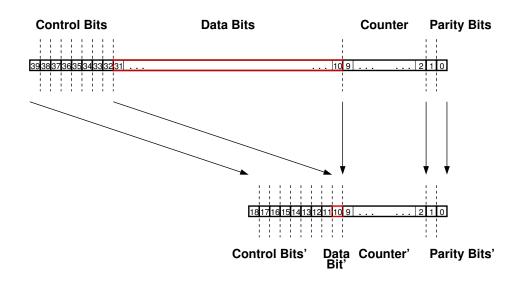

Bitvector variables of E correspond to multi-bit circuit signals of D. Each signal and each bitvector variable  $\boldsymbol{x}$  has a fixed width  $n \in \mathbb{N}_+$  (which usually is annotated as a subscript in square brackets) and takes bitvectors of respective length as values. The later transformation of E into a bit-level representation of the Bounded Model Checking problem generates one bit-level variable for each bit of a bitvector variable. Thus satisfying solutions of E directly correspond to satisfying solutions of  $\hat{\varphi}$  and vice versa, and yield counterexamples for  $\varphi$  and E0 (see Figure 2.9). The proposed abstraction technique establishes a preprocessing step. The system E0 of bitvector equations is taken and analyzed, and a second system E1 is computed which is then used for property checking instead of the original system E1. The system E2 is generated by replacing each word-level signal  $\boldsymbol{x}$  of E1 by a corresponding shrunken signal of width E2 n (where E3 denotes the original width of E3).

Figure 2.10: Basic Abstraction Technique

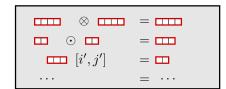

The original system E and the abstract model E' differ from each other only as far as signal widths are concerned. All other data flow aspects, like for example operators or term structure,

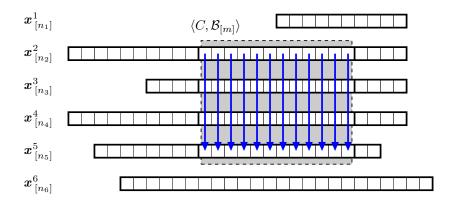

### Word-Level Equations

#### Abstract Word-Level Equations

Figure 2.11: Reducing Systems of Word-Level Equations

are not changed (see Figure 2.11), and the proposed method computes the reduced widths such that satisfiability is strictly preserved, i.e.

$$E \text{ is satisfiable} \iff E' \text{ is satisfiable}$$

(2.17)

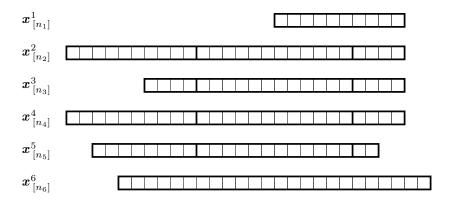

The width of each signal in the abstract model is the minimum width which is necessary and sufficient in order to establish a one-to-one abstraction with respect to design, property, and the proposed reduction (E' differing from E only by reduced variable widths). The reduced system E' then corresponds to a scaled version of the original design D, and scaling is understood in terms of strictly preserving the general data flow of D except for a reduction of the widths of the data paths, as illustrated in Figure 2.12.

Figure 2.12: Original and Scaled Design

The amount of reduction that can be achieved is determined with respect to the circuit property that is to be verified. The scaled version of the design is then used for verification instead of the original one, and (2.17) yields:

the property holds for the original design  $\iff$  the property holds for the scaled design

If the property does not hold, then, considering the modified verification flow, the counterexample which is returned by the property checker is a counterexample for the scaled version of

the design. The abstraction technique which is presented in this thesis adds an additional postprocessing step to the verification flow. In this step, the reduced counterexample is taken and a counterexample for the original design is generated. The proposed reduction technique provides an easy generation of satisfying solutions of E from satisfying solutions of E'. Figure 2.13 illustrates how the proposed abstraction technique is integrated in the verification flow.

Figure 2.13: Property Checking Flow with High-Level Abstraction

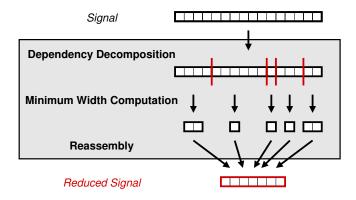

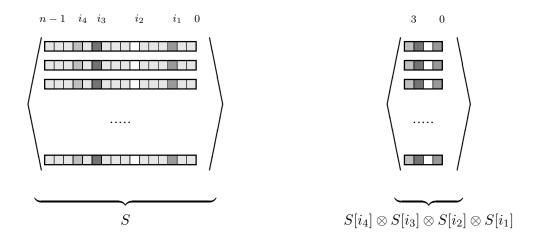

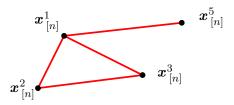

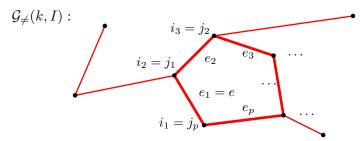

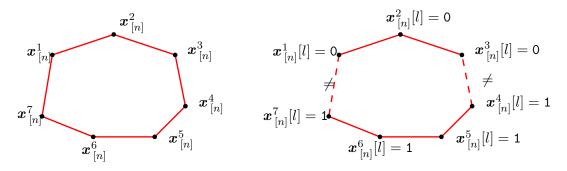

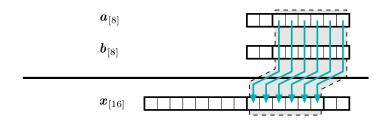

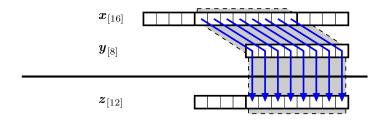

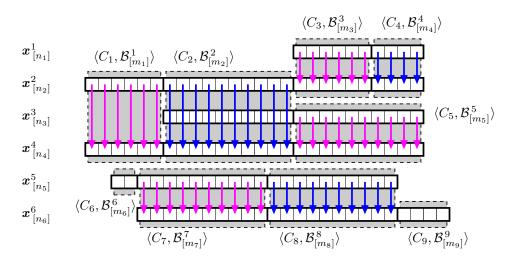

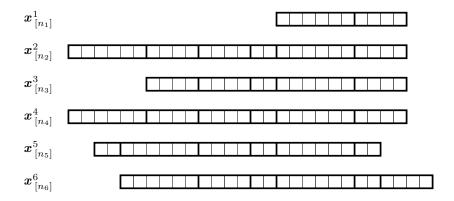

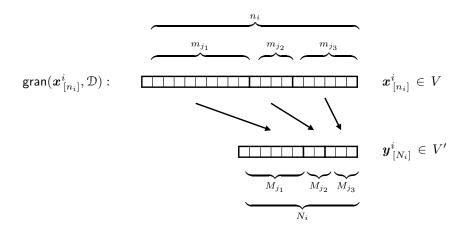

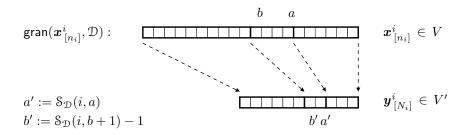

The process of scaling down signal widths is separated into two subsequent phases. First, the coarsest granularity of each word-level signal is computed as determined by the structural data dependencies of E. A granularity is a separation of a signal into several contiguous parts which indicate the coarsest possible subsumptions of individual bits of the signal which are processed on the same data path. Details are given in Chapter 6 (see also Example 2.3). Then, for each such part, the necessary minimum width is computed which guarantees that satisfiability of E and E' correspond to each other in a one-to-one fashion. This will be further explained in Chapter 4. According to these computed minimum widths, the reduced width for the corresponding signal is reassembled. The basic concept of this technique is shown in Figure 2.14 (see also Chapter 9).

Figure 2.14: Signal Width Reduction

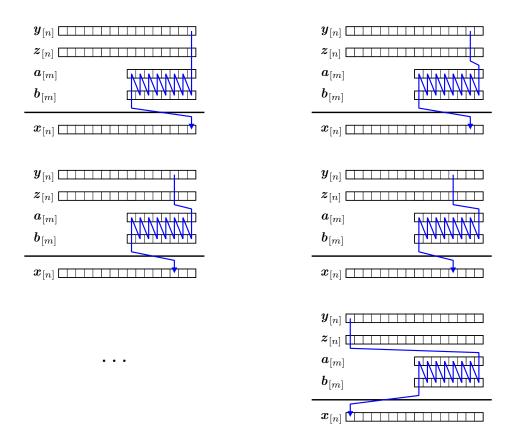

The bit-level representation of the Bounded Model Checking problem which is generated from the RTL representation contains bit-level variables for each bit of each word-level signal. Depending on the degree of reduction of the signal widths during scaling, the bit-level representation can contain significantly less variables when the abstract RTL model is used (see Figure 2.15).

Figure 2.15: Speeding Up Property Checking by Automated Data Path Scaling

The effect is a reduction of the sizes of the Bounded Model Checking problems which have to be handled by the property checker. This aspect coincides with a speed-up of the verification runtimes. Thus, although property checking is still done on bit-level, this verification approach indirectly uses and benefits from high-level information. Another advantage is that no modifications have to be applied to the property checker; the proposed abstraction can easily be integrated into existing flows (see also [JD01, JD02a] for an overview).

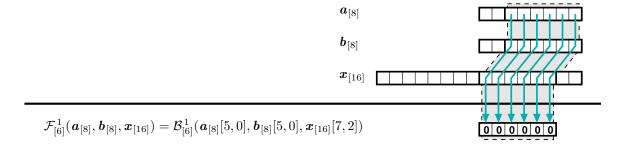

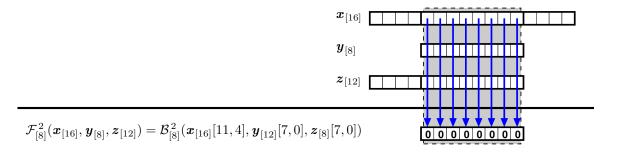

### 2.5 Signal Width Reduction

Systems of bitvector equations can be used to describe data flow and control flow aspects of a digital circuit on word-level (bitvector terms and bitvector equations are formally defined in Chapter 5). Design properties can be verified by checking satisfiability of such equations. The high-level information about which individual bits belong to the same multi-bit high-level signal and the high-level information about how single bits are grouped and ordered within these signals is explicitly contained in the equations. In the following introductory examples the basic idea for using this information to reduce computational complexity of satisfiability checks of bitvector equations is illustrated.

**Example 2.1 (Uniform Data Dependencies)** Determining if bitwise Boolean conjunction of two word-level signals of width 8, denoted by  $\mathbf{x}_{[8]}$  and  $\mathbf{y}_{[8]}$ , can evaluate to the 8-bit zero vector can be done by checking if the following bitvector equation

$$\boldsymbol{x}_{[8]}$$

and  $\boldsymbol{y}_{[8]}$  = 00000000 (2.18)

is satisfiable, where and denotes bitwise Boolean conjunction. Equation (2.18) specifies functional data dependencies between  $\boldsymbol{x}_{[8]}$  and  $\boldsymbol{y}_{[8]}$ , and satisfiability of (2.18) is characterized by satisfiability of the following corresponding bit-level formula

$$(x_0 \text{ and } y_0 = 0) \land (x_1 \text{ and } y_1 = 0) \land \dots \land (x_7 \text{ and } y_7 = 0)$$

(2.19)

involving 16 Boolean variables and 8 bit-level equations. Obviously, it is not necessary to solve all 8 equations of (2.19) separately because bit-positions 0-7 of  $\boldsymbol{x}_{[8]}$  and  $\boldsymbol{y}_{[8]}$  are treated uniformly, i.e. the data dependencies for  $x_0, y_0$  to  $x_7, y_7$  are the same except for index numbering. Let  $\boldsymbol{x'}_{[1]}$  and  $\boldsymbol{y'}_{[1]}$  denote two new word-level signals of width 1, derived from the variables of (2.18). It is sufficient to check if

$$\boldsymbol{x'}_{[1]}$$

and  $\boldsymbol{y'}_{[1]} = 0$  (2.20)

is satisfiable as (2.18) is satisfiable if and only if (2.20) is satisfiable. Furthermore, a satisfying solution of (2.18) can be obtained from a satisfying solution of (2.20) by copying the values of  $\mathbf{x'}_{[1]}$  and  $\mathbf{y'}_{[1]}$  into all bit positions of the corresponding signals of (2.18). For example,  $\mathbf{x'}_{[1]} = 0$  and  $\mathbf{y'}_{[1]} = 1$  yields  $\mathbf{x}_{[8]} = 00000000$  and  $\mathbf{y}_{[8]} = 111111111$ .

In Example 2.1, both signals  $x_{[8]}$  and  $y_{[8]}$  have uniform data dependencies and can be reduced to a width of one bit. Uniform data dependencies are formally introduced in Section 3.4 and form the basis of the width reduction technique, as explained in Chapter 4. In general, the possible amount of reduction depends on structural and dynamical data dependencies as well, and the data flow of a signal must be analyzed for all equations of a given system of bitvector equations. Reduction depends on the data dependencies imposed by the conjunction of all equations. Thus, even if uniform data flow exists for specific signals in one equation, other equations can be the reason that reduction to only 1-bit width might not preserve satisfiability in a one-to-one fashion.

Example 2.2 (Dynamical Data Dependencies) Let  $x_{[8]}$ ,  $y_{[8]}$  and  $z_{[8]}$  be signals of 8-bit width for which uniform data dependencies exist. Consider a system of bitvector equations which additionally contains equations involving the following expressions:

A satisfying solution of (2.21) might only exist if the values of  $x_{[8]}, y_{[8]}, z_{[8]}$  are mutually different, i.e.

$$x_{[8]} \neq y_{[8]} \land y_{[8]} \neq z_{[8]} \land z_{[8]} \neq x_{[8]}.$$

(2.22)

Then, reduction to only one bit width is not possible, because

$$x'_{[1]} \neq y'_{[1]} \land y'_{[1]} \neq z'_{[1]} \land z'_{[1]} \neq x'_{[1]}$$

(2.23)

is not satisfiable, while (2.22) is. Instead the following holds:

$$x_{[m]} \neq y_{[m]} \land y_{[m]} \neq z_{[m]} \land z_{[m]} \neq x_{[m]}$$

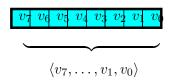

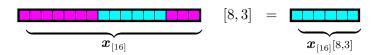

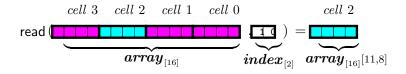

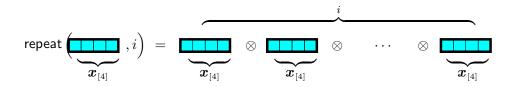

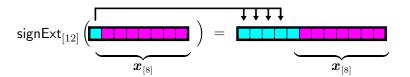

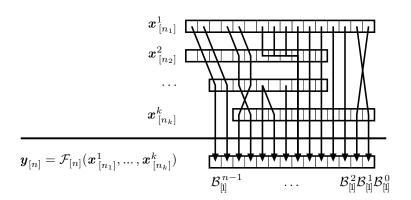

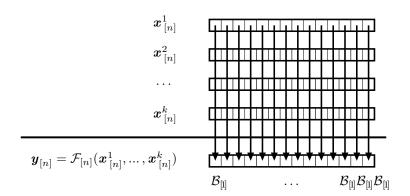

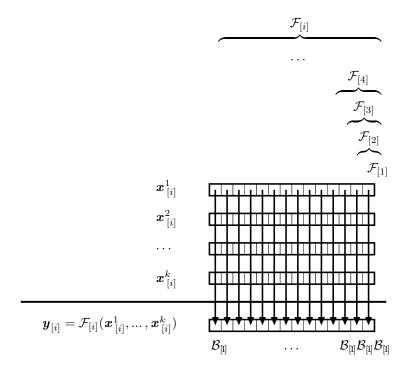

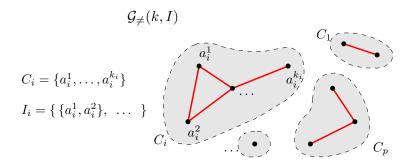

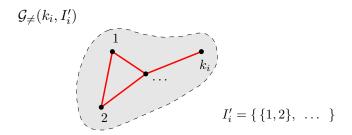

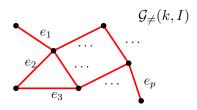

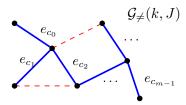

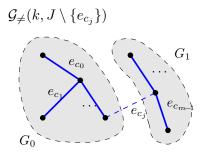

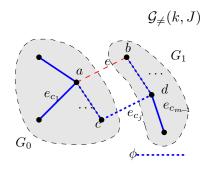

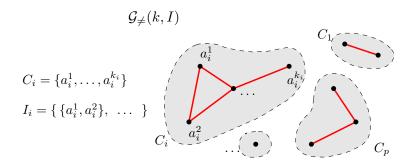

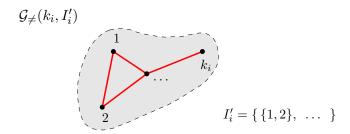

(2.24)