# Entwicklung von neuen Algorithmen der Computerarithmetik in Hinsicht auf ihre Nutzung in der Kryptographie

#### Dissertation

zur Erlangung des akademischen Grades

Doktor der Naturwissenschaften

(Dr. rer. nat.)

der Technischen Fakultät

der Christian-Albrechts-Universität zu Kiel

Viktor Bunimov

Kiel 2005

1. Gutachter Prof. Dr. rer. nat. Manfred Schimmler

2. Gutachter Prof. Dr. Thomas Wilke

3. Gutachter Prof. Dr.-Ing. Christof Paar

Datum der mündlichen Prüfung 7.12.05

#### **Zusammenfassung:**

In dieser Arbeit wird eine Reihe neuer Algorithmen aus dem Bereich der ganzzahligen Langzahlcomputerarithmetik für die Anwendungen vor allem aus dem Bereich der modernen Kryptographie entwickelt. Alle hier behandelten Verfahren wurden weiterhin in Bezug auf eine Realisierung in Hardware optimiert. Es werden drei thematische Schwerpunkte behandelt.

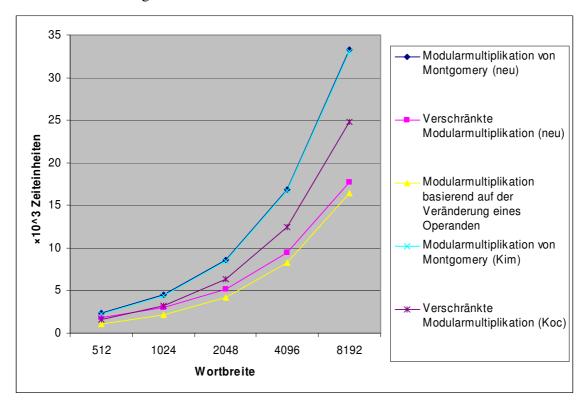

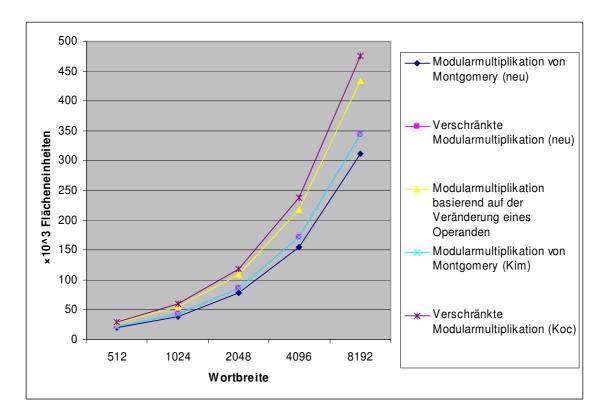

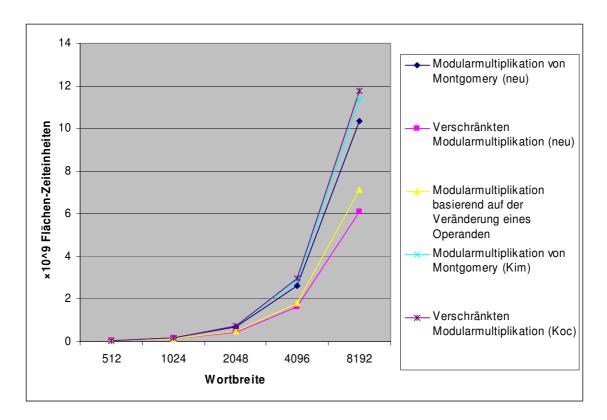

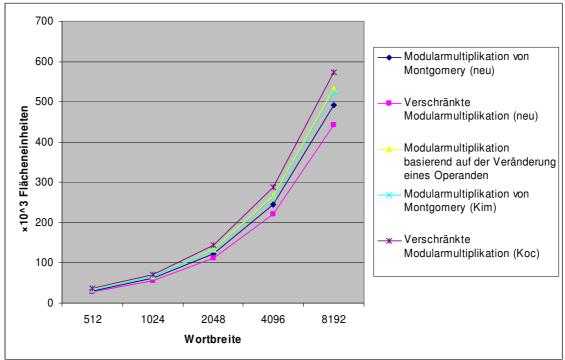

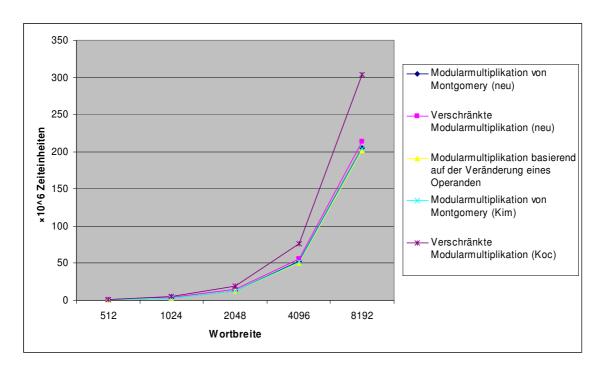

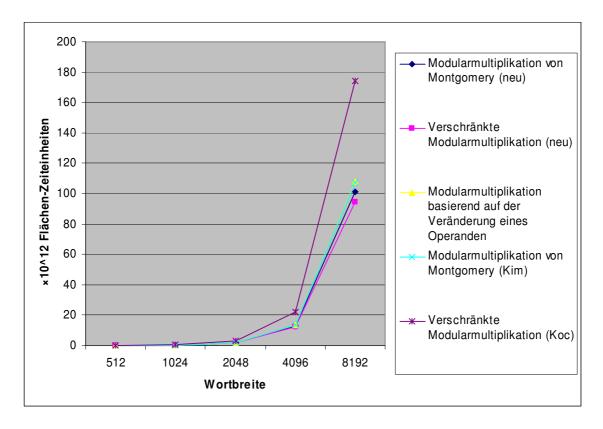

Als erstes werden neue Methoden zur Berechnung der Modularmultiplikation aufgezeigt, die sich durch ein besonders günstiges Flächen-Zeit-Produkt auszeichnen. Dabei wird zunächst eine neue Version der Modularmultiplikation von Montgomery entwickelt, bei der die Anzahl der Additionseinheiten gegenüber den besten bisher bekannten Verfahren halbiert werden kann. Danach wird die Verschränkte Modularmultiplikation behandelt. Bezogen zur derzeit als bestgeltenden Version kann hier die Anzahl der Additionseinheiten um einen Faktor drei reduziert werden. Der dritte Algorithmus ist ein in dieser Arbeit neu entwickeltes Verfahren, bei dem nicht nur die Berechnungen, sondern auch die Eingaben in redundanter Form erfolgen. Dadurch kann die Umrechnung von redundanter in nichtredundante Form bei der mehrfachen Anwendung der Modularmultiplikation, wie z.B. bei der Modularen Exponentiation, eingespart werden, ohne zusätzlichen Zeit- bzw. Flächenaufwand zu benötigen. Alle drei Algorithmen werden in die Modulare Exponentiation eingebettet und in Hinsicht auf ihre Komplexität evaluiert.

Das zweite Thema ist ein zeitoptimaler paralleler Algorithmus für die Modularmultiplikation, der eine Zeitkomplexität von O(logn) aufweist. Dabei wird die Eigenschaft ausgenutzt, dass bei den meisten Anwendungen, wie z. B. bei RSA oder Elliptischen Kurven, viele aufeinander folgende Modularmultiplikationen mit dem gleichen Modulus erforderlich sind.

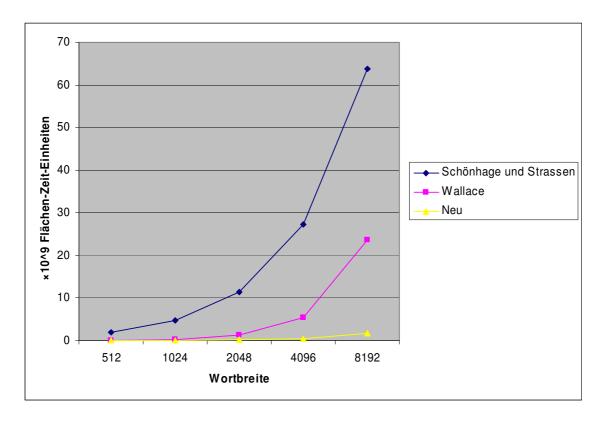

Das dritte Thema behandelt ein Verfahren für die zeitoptimale Multiplikation. Die Zeit-komplexität dieses Algorithmus liegt ebenso bei O(logn). Das Verfahren hat eine bessere asymptotische Flächen-Zeit-Komplexität als der in den meisten Prozessoren benutzte Wallace Tree. Darüber hinaus ist der Flächen-Zeit-Aufwand einer realen Implementierung deutlich niedriger als beim Wallace Tree oder im Falle der Schönhage-Strassen-Multiplikation, welche in ihrer Flächen-Zeit-Komplexität besser ist als alle bisher bekannten Verfahren.

Mein Dank gilt Prof. Dr. Manfred Schimmler, der mir ermöglichte auf diesem Forschungsgebiet zu promovieren und mich während meiner ganzen Arbeit mit viel Leidenschaft betreute. Ich danke Prof. Dr. Thomas Wilke für seine Verbesserungsvorschläge und Prof. Dr. Christof Paar für das Einverständnis bei meiner Promotion Gutachter zu sein. Herzlich bedanken möchte ich mich bei meinem Freund Stefan Vocke und meinem Bruder Stanislav Bunimov, die meine Arbeit mehrfach lasen und mit ihren Ratschlägen zur deren Verbesserung viel beitrugen. Ferner bedanke ich mich bei meinen Kollegen Gerd Pfeiffer, Jürgen Noss und Stefan Baumgart, die beim Lesen der ausgewählten Stellen meiner Arbeit mich auf die stilistischen Ungenauigkeiten aufmerksam machten.

## Inhaltsverzeichnis

| Inhaltsverzeichnis                                                      | 1   |

|-------------------------------------------------------------------------|-----|

| Abbildungsverzeichnis                                                   | iii |

| Algorithmenverzeichnis                                                  | v   |

| Tabellenverzeichnis                                                     | vii |

| Tabellenverzeichnis                                                     | vii |

| 1 Einführung                                                            | 1   |

| 2 Bisherige Lösungen für die Modularmultiplikation                      | 13  |

| 3 Ein einfaches Hardwaremodell                                          | 19  |

| 3.1 Mathematische Notationen                                            | 19  |

| 3.2 Addition                                                            | 19  |

| 3.2.1 Carry-Save-Addition und redundante Zahlendarstellung              | 19  |

| 3.3 Komplexitätsmodell                                                  | 21  |

| 3.3.1 Definition der Komplexität                                        | 21  |

| 3.3.2 Volladdierer                                                      | 22  |

| 3.3.3 Ripple-Carry-Addierer                                             | 22  |

| 3.3.4 Carry-Save-Addierer                                               | 23  |

| 3.3.5 Carry-Look-Ahead-Addierer                                         | 24  |

| 3.3.6 Kombiaddierer                                                     | 27  |

| 3.3.7 Register                                                          | 28  |

| 3.3.8 Lookup Table                                                      | 28  |

| 3.3.9 Bauelemente für die Datensteuerung                                | 29  |

| 3.3.10 Zusammenfassung                                                  | 30  |

| 3.4 Flächenkomplexitätsanalyse                                          | 31  |

| 4 Sequenzielle Algorithmen der Modularmultiplikation                    | 35  |

| 4.1 Montgomery Modularmultiplikation und die Verbesserung durch di      | e   |

| Nutzung einer Lookup Table                                              | 35  |

| 4.1.1 Algorithmus von Montgomery                                        | 35  |

| 4.1.2 Redundante Variante der Implementierung des Algorithmus von       |     |

| Montgomery in Hardware                                                  | 39  |

| 4.1.3 Optimierung des Algorithmus von Montgomery unter Benutzung        |     |

| vorberechneter Werte                                                    | 40  |

| 4.1.4 Komplexitätsanalyse                                               | 44  |

| 4.1.5 Zusammenfassung                                                   | 48  |

| 4.2 Interleaved Modularmultiplikation                                   | 48  |

| 4.2.1 Interleaved Modularmultiplikation                                 | 48  |

| 4.2.2 Optimierung des Algorithmus im Bezug auf Fläche und Zeit          | 52  |

| 4.2.3 Verschränkte Modularmultiplikation mit einem Carry-Save-          |     |

| Addierer                                                                | 59  |

| 4.2.4 Komplexitätsanalyse                                               | 66  |

| 4.2.5 Zusammenfassung                                                   | 70  |

| 4.3 Modularmultiplikation basierend auf der Veränderung eines Operanden | 71  |

| 4.3.1 Darstellung des neuen Algorithmus                                 | 71  |

| 4.3.2 Optimierungsvorschläge                                            | 73  |

| 4.3.3 Unvollständige Modularmultiplikation                               | 77  |

|--------------------------------------------------------------------------|-----|

| 4.3.4 Vollständige Modularmultiplikation                                 |     |

| 4.3.5 Modularmultiplikation mit dem redundanten Addierer                 |     |

| 4.3.6 Redundante Modularmultiplikation                                   |     |

| 4.3.7 Komplexitätsanalyse                                                |     |

| 4.3.8 Zusammenfassung                                                    |     |

| 4.4 Algorithmenvergleich und Zusammenfassung                             | 88  |

| 5 Redundante Modulare Exponentiation                                     |     |

| 5.1 Algorithmus für Modulare Exponentiation                              |     |

| 5.2 Modulare Exponentiation basierend auf Redundan                       |     |

| Modularmultiplikation                                                    | 94  |

| 5.2.1 Beschreibung des Algorithmus                                       | 94  |

| 5.2.2 Komplexitätsanalyse                                                | 95  |

| 5.3 Modulare Exponentiation basierend auf der verschränkt                | ten |

| Modularmultiplikation                                                    | 96  |

| 5.3.1 Beschreibung des Algorithmus                                       | 96  |

| 5.3.2 Komplexitätsanalyse                                                | 97  |

| 5.4 Modulare Exponentiation basierend auf der Modularmultiplikation v    |     |

| Montgomery                                                               | 98  |

| 5.4.1 Beschreibung des Algorithmus                                       |     |

| 5.4.2 Komplexitätsanalyse                                                | 100 |

| 5.5 Algorithmenvergleich und Zusammenfassung                             |     |

| 6 Parallele Algorithmen der Modularmultiplikation                        |     |

| 6.1 Parallele Modularmultiplikation basierend auf der Benutzung von Look |     |

| Tables                                                                   |     |

| 6.1.1 Idee der schnelleren Modularen Potenzierung                        |     |

| 6.1.2 Algorithmus für Modularmultiplikation                              |     |

| 6.1.3 Komplexität der Parallelen Modularmultiplikation                   |     |

| 6.1.4 Optimierung                                                        |     |

| 6.1.5 Abschlussfolgerung                                                 |     |

| 7 Andere Algorithmen der Computerarithmetik                              |     |

| 7.1 Parallele Multiplikation                                             |     |

| 7.1.1 Problembeschreibung                                                |     |

| 7.1.2 Darstellung des Algorithmus                                        |     |

| 7.1.3 Optimierte Version des Algorithmus unter Verwendung von Carry-     |     |

| Save-Addierern                                                           |     |

| 7.1.4 Beispielrealisierung                                               |     |

| 7.1.5 Zusammenfassung                                                    |     |

| 8 Zusammenfassung und Ausblick                                           |     |

| Referenzen                                                               | 127 |

# Abbildungsverzeichnis

| Abbildung 3.3.1: Schaltbild eines Volladdierers                                   | 22   |

|-----------------------------------------------------------------------------------|------|

| Abbildung 3.3.2: Ripple-Carry-Addierer                                            | 23   |

| Abbildung 3.3.3: Schaltbild eines Ripple-Carry-Addierers                          | 23   |

| Abbildung 3.3.4: Carry-Save-Addierer                                              | 23   |

| Abbildung 3.3.5: Schaltbild eines Carry-Save-Addierers                            | 24   |

| Abbildung 3.3.6: 4-bit Carry-Look-Ahead-Addierer                                  |      |

| Abbildung 3.3.7: Schaltbild eines Carry-Look-Ahead-Addierers                      | 26   |

| Abbildung 3.3.8: Funktionsweise eines Kombiaddierers                              |      |

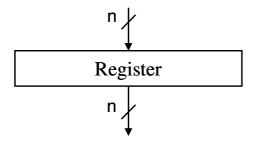

| Abbildung 3.3.9: <i>n</i> -bit Register                                           |      |

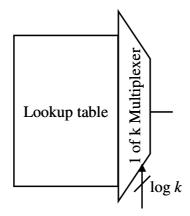

| Abbildung 3.3.10: Schaltbild der Lookup Table                                     | 29   |

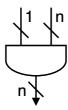

| Abbildung 3.3.11: Schaltbild des Datenwegschalters                                | 30   |

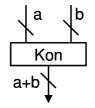

| Abbildung 3.3.12: Schaltbild für die Konkatenation                                | 30   |

| Abbildung 3.3.13: Schaltbild für die Dekonkatenation                              |      |

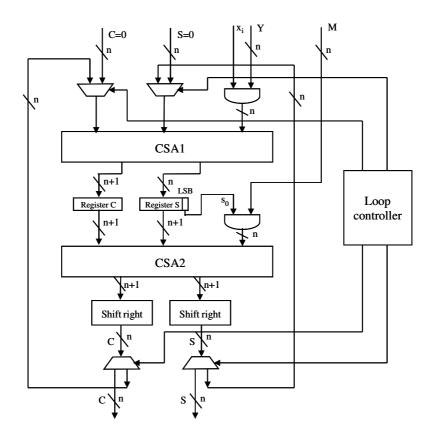

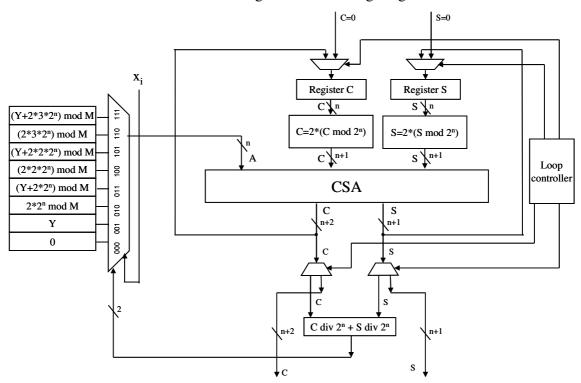

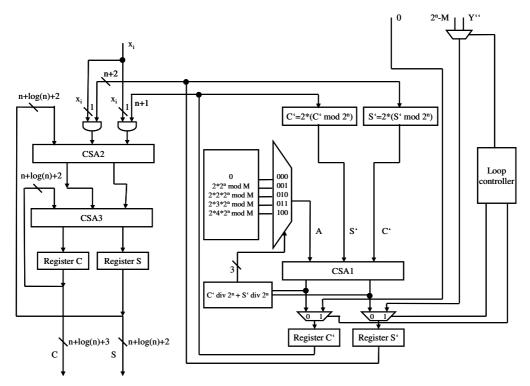

| Abbildung 4.1.1: Modularmultiplikation von Montgomery mit Carry-Save-Addierer     | n 40 |

| Abbildung 4.1.2: Schleifendurchlauf der schnellen Modularmultiplikation von       |      |

| Montgomery                                                                        |      |

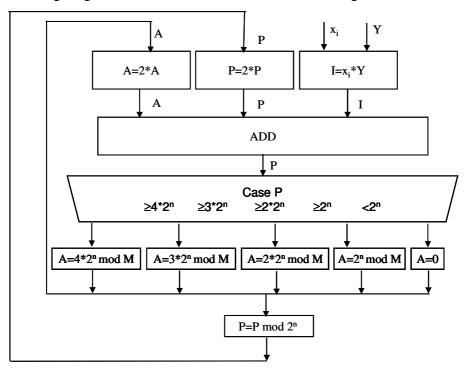

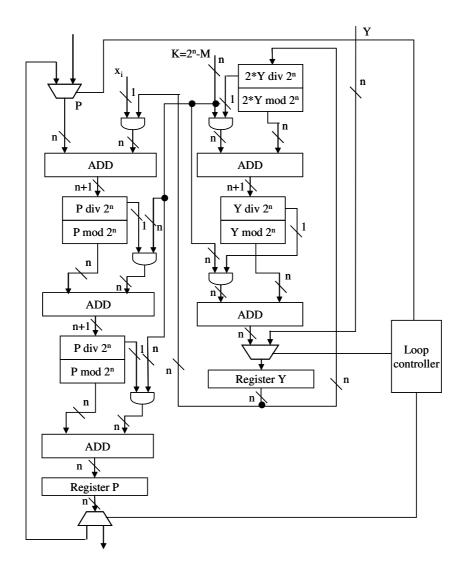

| Abbildung 4.2.1: Ein Schleifendurchlauf des Algorithmus 4.2.1                     | 51   |

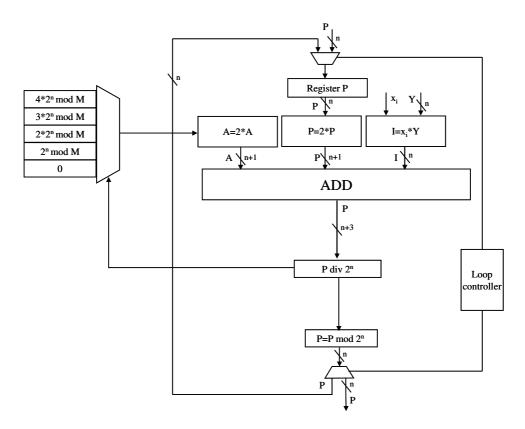

| Abbildung 4.2.2: Ein Schleifendurchlauf der verbesserten verschränkten            |      |

| Modularmultiplikation                                                             |      |

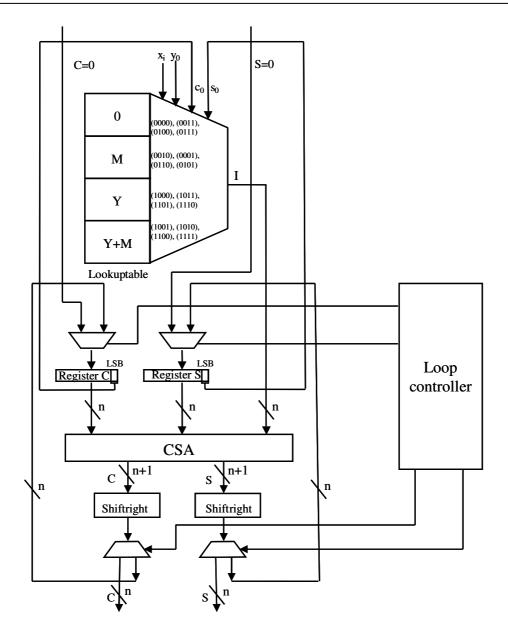

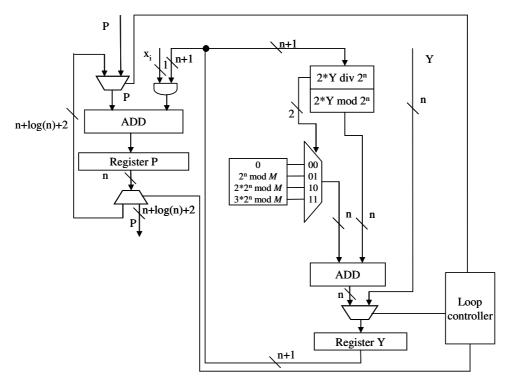

| Abbildung 4.2.3: Verschränkte Modularmultiplikation unter Benutzung einer Looku   |      |

| Table                                                                             | 55   |

| Abbildung 4.2.4: Ein Schleifendurchlauf der verschränkten Modularmultiplikation   |      |

| ohne Verdopplung des Korrekturwertes                                              | 56   |

| Abbildung 4.2.5: Ein Schleifendurchlauf der verschränkten Modularmultiplikation   |      |

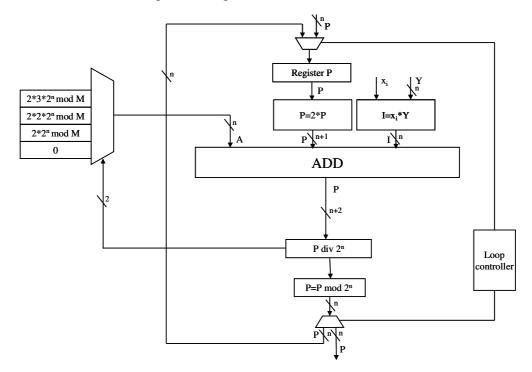

| mit einem Addierer                                                                | 58   |

| Abbildung 4.2.6: Ein Schleifendurchlauf der verschränkten Modularmultiplikation   |      |

| mit einem Carry-Save-Addierer                                                     |      |

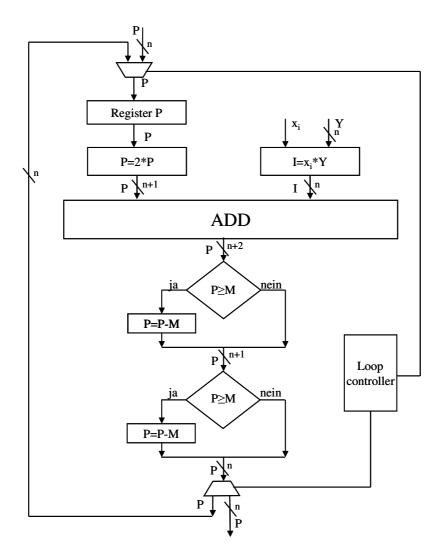

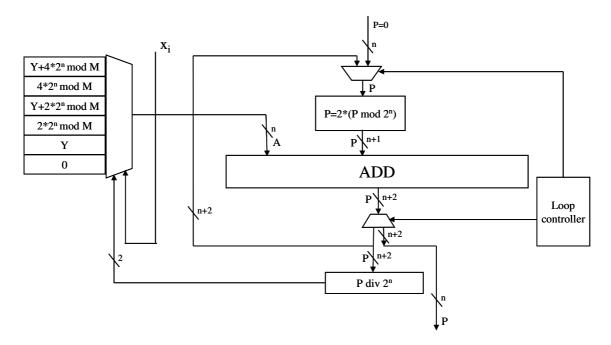

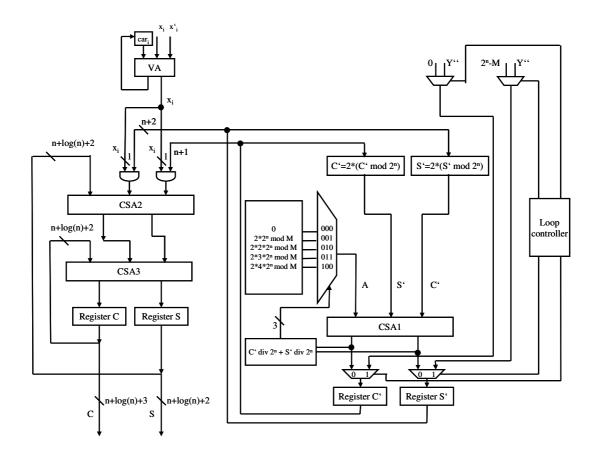

| Abbildung 4.3.1: Ein Schleifendurchlauf des Algorithmus 4.3.2                     |      |

| Abbildung 4.3.2: Ein Schleifendurchlauf des Algorithmus 4.3.4                     |      |

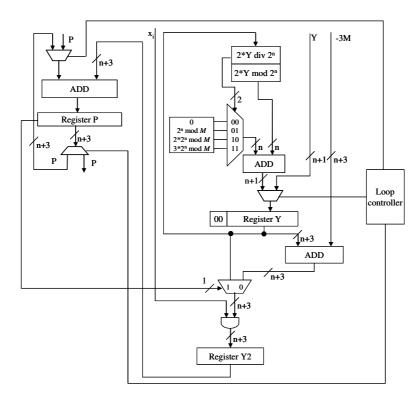

| Abbildung 4.3.3: Ein Schleifendurchlauf des Algorithmus 4.3.5                     | 81   |

| Abbildung 4.3.4: Modularmultiplikation basierend auf der Veränderung eines        |      |

| Operanden unter der Benutzung von redundanten Carry-Save-                         |      |

| Addierern                                                                         |      |

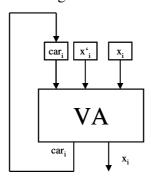

| Abbildung 4.3.5: Bit-serielle Berechnung von <i>X</i>                             |      |

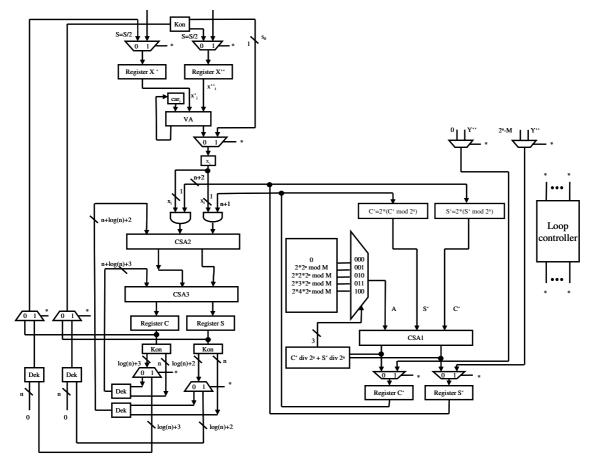

| Abbildung 4.3.6: Ein Schleifendurchlauf des redundanten Modularmultiplizierers    |      |

| Abbildung 4.3.7: Redundanter Modularmultiplizierer                                |      |

| Abbildung 7.1.1: Unterteilung von <i>n</i> Bits in <i>t</i> -bit-lange Intervalle |      |

| Abbildung 7.1.2: Binärer Baum der Addition der Teilergebnisse                     | .117 |

# Algorithmenverzeichnis

| Algorithmus 4.1.1: Modularmultiplikation von Montgomery                           | 36   |

|-----------------------------------------------------------------------------------|------|

| Algorithmus 4.1.2: Redundante Modularmultiplikation von Montgomery                |      |

| Algorithmus 4.1.3: Schnelle Modularmultiplikation von Montgomery                  | 42   |

| Algorithmus 4.1.4: Ausführliche Darstellung der Modularmultiplikation von         |      |

| Montgomery mit Lookup Table                                                       | 45   |

| Algorithmus 4.2.1: Verschränkte Modularmultiplikation                             | 49   |

| Algorithmus 4.2.2: Verschränkte Modularmultiplikation mit approximativem          |      |

| Vergleich                                                                         | 53   |

| Algorithmus 4.2.3: Verschränkte Modularmultiplikation unter Benutzung einer       |      |

| Lookup Table                                                                      | 55   |

| Algorithmus 4.2.4: Verschränkte Modularmultiplikation ohne Verdopplung des        |      |

| Korrekturwertes                                                                   | 57   |

| Algorithmus 4.2.5: Verschränkte Modularmultiplikation mit einem Addierer          | 58   |

| Algorithmus 4.2.6: Verschränkte Modularmultiplikation mit redundanter Carry-      |      |

| Save-Addition                                                                     | 61   |

| Algorithmus 4.2.7: Verschränkte Modularmultiplikation mit verkürzter              |      |

| Abschlussphase                                                                    |      |

| Algorithmus 4.3.1: Grundvariante des neuen Verfahrens                             |      |

| Algorithmus 4.3.2: Erste Optimierung des neuen Algorithmus                        | 74   |

| Algorithmus 4.3.3: Optimierte Version der Modularmultiplikation basierend auf der |      |

| Veränderung eines Operanden                                                       |      |

| Algorithmus 4.3.4: Unvollständige Modularmultiplikation                           |      |

| Algorithmus 4.3.5: Vollständige Modularmultiplikation                             | 80   |

| Algorithmus 4.3.6: Modularmultiplikation basierend auf der Veränderung eines      |      |

| Operanden unter der Benutzung von redundanten Carry-Save-                         |      |

|                                                                                   | 83   |

| Algorithmus 4.3.7: Redundante Modularmultiplikation basierend auf der             |      |

| Veränderung eines Operanden                                                       |      |

| Algorithmus 5.1.1: Binäre Modulare Exponentiation                                 | 93   |

| Algorithmus 5.2.1: Binäre Modulare Exponentiation basierend auf Redundanter       |      |

| Modularmultiplikation                                                             | 94   |

| Algorithmus 5.3.1: Binäre Modulare Exponentiation basierend auf der verschränkten |      |

| Modularmultiplikation                                                             | 97   |

| Algorithmus 5.4.1: Binäre Modulare Exponentiation basierend auf der               |      |

| Modularmultiplikation von Montgomery                                              | 99   |

| Algorithmus 5.4.2: Binäre Modulare Exponentiation basierend auf der               |      |

| Modularmultiplikation von Montgomery                                              |      |

| Algorithmus 6.1.1: Parallele Modularmultiplikation                                |      |

| Algorithmus 6.1.2: Modulare Exponentiation                                        | .110 |

## **Tabellenverzeichnis**

| Tabelle 3-1: Wahrheitstabelle eines Volladdierers                                | .22 |

|----------------------------------------------------------------------------------|-----|

| Tabelle 3-2: Komplexität einzelner Hardwareelemente                              | .31 |

| Tabelle 3-3: Standard Schaltkreise bei unterschiedlichen Technologien            | .32 |

| Tabelle 4-1: Komplexität der vollständigen Modularmultiplikation von Montgomery  | .48 |

| Tabelle 4-2: Komplexität der verschränkten Modularmultiplikation                 | .70 |

| Tabelle 4-3: Komplexität der Modularmultiplikation basierend auf der Veränderung |     |

| eines Operanden.                                                                 | .87 |

| Tabelle 5-1: Komplexitätsanalyse der Redundanten Modularen Exponentiation        |     |

| basierend auf der Veränderung eines Operanden                                    | .96 |

| Tabelle 5-2: Flächen-Zeit-Komplexität der Modularen Exponentiation basierend auf |     |

| der Veränderung eines Operanden                                                  | .96 |

| Tabelle 5-3: Flächen-Zeit-Komplexität der Modularen Exponentiation basierend auf |     |

| der verschränkten Modularmultiplikation                                          | .98 |

| Tabelle 5-4: Flächen-Zeit-Komplexität der Modularen Exponentiation basierend auf |     |

| der Modularmultiplikation von Montgomery1                                        | 01  |

| Tabelle 6-1: Lookup Table mit n unterschiedlichen Zweierpotenzen modulo 21       | 06  |

| Tabelle 6-2: Lookup Table für eine parallele 4-bit Modularmultiplikation1        | 07  |

Die Wissenschaft der Verschlüsselung von Informationen (Kryptographie) spielt seit Jahrtausenden eine wichtige Rolle in der menschlichen Gesellschaft. Schon Julius Cäsar benutzte ein Chiffrierverfahren, um Kriegsnachrichten zu verschlüsseln und somit zu verhindern, dass seine Geheimnisse in fremde Hände geraten. Seitdem nahm die Bedeutung der Kryptographie für militärische Zwecke immer mehr zu: Die Datenmengen, die verschlüsselt werden sollten, wuchsen und gleichzeitig stiegen die Anforderungen an die Sicherheit. Einer der Höhepunkte des Bedeutungszuwachses der Kryptographie war die Entschlüsselung der ENIGMA Chiffre durch die Alliierten im Zweiten Weltkrieg, mit deren Hilfe der Krieg im Atlantik gewonnen wurde. Darüber hinaus kann dies als ein entscheidender Wendepunkt im Verlauf des Zweiten Weltkriegs geltend gemacht werden [69], [37].

Bis Mitte des 20. Jahrhunderts spielte die Kryptographie nur im militärischen Bereich und in der Politik eine wichtige Rolle. Mit der Einführung der EDV wurde sie aber auch für die Wirtschaft unabdingbar, denn die stetig wachsende Speicherkapazität der immer kleiner werdenden Datenträger (elektronische Speichermedien, Filme, etc.) bringt unweigerlich Sicherheitsprobleme für die Unternehmen mit sich. Um zu verhindern, dass unbefugte Personen in der Lage sein könnten, neue Entwicklungen, Kundendaten und andere wichtige Informationen zu stehlen, müssen die Daten heute verschlüsselt werden. Ein weiterer Aspekt zur Steigerung der Sicherheit ist das Problem der Authentifizierung von Personen und Nachrichten. Zudem brachte die Globalisierung zusätzliche Veränderungen im Nutzungsprofil der Kryptographie: Firmen verfügen heute über ein Netz von Filialen in unterschiedlichen Ländern, deren Daten zwischen den verschiedenen Standorten elektronisch übertragen und somit von nicht autorisierten Personen abgefangen werden könnten. Es ist somit unumgänglich, die Daten zu verschlüsseln, um den Zugriff durch Unbefugte zu verhindern.

In der modernen Kryptographie existieren zwei sich vom Wesen her unterscheidende Ansätze: Erstens die so genannten symmetrischen Verschlüsselungsverfahren, bei denen der Klartext und der Chiffretext mit demselben Schlüssel chiffriert bzw. dechiffriert werden. Die symmetrischen Chiffrierverfahren werden auch als "Secret Key"-Ver-

fahren bezeichnet, da der Schlüssel geheim sein muss; denn sollte eine dritte unbefugte Person den Schlüssel kennen, wäre diese in der Lage, den Chiffretext zu dechiffrieren und somit den Klartext zu lesen. Im Allgemeinen gelten die symmetrischen Chiffrierverfahren als sehr schnell und erlauben daher eine Informationsübertragung mit hohen Datenraten [72].

Die zweite Kategorie stellen die asymmetrischen Chiffrierverfahren dar, deren Besonderheit die Verwendung zweier unterschiedlicher Schlüssel ist. Mit dem ersten Schlüssel, der öffentlich bekannt ist, ist jede Person in der Lage, einen Klartext zu chiffrieren, weshalb solche Verfahren auch "Public Key"-Verfahren genannt werden. Der zweite Schlüssel, der nur dem Empfänger bekannt ist und daher als geheimer Schlüssel bezeichnet wird, dient dazu den Chiffretext zu dechiffrieren. Der Vorteil eines solchen Verfahrens ist unter anderem die Möglichkeit der Schlüsselübertragung über einen unsicheren Kanal. Die asymmetrischen Verfahren gelten als sichere Verschlüsselungen [72], allerdings sind die Operationen, die nötig sind, um eine solche Nachricht zu entbzw. verschlüsseln, mit einem erhöhten Rechenaufwand verbunden. Demzufolge haben asymmetrische Kryptoverfahren eine niedrige Datenrate. Um diese zu erhöhen, werden solche Verfahren häufig direkt in Hardware implementiert, was eine Beschleunigung um Faktor 100 oder mehr mit sich bringen kann.

Wird ein Problem mit Hilfe von Software (Implementierung der Problemlösung in einer Programmiersprache und Ausführung des so entstehenden Programms auf einer vorgegeben Hardware) gelöst, so muss vor allem die Zeitkomplexität als Bewertungsmaß des zugrundeliegenden Algorithmus betrachtet werden. Diese entspricht dem Produkt aus der Anzahl der Maschinenbefehle und der durchschnittlichen Dauer eines Befehls auf der Hardware. Wird eine Hardwarelösung gewählt, die eigens für einen speziellen Zweck entwickelt wurde und somit keinen Maschinenbefehlssatz besitzt, so entspricht die Zeitkomplexität dem Produkt aus der Anzahl der Takte und der Dauer eines Taktes. Bei einer speziellen Hardwarelösung ist nicht nur die Zeit-, sondern auch die Flächenkomplexität bedeutsam, die ein Maß für die Fläche des Chips, in dem die entsprechenden Funktionen implementiert sind, darstellt. Da die Chipfläche eine technologieabhängige Größe ist, wird ein abstraktes Maß für die in dieser Arbeit benutzten Bauelemente definiert, welches durch eine Evaluierung verschiedener Technologien erarbeitet wurden. Ähnlich wie bei der Flächenkomplexität ist auch die Zeitkomplexität technologieabhängig. Demzufolge wird gleichermaßen auch ein einheitliches Maß für die Zeitkomplexität definiert. Damit dieses Maß eine realistische

Bewertung der zu betrachtenden Algorithmen erlaubt, wird dessen Verifikation in Abschnitt 3.3 ebenfalls durch eine Gegenüberstellung verschiedener Technologien durchgeführt.

Die Zeit- und die Flächenkomplexität sind meistens voneinander abhängig, da durch eine Verringerung der Zeitkomplexität häufig die Flächenkomplexität eines Verfahrens wächst und umgekehrt. Um in der Lage zu sein allgemeingültige Aussagen zu treffen, mit denen unterschiedliche Verfahren miteinander verglichen werden können, ist es daher notwendig ein technologieunabhängiges Maß zu definieren, bei dem sowohl die Flächen- als auch die Zeitkomplexität zum Tragen kommt. Auf Grund der hier aufgeführten Überlegungen empfiehlt sich die Verwendung des Flächen-Zeit-Produkts als ein solches Maß [70]. In Abschnitt 3.3 werden aus diesem Grund die Zeit- und Flächenkomplexität der meisten in dieser Arbeit benutzten Bauelemente definiert und deren Flächen-Zeit-Produkt berechnet.

Viele asymmetrische Verfahren (unter ihnen auch die am häufigsten benutzten Verfahren wie RSA [62] oder Elliptische Kurven [50]) basieren auf der wiederholten Anwendung derselben Rechenoperation: Der Modularmultiplikation. Diese ist eine mathematische Operation, deren Eingabe aus drei ganzen Zahlen besteht, wobei die ersten zwei als Operanden und die dritte als Modulus bezeichnet werden. Das Ergebnis der Modularmultiplikation ist der Rest der Division des Produktes der beiden Operanden durch den Modulus. In modernen kryptographischen Anwendungen werden Operanden mit einer Länge von mehreren Hundert Bits verwendet; so werden z.B. beim RSA-Verfahren oft Operanden ab 1024 Bits und mehr benutzt. Mit steigender Operandengröße erhöht sich die Länge der für die Speicherung erforderlichen Register in der Hardwareschaltung. Ein Register besteht aus einer Menge von Flipflops, die parallel zueinander schalten, wobei jedes Flipflop ein Bit speichern kann. Mit steigender Operandenlänge erhöhen sich sowohl der Bedarf an Logik und somit auch die Flächenkomplexität als auch die Zeitkomplexität der Gesamtschaltung. Demzufolge ist es sinnvoll, die Komplexität der Schaltung durch algorithmische Verbesserungen zu optimieren.

Es gibt mehrere Algorithmen für die Modularmultiplikation (eine ausführliche Auseinandersetzung mit diesen Algorithmen wird im Kapitel 2 durchgeführt). Am häufigsten werden dabei die Modularmultiplikation von Montgomery [53] und die verschränkte (Interleaved) Modularmultiplikation [12] (eine genaue Beschreibung dieser Algorithmen findet in den Abschnitten 4.1 und 4.2 statt) benutzt. Die verschränkte Modularmultiplikation war der erste Algorithmus für die Modularmultiplikation, der es erlaubte die

Multiplikation und die Modulare Reduktion (Berechnung des Divisionsrestes) ineinander zu verschachteln und damit die Bitlänge des Zwischenergebnisses zu reduzieren. Es wurde weiterhin erreicht, dass die verschränkte Modularmultiplikation auf drei schnelle Additionen pro Schleifendurchlauf reduziert wurde [42]. Der Nachteil dabei liegt in der Tatsache, dass die Vergleiche zeitineffizient sind. Der zweite Algorithmus, die Modularmultiplikation von Montgomery, ist heute der am häufigsten benutzte Algorithmus, dessen Vorteil darin besteht, dass er keine komplizierten Vergleiche enthält. Die beste existierende Lösung [40] reduziert den Algorithmus auf zwei redundante Additionen pro Schleifeniteration.

Ziel dieser Arbeit ist die Entwicklung mehrerer Algorithmen für die Modularmultiplikation mit geringerer AT-Komplexität (area-time complexity) als bei allen bisher existierenden Verfahren. Dabei ist die AT-Komplexität das Produkt der Flächen- und der Zeitkomplexität. Dieses wird bei der Hardwareentwicklung oft als das Maß für die Güte der neuen Schaltung verwendet. Um die AT-Komplexität der bereits existierenden Verfahren zu reduzieren werden drei neue Algorithmen entwickelt: Der erste Algorithmus basiert auf der Modularmultiplikation von Montgomery, die auf eine schnelle Addition pro Schleifeniteration reduziert wird, wobei hierdurch eine Verbesserung um das Vierfaches gegenüber dem besten bisher bekannten Verfahren [40] erreicht wird. Der zweite Algorithmus baut auf der verschränkten Modularmultiplikation auf, dabei wird die Anzahl der Additionen auf eine pro Schleifeniteration reduziert, die ineffizienten Vergleiche werden nicht mehr benötigt. Insgesamt wird eine Komplexitätsverbesserung mindestens um den Faktor sechs gegenüber dem gegenwärtig führenden Verfahren [42] erreicht.

Der Nachteil des Algorithmus von Montgomery und der verschränkten Modularmultiplikation ist, dass die Verwendung der schnelleren Addition eine spezielle redundante Zahlendarstellung erfordert. Die Eingaben für die Modularmultiplikation müssen

hingegen in der binären Standarddarstellung erfolgen. Da bei den meisten Anwendungen die Modularmultiplikation mehrmals wiederholt wird, wird eine Konvertierung aus

der redundanten Zahlendarstellung in die binäre Standarddarstellung notwendig. Das

Problem der Konvertierung, die zusätzlichen Flächen- und Zeitaufwand benötigt, wird

durch den dritten Algorithmus gelöst. Dieser bietet ein neues mathematisches Modell

an, das nicht nur die Nutzung der schnellen Addition, sondern auch Eingaben in redundanter Zahlendarstellung erlaubt. Dadurch ist die mehrmalige Konvertierung bei wiederholter Modularmultiplikation überflüssig.

Die drei neu entwickelten Algorithmen werden danach in die Exponentiation eingebettet.

Darüber hinaus werden zwei weitere neue Algorithmen für die parallele Modularmultiplikation und die parallele Multiplikation vorgestellt. Sowohl bei dem Algorithmus

für die parallele Modularmultiplikation, als auch bei dem für die parallele StandardMultiplikation beträgt die Zeitkomplexität O(logn). Der Vorteil des Multiplikationsalgorithmus gegenüber den existierenden Lösungen liegt in der Tatsache, dass er nicht nur

eine gute asymptotische Komplexität, sondern auch kleine Koeffizienten besitzt und

somit in praktischen Anwendungen implementiert werden kann.

Diese Arbeit ist wie folgt strukturiert: Kapitel 2 bietet einen Vergleich der existierenden Algorithmen für die Modularmultiplikation. In Kapitel 3 werden einige der am häufigsten benutzten Bauelemente (Schaltungen) vorgestellt, ein Komplexitätsmodell definiert und die Zeit- und Flächenkomplexität der oben beschriebenen Bauelemente erläutert. Außerdem wird eine Analyse unterschiedlicher VLSI-Technologien (Very Large Scale Integration) durchgeführt, die die praktische Relevanz des Komplexitätsmodells bestätigen.

In Kapitel 4 werden drei neue Algorithmen für die Modularmultiplikation entwickelt. Zunächst wird in Abschnitt 4.1 die Modularmultiplikation von Montgomery [53] eingeführt, bei der die einzelnen Bits des ersten Operanden schrittweise vom niederwertigsten bis zum höchstwertigsten Bit mit dem zweiten Operand multipliziert werden. Die so entstehenden Teilprodukte werden addiert und produzieren eine Folge von Zwischenergebnissen, wobei nach jeder Addition eine Normierung erfolgt. Insgesamt benötigt die Modularmultiplikation von Montgomery n Schleifendurchläufe. Der Vorteil der Montgomery-Modularmultiplikation liegt in der Tatsache, dass während der Berechnung keine Vergleiche erforderlich sind, die aufwendig in Hinsicht auf die Komplexität sind. Allerdings werden in der Originalfassung langsame Standardadditionen angewendet. Dem Montgomery-Verfahren, welches einen Meilenstein in der Geschichte der modularen Arithmetik darstellt, folgten eine Reihe von Optimierungen und Implementierungen durch andere Wissenschaftler, welche in Kapitel 2 detailliert behandelt werden. Als Basis für die in dieser Arbeit entwickelte Version dient die Arbeit von Kim, Kang und Choi [40], bei der die Standardadditionen durch geschickte schnelle Additionen ersetzt werden, die das Verfahren von Montgomery auf zwei redundante Additionen pro Schleifendurchlauf reduzieren. In Abschnitt 4.1.2 wird zunächst deren Verbesserung

detailliert beschrieben. Danach folgt in Abschnitt 4.1.3 die Entwicklung eines neuen Algorithmus, in dem die Eigenschaft ausgenutzt wird, dass alle Werte, die während der einzelnen Schleifendurchläufe zum Zwischenergebnis aufaddiert werden, konstant sind. Alle möglichen Kombinationen dieser Summanden werden vor der Schleife einmal berechnet und auf eine spezielle Art und Weise gespeichert. Während jedes Schleifendurchlaufs wird vorhergesagt, welcher Wert im nächsten Schleifendurchlauf aufaddiert werden muss. Dieser Korrekturwert wird danach aus dem Speicher gelesen und Hilfe einer schnellen Addition zum Zwischenergebnis mit addiert. Somit kann in einem Schleifendurchlauf eine einzige, anstatt zwei nacheinander folgenden Additionen durchgeführt werden. Demzufolge reduziert sich sowohl die Flächenkomplexität, als auch die Zeitkomplexität des Verfahrens, was wiederum eine Verbesserung der AT-Komplexität um den Faktor vier mit sich bringt. Weiterhin verifiziert die in Abschnitt 4.1.4 durchgeführte Komplexitätsanalyse die Komplexität des neuen Algorithmus. Die Grundidee dieser Version wurde in [17] veröffentlicht; einige Weiterentwicklungen mit dem Vergleich zu anderen Algorithmen wurden in [22] und [23] publiziert.

In Abschnitt 4.2 wird die verschränkte Modularmultiplikation erörtert, die der Idee der Modularmultiplikation von Montgomery ähnlich ist: Der erste Operand wird bitweise mit dem zweiten Operanden multipliziert und die so entstandenen Teilprodukte werden miteinander addiert. Vor jeder Addition einer solchen Art erfolgt eine Verdopplung des Zwischenergebnisses; danach findet eine modulare Reduktion statt. Der Unterschied zur Modularmultiplikation von Montgomery liegt in der Tatsache, dass der erste Operand nicht vom niederwertigsten zum höchstwertigsten Bit, sondern vom höchstwertigsten zum niederwertigsten Bit durchlaufen wird. Der Vorteil dabei ist, dass die verschränkte Modularmultiplikation das Ergebnis einer Modularmultiplikation berechnet, wohingegen der Algorithmus von Montgomery zweimal durchlaufen werden müsste, um das Ergebnis der Modularmultiplikation zu bestimmen. Der Nachteil liegt in der Tatsache, dass die verschränkte Modularmultiplikation mehrere Vergleiche benötigt, die wiederum die Anwendung einer schnellen Addition, wie beim Algorithmus von Montgomery, erschweren.

Die verschränkte Modularmultiplikation benötigt ebenfalls *n* Schleifendurchläufe, wobei in jedem Schleifendurchlauf das Ergebnis des vorherigen verdoppelt und danach, falls erforderlich, der zweite Operand aufaddiert wird. Das Zwischenergebnis wird einer Modularen Reduktion unterzogen, welche zwei Vergleiche und bis zu zwei Subtraktionen des Modulus enthält. In Abschnitt 4.2.2 werden mehrere Verbesserungen vorge-

schlagen: Zuerst werden die aufwändigen Vergleiche mit dem Modulus durch einfache Vergleiche mit einer Zweierpotenz ersetzt. Bei einem Vergleich zweier Zahlen müssen alle Bits beider Zahlen paarweise miteinander verglichen werden, wohingegen bei einem Vergleich mit der entsprechenden Zweierpotenz bei der zu vergleichenden Zahl nur ein einziges Bit überprüft wird. Ist dieses eine Eins, so ist die Zahl größer oder gleich der zugehörigen Zweierpotenz, ansonsten ist die Zahl kleiner. Danach wird die Anzahl der Subtraktionen des Modulus abgeschätzt. Noch vor den Schleifendurchläufen wurden alle möglichen Subtraktionswerte einmal berechnet und in einer Tabelle (Lookup Table) gespeichert. Die Abschätzung der Subtraktionsanzahl dient als Steuerung (Adressierung) für die Lookup Table. Durch die oben beschriebenen Verbesserungen wird die Anzahl der Operationen in einem Schleifendurchlauf auf zwei Additionen reduziert: Die erste ist für die Addition des Produktes des entsprechenden Bits des ersten Operanden mit dem zweiten Operanden; die zweite dient der Reduktion. Gleichwohl verändert sich der zweite Operand, der während des Schleifendurchlaufs aufaddiert wird, nicht innerhalb der Schleife. Als eine weitere Verbesserung wird auf die Addition mit dem zweiten Operanden verzichtet. Stattdessen wird der zweite Operand in die Lookup Table eingefügt. Die letzte Verbesserung halbiert die Anzahl der Additionen in einem Schleifendurchlauf. In Abschnitt 4.2.3 wird die verbliebene Addition durch eine Carry-Save-Addition ersetzt, was eine weitere Verringerung der Zeitkomplexität des Verfahrens bewirkt. In Abschnitt 4.2.4 wird die Komplexitätsanalyse dieser neuen Verfahren durchgeführt. Einige in diesem Abschnitt vorgestellte Verbesserungen wurden bereits in [18], [21], [22], [23], [64] veröffentlicht.

Alle existierenden Algorithmen – einschließlich der in den Abschnitten 4.1 und 4.2 präsentierten Verfahren – haben einen nicht zu vernachlässigbaren Nachteil: Obwohl während der Modularmultiplikation selbst im redundanten Zahlensystem gerechnet werden kann, erfordern die Modularmultiplikationen die Eingaben in nichtredundanter Form. Die Ausgaben dagegen werden in der redundanten Form berechnet, demzufolge wird nach jeder Modularmultiplikation eine Konvertierung aus der redundanten Form in die nichtredundante Form benötigt, die zusätzliche Hardware und Zeit erfordert. Dementsprechend steigt die Zeit- und die Flächenkomplexität und folglich auch deren Produkt. Der in Abschnitt 4.3 beschriebene Algorithmus bietet eine Möglichkeit, diesen Nachteil zu beheben. Während die neuen Algorithmen aus den Abschnitten 4.1 und 4.2 auf bereits existierenden mathematischen Modellen basieren, wird in Abschnitt 4.3 ein vollkommen neues mathematisches Modell entwickelt. Der Vorteil dieses Modells ge-

genüber anderen existierenden Verfahren für die Modularmultiplikation liegt in der Tatsache, dass sowohl alle Berechnungen als auch alle Eingaben im redundanten Zahlensystem erfolgen. Die Idee des neuen Algorithmus der Modularmultiplikation, basierend auf der Veränderung eines Operanden, ist grundsätzlich einfach: Die einzelnen Bits des ersten Operanden werden mit dem zweiten Operand multipliziert, und diese Teilprodukte werden zum Zwischenergebnis hinzuaddiert, was der Modularmultiplikation von Montgomery und der verschränkten Modularmultiplikation entspricht. Allerdings wird dabei nicht das Zwischenergebnis jedes Mal reduziert und um ein Bit verschoben, sondern der zweite Operand wird in jedem Schleifendurchlauf verdoppelt und einer Modularen Reduktion unterzogen. Als Folge steigt der Wert des Zwischenergebnisses viel langsamer an als bei den anderen Verfahren. In Abschnitt 4.3.2 werden verschiedene Optimierungsvorschläge diskutiert: Der langsame Vergleich mit dem Modulus wird durch den schnelleren Vergleich mit einer Zweierpotenz ersetzt und die Subtraktionen von dem Modulus werden durch die Reduktion mit Hilfe einer Lookup Table mit vorberechneten Werten durchgeführt. Die Verdopplung mit der anschließenden Reduktion des zweiten Operanden und die Summenbildung des Teilproduktes mit dem Zwischenergebnis werden nebenläufig ausgeführt, hierdurch wird die Zeitkomplexität des Verfahrens verbessert. In den Abschnitten 4.3.3 und 4.3.4 werden zwei unterschiedliche Versionen der Modularmultiplikation, basierend auf der Veränderung eines Operanden, vorgestellt. Die nachfolgenden Abschnitte 4.3.5 und 4.3.6 stellen eine Weiterentwicklung der Version aus Abschnitt 4.3.3 dar: Die Addition im redundanten Zahlensystem ersetzt die Addition im nichtredundanten Zahlensystem, das heißt, dass die Addition mit Hilfe eines Carry-Save-Addierers erfolgt, dessen Anwendung wiederum zu einer Verbesserung der Zeitkomplexität des Verfahrens führt. Darüber hinaus werden die Eingänge auf eine solche Art und Weise erweitert, dass die Eingabe im nichtredundanten Zahlensystem möglich wird. Mit dieser Optimierung wird die aufwändige Konvertierung ins nichtredundante Zahlensystem nach jeder Modularmultiplikation überflüssig, was die Anwendung mehrerer Modularmultiplikationen mit dem gleichen Modulus vereinfacht. Die Komplexitätsanalyse und die Zusammenfassung beenden den Abschnitt 4.3. Die meisten Ideen dieses Abschnittes können in [67], [68] und [24] nachgelesen werden.

Kapitel 5 beschreibt die Modulare Exponentiation [34] und [50], die auf der Modularmultiplikation basiert. Zu diesem Zweck wird in dieser Arbeit in Abschnitt 5.1 einer der Algorithmen für die Modulare Exponentiation vorgestellt. In den darauf folgenden

Abschnitten 5.2, 5.3 und 5.4 werden die Algorithmen für die Modularmultiplikation von Montgomery (Abschnitt 4.1), die verschränkte Modularmultiplikation (Abschnitt 4.2) und die Modularmultiplikation basierend auf der Veränderung eines Operanden (Abschnitt 4.3) in die Modulare Exponentiation eingebettet. Darüber hinaus wird in Abschnitt 5.5 die Komplexitätsanalyse der Modularen Exponentiation mit unterschiedlichen Algorithmen für die Modularmultiplikation durchgeführt.

Kapitel 4 und Kapitel 5 konzentrieren sich auf neue Algorithmen für Modulare Arithmetik, die in Hinsicht auf das Flächen-Zeit-Produkt optimiert werden. Solche Optimierungen sind in dem Falle wichtig, wenn z.B. für die Massenfertigung die Kosten minimiert werden müssen. Die Optimierung der Modularmultiplikation in Bezug auf das Produkt von Fläche und Zeit ist auch unter anderen Gesichtspunkten wichtig: Die Modularmultiplikation kann als eingebettete Funktion bei Smartcards, Handys und anderen Kommunikationsgeräten implementiert werden, da solche Geräte eine begrenzte Fläche zur Verfügung stellen. Außerdem ist die Taktrate aus Gründen der Leistungseffizienz häufig niedriger als bei stationären Geräten. Darüber hinaus spielt der Stromverbrauch, welcher neben anderen Faktoren stark von der Fläche des Chips abhängt, eine wichtige Rolle, insbesondere bei mobilen Geräten kommt dies zum Tragen, da deren Leistungsfähigkeit durch die begrenzte Stromkapazität der Batterie eingeschränkt ist.

Manchmal spielen die Kosten und damit das AT-Produkt aber auch eine untergeordnete Rolle. Dann wird versucht die Datenrate zu minimieren und eine zeitoptimale

Lösung zu entwickeln. Eine solche Vorgehensweise ist z. B. häufig in technisch-wissenschaftlichen Anwendungen wichtig, da es sich hierbei meist um Einzellösungen, die

somit nur einmalige Kosten verursachen, und nicht um Massenprodukte handelt. Ein

Beispiel dafür bieten kryptographische Verfahren wie z.B. RSA, für deren Implementierung kostengünstige Lösungen gesucht werden, die es ermöglichen, mehrere Millionen

Hardware-Chips zu bauen. Beim Versuch, diese Verfahren zu brechen, wird dagegen oft

nur eine einzige Implementierung angestrebt, die es erlaubt, die verschlüsselte Nachricht schnell zu brechen. Diese niedrige Zeitkomplexität wird oft durch hohe Kosten

und somit hohen Flächenaufwand erreicht.

Die folgenden Kapitel 6 und Kapitel 7 zeigen zwei zeitoptimale neue Algorithmen für die Standard-Modularmultiplikation und für eine Multiplikation, die mit logarithmischer Zeitkomplexität arbeiten.

In Kapitel 6 wird ein neuer zeitoptimaler Algorithmus für die Modularmultiplikation vorgestellt, der eine logarithmische Zeitkomplexität besitzt. Dies wird erreicht, indem mehrere nur vom Modulus abhängige Werte initial berechnet und dann für mehrere Modularmultiplikationen mit dem gleichen Modulus in eine Lookup Table gespeichert werden. In jeder Modularmultiplikation wird zuerst die Multiplikation, für die ein Wallace Tree [86] mit der Zeitkomplexität von O(logn) benutzt wird, durchgeführt. Danach werden die n höchstwertigsten Bits durch die in der Lookup Table gespeicherten Werte parallel zueinander ersetzt. Somit wird eine 2n-bit-lange Zahl durch eine Summe von n n-bit-langen Zahlen ersetzt, die wiederum mit dem Wallace Tree aufaddiert werden und ein Ergebnis liefern, das durch eine n+logn-bit-lange Zahl repräsentiert ist. Diese Berechnungen werden solange wiederholt, bis das Ergebnis länger als n-bit ist. Die Idee für dieses Verfahren wurde bereits in [20] veröffentlicht.

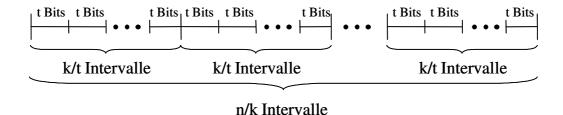

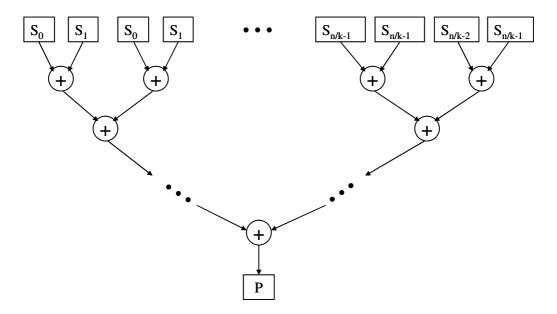

Ein zeitoptimaler Algorithmus für die Standard-Modularmultiplikation wird in Kapitel 7 aufgezeigt. Es gibt viele Algorithmen für die Multiplikation [29], [38], [41], [73], [74], [76], [83], [86], [90], [91] und [92], von denen viele eine AT-Komplexität kleiner als O(n<sup>2</sup>) besitzen [38], [41], [72], [83], [90], [91] und [93]. Für eine reale Implementierung in Hardware sind diese Algorithmen jedoch weniger geeignet. Einige von ihnen (z. B. [38] oder [83]) haben eine Zeitkomplexität von mehr als O(n). Andere (z. B. [73] und [90]) haben zwar eine optimale Zeitkomplexität von O(logn) und eine hohe AT-Komplexität von O(nlog<sup>2</sup>nloglogn), benötigen bei der Hardwareimplementierung aber sehr hohe Koeffizienten und sind somit für die praktische Anwendung nur beschränkt geeignet. In modernen Prozessoren wird heute für die Multiplikation ein Wallace Tree mit nachgelagertem Carry-Look-Ahead-Addierer [86] benutzt, der die optimale Zeitkomplexität  $O(\log n)$  hat. Die Flächenkomplexität des Wallace Tree liegt dagegen bei  $O(n^2)$ . Dementsprechend ist die AT-Komplexität des Wallace Tree  $O(n^2 \log n)$ . Der Algorithmus, der in Kapitel 7 vorgestellt wird, hat ebenso wie der Wallace Tree die optimale Zeitkomplexität  $O(\log n)$ ; die Flächenkomplexität liegt dagegen bei  $O(n^2/\log^2 n)$ . Demzufolge beträgt die AT-Komplexität des Algorithmus  $O(n^2/\log n)$ . Dabei sind die Konstanten, die für die Hardwareimplementierung nötig sind klein. Der Grundgedanke des Algorithmus ist einfach: Es findet eine dreifache Unterteilung des ersten Operanden in mehrere Intervalle statt. Dabei wird die Multiplikation kleinerer Intervalle mit dem zweiten Operanden durch das Einfügen vorberechneter Werter ersetzt, die in einer Lookup Table gespeichert sind. Die Ergebnisse in jedem mittleren Intervall werden mit einem einfachen Addierer aufsummiert. Die so gewonnenen Ergebnisse werden mit

dem Wallace Tree aufaddiert. Die Grundidee dieses Verfahrens wurde in [19] veröffentlicht.

In Kapitel 8 folgt die abschließende Zusammenfassung, der in dieser Arbeit gewonnenen Ergebnisse, und es wird eine Wertung geliefert. Ferner wird ein Ausblick auf mögliche weitere Einsatzgebiete gegeben.

## 2 Bisherige Lösungen für die Modularmultiplikation

Modularmultiplikation ist eine mathematische Operation, bei der der ganzzahlige Divisionsrest des Produkts zweier Operanden und einer dritten Zahl, dem so genannten Modulus, berechnet wird. In den meisten Anwendungen sind die Operanden kleiner als der Modulus, der wiederum oft eine ungerade Zahl in der Größenordnung zwischen 2<sup>150</sup> und 2<sup>8000</sup> ist. Kryptografische Verfahren stellen das Haupteinsatzgebiet für die Modularmultiplikation dar. So besteht z.B. die Ver- und die Entschlüsselung bei dem als Standard geltendem RSA-Kryptoverfahren [62] jeweils aus einer Modularen Exponentiation [34], [50] und [72]. Die Modularmultiplikation ist wiederum die Grundoperation bei den meisten Algorithmen der letzteren Verfahren. Hierbei wird diese mehrmals nacheinander ausgeführt, was zu einem hohen Rechenaufwand führt. Dies ist der Grund dafür, dass mehrere Algorithmen für die Modularmultiplikation existieren und weitere noch effizientere Methoden entwickelt werden.

Der älteste Algorithmus für die Modularmultiplikation ist die klassische Modularmultiplikation [41]. Hierbei wird zuerst die Multiplikation und dann die modulare Reduktion, bei der der Divisionsrest bestimmt wird durchgeführt. Ein Nachteil der klassischen Modularmultiplikation liegt in der Tatsache, dass das Zwischenergebnis die doppelte Länge der Eingaben besitzt, da das Ergebnis der Multiplikation zweier *n*-bit Zahlen eine 2*n*-bit Zahl ist. Die doppelte Zahlenlänge führt bei einer Implementierung in der Hardware zu einer Erhöhung des Aufwandes der Schaltung, was wiederum eine deutliche Verschlechterung der Gesamtkomplexität der zu betrachtenden Anwendung mit sich bringt. Im letzten Viertel des zwanzigsten Jahrhunderts wurde daher eine Reihe weiterer Algorithmen entwickelt:

In einem – der Modularmultiplikation von Barrett [8] – wurde eine Modularmultiplikation durch mehrere Standardmultiplikationen ersetzt. Der Vorteil dabei ist, dass Barrett eine eventuell schon vorhandene Hardware für Multiplikation wie z.B. einen Wallace Tree [86] anwenden kann. Jedoch zeigen sich dabei auch mehrere Nachteile: Ähnlich wie die Klassische Modularmultiplikation erfordert der Algorithmus von Bar-

rett mindestens ein Register, das doppelt so groß ist wie die Eingabewerte. Darüber hinaus ist die Zeitkomplexität bei Barrett dreimal so hoch wie bei einer normalen Multiplikation. Daraus resultierend ist auch die AT-Komplexität um Faktor drei größer als bei der Verwendung der Multiplikation.

Der Algorithmus von Barrett wurde in mehreren Arbeiten weiterentwickelt. So beschleunigte [33] die Modularmultiplikation von Barrett durch eine Pipeline im Wallace Tree und durch die Anwendung des Algorithmus von Booth [15]. Letzterer erlaubt bei der Berechnung des Produktes zweier Zahlen durch die geschickte Benutzung der Basis vier, die Anzahl der bei der Multiplikation entstehenden Teilprodukte zu halbieren. Trotz dieser Optimierungen ist die AT-Komplexität relativ hoch. Eine weitere Verbesserung, welche auf vergleichbaren Ideen wie in [33] basiert, liefert [56].

Eine andere Vorgehensweise bei der Modularmultiplikation liegt in der Benutzung des RNS (Residue Number System), welches auf folgender Grundidee aufbaut: Durch die Anwendung des Chinesischen Restesatzes wird das Problem der Modularmultiplikation in eine Menge von kleineren Problemen unterteilt. Mehrere Arbeiten setzen diese Methode als Lösungsansatz ein. So wird bei [1], [5] und [6] die Modularmultiplikation in kleinere Probleme unterteilt, die mit Hilfe von gewöhnlichen Standardprozessoren (z.B. 32-bit Prozessoren) gelöst werden können. Eine weitere Möglichkeit ist es, das RNS direkt bei der Montgomery Modularmultiplikation (der dazugehörige Algorithmus wird später in dieser Arbeit detailliert betrachtet) anzuwenden. Somit wird im so genannten MRNS (Montgomery Residue Number System) gearbeitet, wie z.B. in [60] und [61]. Allerdings dienen solche Lösungen nur der Skalierung des Problems, die AT-Komplexität wird hierbei nicht reduziert.

Ein weiterer Algorithmus ist die Interleaved Modularmultiplikation (verschränkte Modularmultiplikation). Die Grundidee dieses Algorithmus ist die Bildung der Teilprodukte einzelner Bits eines Operanden mit dem zweiten Operanden. So wird in jedem Schleifendurchlauf ein solches Produkt zum Zwischenergebnis dazuaddiert, welches nachfolgend der Modularen Reduktion unterzogen wird. Dieser Algorithmus wird in [12] präsentiert und in [75] verbessert. Später folgte eine ganze Reihe von Veröffentlichungen, bei denen die verschränkte Modularmultiplikation überarbeitet wurde. So ersetzt [57] den aufwändigen Vergleich mit dem Modulus durch den schnellen Vergleich mit einer Zweierpotenz. Eine weitere Optimierung [69] basiert darauf, dass die einzelnen Operationen innerhalb eines Schleifendurchlaufs parallelisiert wurden, wodurch sich die Zeitkomplexität verringert. Eine der besten Optimierungen in Bezug auf das

Flächen-Zeit-Produkt wurde in [42] veröffentlicht. Die Interleaved Modularmultiplikation wird mit drei redundanten Addierern durchgeführt. Diese Lösung hat allerdings zwei Nachteile: Zum einen erhöhen drei redundante Addierer (Carry-Save-Addierer) den Flächenaufwand; zum anderen wird während der Berechnung mehrmals ein Vergleich mit Null durchgeführt, wobei der Autor in [42] auch negative Zahlen verwendet, was den oben beschriebenen Vergleich allerdings sehr aufwendig macht, da dieser in einem redundanten Zahlensystem durchgeführt wird. Eine weitere Möglichkeit der Nutzung der redundanten Zahlen bieten [77] und [78], wobei die einzelnen Ziffern aus {-2, -1, 0, 1, 2} bestehen. Die Addition von solchen Zahlen hat im Vergleich zu binären Zahlen eine höhere Zeit- und Hardwarekomplexität. Außerdem benutzen die beiden oben beschriebenen Algorithmen und weitere Algorithmen wie [27], [42] oder [54] höhere Basen. Dies bringt zwar eine Verringerung der Zeitkomplexität, allerdings nur auf Kosten der Flächenkomplexität. Eine weitere Version der verschränkten Modularmultiplikation wurde in [59] veröffentlicht. Hierbei werden ebenso Carry-Save-Addierer, Tabellen mit vorberechneten Werten und höhere Basen benutzt. Allerdings sind sowohl die Anzahl der Carry-Save-Addierer als auch der Umfang der Tabellen sehr groß und die Flächenkomplexität demzufolge relativ hoch. In [39] wurde eine weitere Version der verschränkten Modularmultiplikation aufgezeigt, die ebenfalls den Carry-Save-Addierer benutzt. Einige Werte werden dabei vorberechnet und können später mehrmals angewendet werden. Der Nachteil dabei ist, dass diese Werte in Registern gespeichert werden und sich somit die Flächenkomplexität der Schaltung erhöht. Ferner gibt es Arbeiten wie [11], in denen eine für FPGA (Field Programmable Gate Arrays) optimierte Algorithmen präsentiert werden. Solche Varianten bieten zwar eine sehr kostengünstige individuelle Lösung, sind aber in Bezug auf das Flächen-Zeit-Produkt in der Regel nicht optimal.

Das am häufigsten benutzte Verfahren ist die Modularmultiplikation von Montgomery [53]. Die Idee dieses Algorithmus ist ähnlich wie bei der verschränkten Modularmultiplikation: Es werden Teilprodukte einzelner Bits eines Operanden mit dem zweiten Operand gebildet und zur Zwischensumme aufaddiert. Im Gegensatz zu Interleaved Modularmultiplikation wird der zweite Operand vom niederwertigsten zum höchstwertigsten Bit bearbeitet. Eine genaue Beschreibung dieses Verfahrens wird in Abschnitt 4.1 durchgeführt. Viele wissenschaftliche Arbeiten beschäftigen sich mit der Modularmultiplikation von Montgomery. So wurden in [80], [81] und [82] skalierbare Algorithmen für die Modularmultiplikation entwickelt, welche hauptsächlich der Flä-

chenminimierung dienen. Dies wiederum geschieht auf Kosten der Zeitkomplexität, so dass die AT-Komplexität dabei nicht verbessert wird. Einige Arbeiten befassen sich mit den Implementierungen auf FPGAs [13], [14], [47], [79], [80], und [82]. Solche Algorithmen sind zwar kostengünstig, aber nicht optimal im Bezug auf die AT-Komplexität, denn die einzelnen Zellen der FPGAs, die jeweils nur eine einfache logische Funktion ausführen, besitzen eine hohe Flächenkomplexität. Eine weitere Vorgehensweise ist die Implementierung systolischer Felder [10], [31] und [89]. Eine solche Implementierung bedeutet, dass die Schaltung in eine Menge der gleichen Funktionen, die als Prozessorelemente bezeichnet werden, unterteilt wird. Eine solche Anordnung hat vor allem zwei Vorteile: An erster Stelle ist zu nennen, dass nicht die ganze Schaltung, sondern nur ein einzelnes Prozessorelement optimiert wird, da die anderen Prozessorelemente nur dessen Kopien sind. Der zweite Vorteil ist die Möglichkeit, eine solche Schaltung in eine regelmäßige Hardwarestruktur (z. B. FPGA) einzubetten. Der Nachteil bei all diesen Algorithmen ist deren Komplexität, sowohl in Bezug auf den Flächen-, als auch auf den Zeitaufwand, da es bei solchen harten Strukturen oft nicht möglich ist Optimalität zu gewährleisten. Darüber hinaus gibt es Arbeiten, bei denen die Zeitkomplexität durch die Nutzung der nicht redundanten Zahlensysteme verbessert wird. Dabei werden die einzelnen Ziffern als {-1, 0, 1} dargestellt [37]. Die Operationen (Additionen) sind bei solchen Lösungen sehr schnell im Vergleich zu nichtredundanten Additionen, allerdings deutlich langsamer und flächenaufwändiger als Carry-Save-Additionen, die in Abschnitt 3.2.1 beschrieben werden. Ein weiterer Modularmultiplizierer mit redundanter Addition wurde in [88] veröffentlicht, wobei der dazugehörige Addierer etwa die doppelte Flächenkomplexität eines Carry-Save-Addierers besitzt. Viele Algorithmen benutzen Carry-Save-Additionen [28], [40], [47], [48], wobei eine der besten Implementierungen die von [40] ist. Die Autoren beschreiben eine Lösung, in der nur zwei nacheinander folgende Carry-Save-Additionen in einer Schleifeniteration benutzt werden. Eine andere Version [48] bietet einen vollständig redundanten Modularmultiplizierer, der eine Weiterentwicklung von [40] und [17] darstellt. Der Beitrag [17] ist ein Teil dieser Doktorarbeit und wird detailliert in Abschnitt 4.1. erläutert. Allerdings wird die vollständige Redundanz durch eine Verdopplung des benötigten Flächen- und Zeitaufwandes erreicht und ist somit nicht AT-optimal.

Ansonsten gibt es Arbeiten, in denen mit höheren Basen gearbeitet wird [13], [36], [79] und [81]. Die höheren Basen verbessern zwar das Zeitverhalten der Algorithmen (die Anzahl der Schleifendurchläufe wird reduziert), dabei steigt die Flächenkomplexi-

tät jedoch entsprechend schnell an. Insofern verbessert sich die AT-Komplexität nicht. Es gibt außerdem noch zeitoptimale Algorithmen wie [87], die mit der Zeitkomplexität von  $O(\log n)$  arbeiten. Die Flächenkomplexität ist dagegen sehr schlecht, was dazu führt, dass die AT-Komplexität deutlich niedriger als bei den AT-optimalen Lösungen ist.

Darüber hinaus existieren eine Reihe anderer Lösungen, die nicht AT-optimal sind: Bei [16] handelt es sich um den Vorgänger der verschränkten Modularmultiplikation; [26] zeigt eine Modularmultiplikation von 2*n*-bit Zahlen unter Benutzung der Modularmultiplikation von *n*-bit Zahlen; bei [7] handelt es sich um einen Algorithmus für modulare Reduktion; [35] beschreibt eine hardwarespezifische Lösung unter Verwendung von DSPs (Digital Signal Processor); [46] ist eine softwarebasierte Optimierung; in [1] werden unterschiedliche Skalierungen der Montgomery Modularmultiplikation miteinander verglichen; [49] beschreibt einen Algorithmus, der nur für bestimmte Moduli sinnvoll ist und [58] vergleicht einige Algorithmen mit nichtredundanten Zahlen. Es gibt eine Reihe weiterer, unbedeutender Algorithmen, eine komplette Auflistung würde den Rahmen dieser Arbeit jedoch sprengen.

#### 3 Ein einfaches Hardwaremodell

#### 3.1 Mathematische Notationen

In dieser Arbeit werden folgende mathematische Notationen benutzt: Großbuchstaben bezeichnen Zahlen, die als binäre Vektoren betrachtet werden. So werden vor allem die Operanden, der Modulus und die Potenz bezeichnet. Kleinbuchstaben werden vor allem bei der Darstellung von Faktoren, Indizes oder der Bitlänge einer Zahl verwendet. Mit  $x_i$  wird das i-te Bit von X bezeichnet. "+", "-" und "\*" werden jeweils für die klassischen Addition, Subtraktion bzw. Multiplikation angewandt.

stellt eine XOR-Verknüpfung dar. Weitere logische Schaltungen werden entsprechend ihrer englischen Bezeichnung benutzt. Bei Z=RCA(X, Y) und Z=CLA(X, Y) handelt es sich um die Ripple-Carry- bzw. Carry-Look-Ahead-Additionen. (S, C)=CSA(X, Y, Z) beinhaltet eine Carry-Save-Addition mit drei Eingabezahlen X, Y und Z und zwei Ausgabezahlen S und C, wobei S die Konkatenation der Summen und C die Konkatenation der Übertragsbits beinhalten. Die ausführliche Erklärung der Carry-Save-Addition wird in Abschnitt 3.2.1 gegeben. Mit Lookup(...) wird die Lookup Table bezeichnet. Die Funktionen "div" und "mod" werden jeweils für die ganzzahlige Division bzw. für die Berechnung des Divisionsrestes verwendet. Dabei ist das Ergebnis der Operation A mod M eine ganze Zahl und es gilt: 0≤A mod M<M. Das Zeichen "≅" beinhaltet Kongruenz. Zwei Zahlen A und B heißen kongruent modulo M zueinander, wenn gilt A mod  $M = B \mod M$ , so bedeutet  $X \cong Y \mod M$ , dass X gleich Y mod M plus ein Vielfaches des Modulus M ist.

#### 3.2 Addition

#### 3.2.1 Carry-Save-Addition und redundante Zahlendarstellung

Die zentrale Operation der meisten Algorithmen für die Modularmultiplikation ist die binäre Addition. Es gibt mehrere Additionsverfahren: Ripple-Carry-Addition, Carry-Select-Addition, Carry-Look-Ahead-Addition und andere [24], [43], [44], [63]. Der Nachteil all dieser Methoden ist das Weiterleiten des Übertragsbits, das die Latenzzeit der Addition in die Abhängigkeit zur Operandengröße stellt. Dies hat zwar nur

eine geringe Auswirkung für kleine Operanden (z.B. der Länge 64 Bit), aber eine gravierende Wirkung auf die Addition bei Kryptoverfahren, bei denen die Operandengröße zwischen 1024 und 8192 Bit liegen kann. Die Zeitkomplexität einer solchen Addition bestimmt hierbei die Komplexität des Gesamtverfahrens.

Die Carry-Save-Addition bietet die Möglichkeit, eine Addition auszuführen, ohne den Übertrag weiterleiten zu müssen. Sie ist eine einfache parallele Schaltung von n Volladdierern, die nicht miteinander verbunden sind. Die Funktion dieser Volladdierer ist es, drei n-bit-lange ganze Zahlen X, Y und Z miteinander zu addieren. Das Ergebnis sind zwei ganze n+1-bit lange Zahlen C und S mit der Eigenschaft:

$$C + S = X + Y + Z \tag{3.1}$$

Das i-te Bit der Summe  $s_i$  und der i+1-te Bit des Übertrages  $c_{i+1}$  werden durch die folgenden booleschen Gleichungen berechnet:

$s_i = x_i \oplus y_i \oplus z_i$

$s_n=0$

$$c_{i+1} = x_i y_i \lor x_i z_i \lor y_i z_i$$

$$c_0 = 0$$

(3.2)

Im Folgenden wird für eine Carry-Save-Addition die Notation

$$(S, C) = CSA(X, Y, Z) \tag{3.3}$$

verwendet.

Das Zahlenpaar (*S*, *C*) bildet eine redundante Darstellung der Zahl *S*+*C*, die so auf unterschiedliche Art und Weise dargestellt werden kann. Die Addition der Zahlen in einer solchen redundanten Zahlendarstellung ist einerseits sehr schnell, da bei der Addition kein Weiterleiten des Übertrages nötig ist, bringt anderseits jedoch einen gravierenden Nachteil mit sich: Der Vergleich zwischen zwei Zahlen und ebenso der Vergleich mit Null ist in Bezug auf die Flächen- und Zeitkomplexität sehr aufwändig. Jedoch ist der Vergleich ein wichtiger Bestandteil fast aller Algorithmen der Modularmultiplikation [12], [16], [42].

#### 3.3 Komplexitätsmodell

#### 3.3.1 Definition der Komplexität

Das Ziel dieser Arbeit liegt in der Entwicklung neuer, hardwarenaher Algorithmen für Computerarithmetik. Um zu zeigen, dass die neuen Algorithmen besser als die existierenden sind, werden diese anhand gewisser Maße miteinander verglichen. Die beiden wichtigsten Maße sind die Zeit- und Flächenkomplexität. Die Zeit ist nicht zu vernachlässigen, da die meisten Algorithmen der Computerarithmetik eine sehr hohe Datenrate benötigen und gleichzeitig rechenintensiv sind. Somit ist die Zeit eines der wichtigsten Kriterien für die Güte eines Algorithmus. Die Fläche der Hardware ist ein Maß für die Anzahl der benötigten Gatter und somit die Anzahl der Transistoren auf dem Chip. Die Kosten eines Chips steigen mit der benötigten Fläche. Somit ist die Flächenkomplexität eines der wichtigsten Merkmale bei der Entwicklung von hardwarenahen Algorithmen. Darüber hinaus wird eine Kombination aus diesen beiden Maßen, die AT-Komplexität (Flächen-Zeitkomplexität), definiert. Diese bildet das Produkt aus Flächen- und Zeitkomplexität. Es werden folgende Einheiten definiert: Flächeneinheit, Zeiteinheit und Flächen-Zeit-Produkt-Einheit.

Manchmal werden bei der Analyse der Algorithmen die konstanten Faktoren vernachlässigt. In den praktischen Anwendungen spielen die Konstanten eine sehr wichtige Rolle, da Verfahren mit geringerer asymptotischer Komplexität durch größere Konstanten deutlich höhere Kosten als diejenigen, deren asymptotische Komplexität hoch und deren Konstanten klein sind, verursachen. Als Beispiel dafür kann die ganzzahlige Multiplikation dienen – der Wallace Tree [86] mit einer asymptotischen Komplexität von  $O(n^2 \log n)$  ist für praktische Anwendungen besser geeignet als die Schönhage-Strassen Multiplikation [72], deren Komplexität  $O(n\log^2 n\log\log n)$  beträgt. Aus diesem Grund werden in dieser Arbeit sowohl die asymptotische Komplexität als auch Konstanten berücksichtigt.

Da die Bewertung sowohl der Fläche als auch des Zeitverhaltens einzelner Hardwareelemente sehr stark technologieabhängig ist, wird ein abstraktes Modell benutzt, das näherungsweise einer realen Hardwareimplementierung in CMOS entspricht.

In den nächsten Abschnitten werden die in dieser Arbeit benutzten Hardwareelemente dargestellt und deren Komplexität definiert.

#### 3.3.2 Volladdierer

Zu den wichtigen Hardwareelementen zählt der Volladdierer. Ein Volladdierer verfügt über drei Eingabebits (z. B. x, y, z), Schaltlogik und zwei Ausgabebits (z. B. s und c), wobei die Ausgabe die Summe der drei Eingabebits produziert. Die Funktionsweise eines Volladdierers kann folgender Wahrheitstabelle entnommen werden:

| X | у | Z | c | S |

|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 | 1 |

| 0 | 1 | 0 | 0 | 1 |

| 0 | 1 | 1 | 1 | 0 |

| 1 | 0 | 0 | 0 | 1 |

| 1 | 0 | 1 | 1 | 0 |

| 1 | 1 | 0 | 1 | 0 |

| 1 | 1 | 1 | 1 | 1 |

Tabelle 3-1: Wahrheitstabelle eines Volladdierers

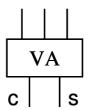

Ein Volladdierer wird durch das folgende Symbol dargestellt:

Abbildung 3.3.1: Schaltbild eines Volladdierers

Die Zeitkomplexität des Schaltens eines Volladdierers wird als eine Zeiteinheit definiert.

Die Flächenkomplexität wird als acht Flächeneinheiten definiert. Die Begründung für diese und weitere Flächenkomplexitätsangaben erfolgt in Abschnitt 3.4. Demgemäß liegt die Flächen-Zeitkomplexität eines Volladdierers bei acht Flächen-Zeit-Produkt-Einheiten.

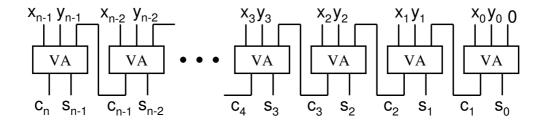

#### 3.3.3 Ripple-Carry-Addierer

Ein *n*-bit Ripple-Carry-Addierer ist ein Schaltkreis, der zwei *n*-bit Zahlen zu einer *n*+1-bit Zahl addiert. Die Addition verläuft von der niederwertigsten zur höchstwertigsten Stelle. Ein *n*-bit Ripple-Carry-Addierer besteht aus *n* Volladdierern, die so miteinander verknüpft sind, dass der Übertrag, der bei der Addition in jedem Volladdierer entsteht, als Eingabe für den nächststehenden Volladdierer dient. Das folgende Bild erläutert die Funktionsweise eines Ripple-Carry-Addierers.

Abbildung 3.3.2: Ripple-Carry-Addierer

Die folgende Abbildung zeigt das Schaltbild eines Ripple-Carry-Addierers:

Abbildung 3.3.3: Schaltbild eines Ripple-Carry-Addierers

Die Zeitkomplexität eines Ripple-Carry-Addierers liegt bei n Schaltvorgängen eines Volladdierers. Das gilt unter der Voraussetzung, dass sowohl die Berechnung des Übertragsbits als auch die Berechnung des Summenbits die gleiche Zeit benötigen. Somit entspricht die Zeitkomplexität eines Ripple-Carry-Addierers n Zeiteinheiten. Die Flächenkomplexität liegt demzufolge bei 8n Flächeneinheiten. Die Flächen-Zeitkomplexität eines Ripple-Carry-Addierers beträgt folglich  $8n^2$  Flächen-Zeit-Produkt-Einheiten.

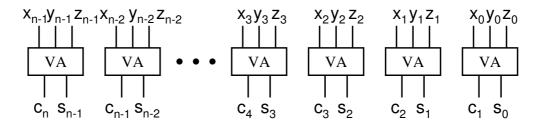

### 3.3.4 Carry-Save-Addierer

Ein *n*-bit Carry-Save-Addierer ist ein Schaltkreis, der drei *n*-bit Zahlen zu zwei *n*+1-bit Zahlen addiert. Eine genauere Beschreibung des Carry-Save-Addierers ist in Abschnitt 3.2.1 zu finden.

Die folgenden Abbildungen zeigen den Aufbau eines Carry-Save-Addierers und dessen Schaltbild:

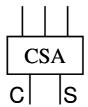

Abbildung 3.3.4: Carry-Save-Addierer

Abbildung 3.3.5: Schaltbild eines Carry-Save-Addierers

Da alle *n* Volladdierer bei einem Carry-Save-Addierer parallel zueinander arbeiten, entspricht die Zeitkomplexität eines Carry-Save-Addierers der Zeitkomplexität eines Volladdierers und beträgt somit eine Zeiteinheit. Die Flächenkomplexität eines *n*-bit Carry-Save-Addierers liegt bei 8*n* Flächeneinheiten. Demzufolge beträgt die Flächen-Zeitkomplexität eines Carry-Save-Addierers 8*n* Flächen-Zeit-Produkt-Einheiten.

#### 3.3.5 Carry-Look-Ahead-Addierer

Der Carry-Look-Ahead-Addierer [9], [25], [43], [63] ist der schnellste bekannte nichtredundante Addierer. Die Hauptidee des Carry-Look-Ahead-Addierers ist das gleichzeitige Generieren aller Überträge. Die so berechneten Werte werden zuerst durch die Struktur eines binären Baumes zur Wurzel und dann an die Blätter zurückgeleitet. Der Carry-Look-Ahead-Addierer hat eine Flächenkomplexität von O(n) und eine Zeitkomplexität von O(logn) [24], [25]. Ein Carry-Look-Ahead-Addierer ist in Form eines Baumes aufgebaut. Es gibt mehrere Versionen des Carry-Look-Ahead-Addierers [25]. Diese unterscheiden sich durch die Anzahl der Einheiten einer Basiszelle. In dieser Arbeit wird die klassische Version des Carry-Look-Ahead-Addierers verwendet. Die Analyse der Standard Cell Libraries, die in Abschnitt 3.4 durchgeführt wird, ergibt, dass ein Carry-Look-Ahead-Addierer etwa die dreifache Flächenkomplexität eines entsprechenden Carry-Save-Addierers besitzt. Dieser Vergleich wurde ohne die Betrachtung der Fläche der Leitungen durchgeführt, auf die in dieser Arbeit verzichtet wurde. Da die Flächenkomplexität eines Carry-Look-Ahead-Addierers bei 8n Flächeneinheiten liegt, wird der Flächenaufwand eines Carry-Look-Ahead-Addierers auf 24n Flächeneinheiten geschätzt.

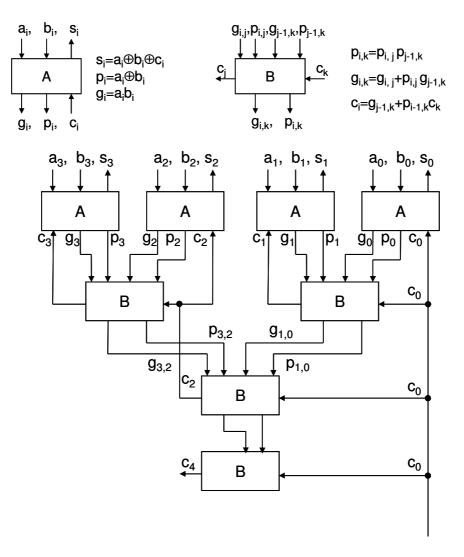

An dieser Stelle wird die Funktionsweise des Carry-Look-Ahead-Addierers erklärt: Um alle Summenbits bei einem Ripple-Carry-Addierer zu bestimmen, müssen im schlechtesten Fall n Übertragbits nacheinander berechnet werden, was zu einer höheren Zeitkomplexität führt. Eine der Möglichkeiten, eine solche Addition zu beschleunigen

ist die parallele Berechnung der Überträge. Für diesen Zweck werden zuerst parallel zueinander "carry-propagate-" und "carry-generate-" Terme berechnet:

$$\begin{aligned} p_i &= a_i \oplus b_i \\ g_i &= a_i b_i \end{aligned} \tag{3.4}$$

Diese können für weitere "carry-propagate-" und "carry-generate-" Terme als Eingabe dienen:

$$p_{i,k} = p_{i,j} p_{j-1,k}$$

$$g_{i,k} = g_{i,j} + p_{i,j} g_{j-1,k}$$

(3.5)

Dabei gilt:

$$i \ge j > k$$

,  $g_{i,i} = g_i$  und  $p_{i,i} = p_i$  (3.6)

Daraus werden die Überträge berechnet:

$$c_{j} = g_{j-1,k} + p_{j-1,k}c_{k}$$

(3.7)

Die Summenbits werden dann als

$$s_i = a_i \oplus b_i \oplus c_i \tag{3.8}$$

bestimmt.

Ein Carry-Look-Ahead-Addierer wird in der Form eines binären Baumes aufgebaut, dessen Knoten die Schaltungen A oder B sind, wie im folgenden Beispiel für einen 4-bit Carry-Look-Ahead-Addierer gezeigt wird:

Abbildung 3.3.6: 4-bit Carry-Look-Ahead-Addierer

Der längste Pfad eines Carry-Look-Ahead-Addierers führt durch 2logn derartiger Schaltungen. Die Zeitkomplexität einer solchen Schaltung ist vergleichbar mit der Zeitkomplexität eines Volladdierers und entspricht somit einer Zeiteinheit. Demzufolge liegt die Gesamtzeitkomplexität des Carry-Look-Ahead-Addierers bei 2logn Zeiteinheiten. Eine genaue Beschreibung eines Carry-Look-Ahead-Addierers ist in [9] und [24] detailliert beschrieben.

Abbildung 3.3.7: Schaltbild eines Carry-Look-Ahead-Addierers

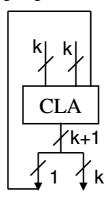

#### 3.3.6 Kombiaddierer

Im letzten Abschnitt wurde der Carry-Look-Ahead-Addierer bewertet. Der Vorteil dieses Addierers ist seine logarithmische Zeitkomplexität. Der Nachteil dabei ist die Tatsache, dass die Flächenkomplexität eines Carry-Look-Ahead-Addierers dreimal so groß wie die Flächenkomplexität eines Carry-Save-Addierers ist. Um diesen Nachteil zu relativieren, wird ein Addierer verwendet, der eine Kombination aus Carry-Look-Ahead und Ripple-Carry-Addierer ist. Um zwei *n*-bit Zahlen zu addieren, wird eine Addition von *k*-bit Blöcken (k≥2) mehrfach nacheinander durchgeführt. Jede *k*-bit Addition wird mit dem *k*-bit Carry-Look-Ahead-Addierer vom niederwertigsten Bit der Operanden ausgehend gemacht. Bei jeder weiteren Addition wird der Übertrag der nächsten Addition aufaddiert. Folgende Abbildung zeigt die Funktionsweise eines Kombiaddierers:

Abbildung 3.3.8: Funktionsweise eines Kombiaddierers

Um zwei *n*-bit Zahlen zu addieren, benötigt ein solcher Kombiaddierer einen *k*-bit Carry-Look-Ahead-Addierer. Die Flächenkomplexität eines solchen Kombiaddierers liegt damit bei 24*k* Flächeneinheiten.

Um eine n-bit Addition durchzuführen, sind  $\lceil n/k \rceil k$ -bit Additionen erforderlich. Ist k dabei ein Teiler von n, so beträgt die Zeitkomplexität eines solchen Addierers

$$2\frac{n}{k} \cdot \log k \tag{3.9}$$

Zeiteinheiten.

Es wird in dieser Arbeit ein Kombiaddierer verwendet, dessen Flächenkomplexität niedriger als bei einem *n*-bit Carry-Save-Addierer ist. Für diesen Zweck wird *k* auf *n*/4 gesetzt, damit ist die Flächenkomplexität eines Kombiaddierers gleich

$$24k = 24\frac{n}{4} = 6n < 8n \tag{3.10}$$

Die Zeitkomplexität eines solchen Kombiaddierers beträgt

$$2\log k \cdot \frac{n}{k} = 2\log \frac{n}{4} \cdot \frac{n}{\frac{n}{4}} = 8(\log n - \log 4) = 8\log n - 8 \cdot 2 = 8\log n - 16 \tag{3.11}$$

Zeiteinheiten.

#### 3.3.7 Register

In allen Schaltungen, die Information zwischenspeichern, werden Register benutzt. Ein 1-bit Register besteht aus einem Flip-Flop, ein *n*-bit Register aus *n* parallel geschalteten Flip-Flops.

Die folgende Abbildung zeigt das Schaltbild eines *n*-bit Registers:

Abbildung 3.3.9: *n*-bit Register

Ein 1-bit Register benötigt nur die Halbe Fläche eines Volladdierers (vgl. 3.4), daher wird die Flächenkomplexität eines 1-bit Registers als 4 Flächeneinheiten definiert. Folglich ist die Flächenkomplexität eines *n*-bit Registers 4*n* Flächeneinheiten. Da die Zeitkomplexität des Schaltens eines Registers bei gegenwärtigen Hardwaretechnologien einerseits niedriger als die Zeitkomplexität eines Volladdierers ist und andererseits in allen in dieser Arbeit betrachteten Algorithmen die gleiche Anzahl der Registerstufen benutzt wird, wird in dem hier verwendeten Komplexitätsmodell auf die Berücksichtigung der Zeit des Registerschaltvorganges (Setup- und Hold-Zeit) verzichtet.

#### 3.3.8 Lookup Table

Im letzten Abschnitt 3.3.7 wurde gezeigt, wie Informationen mit Hilfe von Registern zwischengespeichert werden können. Mehrere Register können gleichzeitig in einem Takt ausgelesen und beschrieben werden. Jedoch muss ihre Verwendung mit relativ hohem Flächenaufwand bezahlt werden. Eine andere Möglichkeit Informationen zwischenzuspeichern bietet die Lookup Table. Eine  $k\cdot n$ -bit Lookup Table enthält k n-bit-lange Worte, die jeweils entweder aus der Lookup Table gelesen oder in die Lookup

Table geschrieben werden können. Allerdings kann pro Takt nur ein Zugriff erfolgen. Obwohl die Lookup Table im Vergleich zu Registern weniger Funktionalität bietet, kann sie den gewichtigen Vorteil einer niedrigen Flächenkomplexität für sich verbuchen. Eine k·n-bit Lookup Table benötigt etwa ein Viertel der Fläche der entsprechenden k n-bit Register. Somit wird die Flächenkomplexität, die für das Speichern eines Bits in der Lookup Table benötigt wird, als eine Flächeneinheit definiert (siehe Abschnitt 3.4). Das Lesen und Schreiben geschieht durch die Adressierung innerhalb der Lookup Table, welche deutlich mehr Zeit als das einfache Lesen und Schreiben in einem Register benötigt. Demgemäß wird die Zeitkomplexität eines Zugriffes auf die Lookup Table als eine Zeiteinheit definiert.

Die folgende Abbildung zeigt das Schaltbild einer  $k \cdot n$ -bit Lookup Table:

Abbildung 3.3.10: Schaltbild der Lookup Table

#### 3.3.9 Bauelemente für die Datensteuerung

In diesem Abschnitt werden einige Schaltungen eingefügt, deren Aufgabe die Steuerung des Datenflusses ist und deren Schaltbilder von der in der Literatur üblichen Standarddarstellung abweichen. Als erstes wird der Datenwegschalter betrachtet, dessen Funktion darin besteht, einen parallelen Datenstrom (Bitvektor) weiterzuleiten, falls das Steuerungsbit eine Eins ist, oder einen Bitvektor, bestehend aus Nullen, zurückzuliefern, falls das Steuerungsbit eine Null ist. Ein Datenwegschalter besteht aus parallel geschalteten UND-Gattern.

Die folgende Abbildung zeigt das Schaltbild eines *n*-bit Datenwegschalters:

#### Abbildung 3.3.11: Schaltbild des Datenwegschalters

Eine weitere Funktion, die in dieser Arbeit verwendet wird, ist die Konkatenation. Diese wird durch das folgende Schaltbild dargestellt:

Abbildung 3.3.12: Schaltbild für die Konkatenation

Ebenso wird die Dekonkatenation (Aufspaltung) benutzt. Das dazugehörige Schaltbild ist:

Abbildung 3.3.13: Schaltbild für die Dekonkatenation

Sowohl der Flächen- als auch der Zeitaufwand eines Datenwegschalters ist relativ gering im Vergleich zum Flächenaufwand eines Carry-Save-Addierers. Darüber hinaus benötigen alle Algorithmen der Computerarithmetik zusätzliche Steuerungselemente. Aus diesem Grund wird die Komplexität dieser Elemente nicht berücksichtigt.

Konkatenation und Dekonkatenation werden in Hardware über geeignete Leitungsführung implementiert. Die Komplexität der Leitungen wird in dieser Arbeit vernachlässigt.

#### 3.3.10 Zusammenfassung

In diesem Kapitel wurden die Begriffe der Flächen- und der Zeitkomplexität sowie deren Produkt, die Flächen-Zeitkomplexität, eingeführt. Außerdem wurden die für diese Arbeit wichtigen Hardwareelemente präsentiert und ihre Komplexität definiert. Die folgende Tabelle bietet einen kurzen Überblick:

| Bezeichnung:                                | Flächenkomplexität/<br>Flächeneinheit | Zeitkomplexität/<br>Zeiteinheit |

|---------------------------------------------|---------------------------------------|---------------------------------|

| Volladdierer                                | 8                                     | 1                               |

| <i>n</i> -bit Ripple-Carry-Addierer         | 8 <i>n</i>                            | n                               |

| <i>n</i> -bit Carry-Save-Addierer           | 8 <i>n</i>                            | 1                               |

| <i>n</i> -bit Carry-Look-<br>Ahead-Addierer | 24 <i>n</i>                           | 2logn                           |

| <i>n</i> -bit Kombiaddierer mit <i>n</i> ≥8 | 6n                                    | 8log <i>n</i> –16               |