# Development and Characterisation of a Process Technology for a 0.25µm SiGe:C RF-BiCMOS embedded Flash Memory

### **Dissertation**

Zur Erlangung des akademischen Grades Doktor der Ingenieurwissenschaften (Dr.-Ing.) der Technischen Fakultät der Christian-Albrechts-Universität zu Kiel

Alexander Fox

Kiel 2006

1. Gutachter Prof. Dr.-Ing. Peter Seegebrecht

2. Gutachter Prof. Dr. rer. nat. Helmut Föll

3. Gutachter Prof. Dr.-Ing. Reinhard Knöchel

Datum der mündlichen Prüfung 11.7.2006

## Acknowledgements

During the time of this dissertation project I worked as part of the scientific staff at the IHP microelectronics research centre, Frankfurt (Oder), Germany. The dissertation has been supervised by Professor Dr.-Ing. Peter Seegebrecht of the "Technische Fakultät der Christian-Albrechts-Universität", Kiel, Germany.

First of all I want to thank Professor Dr.-Ing. Peter Seegebrecht for the supervision of this dissertation, for the confidence he put in me and especially for the time and effort that this required to spend. I enjoyed all the discussions, which gave this dissertation-project a clear structure.

Next I want to thank Professor Dr. rer. nat. Helmut Föll and Professor Dr.-Ing. Reinhard Knöchel to agree to take the responsibility and effort of being the second revisers.

An important support for my work was the positive influence of my colleagues at the IHP.

I want to thank Karl-Ernst Ehwald for the countless technical discussions. I have been in the unique position to work close to a scientist of his experience and deep understanding of physical mechanisms. I also thank him for giving me confidence in my work throughout the project.

I want to thank Dr. Dieter Knoll for technical discussions regarding the baseline process, the HBT and also general technical and project-related topics. I am also thankful for the helpful discussions about the language and structure of the dissertation text.

I want to thank Dr. Bernd Heinemann and Dr. Holger Rücker for being always open for technical and general discussions that supported the development of this the project.

I want to thank Dr. Bernd Tillack for his support as department head of the technology department of the IHP. I am very glad that I have been able to do this work at the IHP in such a straight way and with all the support I needed.

I want to thank Felix Fürnhammer for his support of the project during his time as department head of the technology department of the IHP. I also thank him for being one of the main initiators of the embedded-flash-project at the IHP and of the cooperation with the NTU Kiev.

For the great support of preparing the silicon wafers I want to thank Reiner Barth, (clean room), Andre Wolf (maintenance), Sigrid Orlowski, Martina Glante, Klaus Glowatzki, Renate Gericke and Angelika Gregror (clean-room teams), and by this everybody of IHP's clean room staff.

I want to thank the members of the process research department for their support in discussing, developing and adjusting all the single process steps: Dr. Steffen Marschmeyer, Dr. Thomas Grabolla, Dr. Harald Richter, Ulrich Haak, Dr. Achim Bauer, Dr. Beate Kuck, Dr. Klaus-Detlef Bolze, Katrin Blum and Thomas Morgenstern.

For the countless electrical measurements I want to thank Dr. Peter Schley, also for the many technical discussions about measurement related topics, Detlef Schmidt and Dr. R. Sorge.

For producing the numerous SEM pictures I want to thank Dr. Wolfgang Höppner, Heike Pfeiffer, Renate Naumann, Gabriele Morgenstern and Monika Döppner.

For doing the preparation of the TEM images I want to thank Dr. Petr Formanek and Dr. Günther Weidner.

I want to thank Christoph Wolf for the time he invested in preparing the complex test programs for the functional testing of the 1-Mbit memory and for doing the functional testing itself.

I want to thank Prof. Dr. Rolf Krämer and Dr. Michael Methfessel for the discussions regarding the role of embedded flash memories in a SOC environment and the required specifications.

I want to thank Dr. Biswanath Senapati for the work related to the electrical modeling of the flash cells and of the high-voltage MOS transistors.

I want to thank Dr. Valeriy Stikanov, Alex Gromovyy, Andriy Hudyryev from the NTU Kiev for the very nice cooperation and their work on the circuit design of the 1-Mbit memory.

Finally I want to thank Dr. Dag Behammer, who stands at the beginning of this work, as he has encouraged me in my decision to join the IHP for working on my dissertation, and who has over all been of great influence in evoking my interest in the field of microelectronics.

| 1. Introduction                                           | 1  |

|-----------------------------------------------------------|----|

| 2. The chosen embedded NVM concept                        | 5  |

| 2.1. Non - volatile memories                              | 5  |

| 2.1.1. Floating gate memories                             | 5  |

| 2.1.2. Nitride trap memory                                |    |

| 2.1.3. Advanced memory concepts                           | 7  |

| 2.2. Embedding flash memories                             | 8  |

| 2.2.1. FLOTOX                                             |    |

| 2.2.2. ETOX <sup>TM</sup>                                 | 9  |

| 2.2.3. HIMOS <sup>TM</sup>                                | 10 |

| 2.2.4. Superflash                                         | 11 |

| 2.2.5. Single poly cells                                  | 11 |

| 2.3. The chosen memory concept                            |    |

| 2.3.1. Cell operation                                     |    |

| 2.3.2. Array operation                                    | 14 |

| 3. The Flash / BiCMOS Process Integration Scheme          | 16 |

| 3.1 The baseline BiCMOS process                           | 16 |

| 3.2 Flash Memory Integration                              | 18 |

| 3.2.1. Integration scheme                                 |    |

| 3.2.2. Fabrication of the floating gate memory transistor |    |

| 3.2.3. The 2-transistor cell                              |    |

| 3.2.4. The split-gate cell                                |    |

| 3.2.5. High voltage MOS transistor integration            |    |

| 4. Process Implementation                                 | 30 |

| 4.1. Geometrical Results                                  | 30 |

| 4.1.1. Flash Cells                                        |    |

| 4.1.2. High voltage transistors                           |    |

| 4.2. Important process steps and process parameters       | 37 |

| 4.2.1. The tunnel oxide                                   |    |

| 4.2.2. The interpoly oxide / HVMOS gate oxide             | 39 |

| 4.2.3. The Flash p-well and the HVMOS wells               |    |

| 4.2.4. Floating gate etching                              |    |

| 4.2.5. Control gate etching                               |    |

| 4.2.6. Control gate lithography: anti reflective coating  |    |

| 4.3 Process impact on CMOS and HRT                        | 45 |

| 5. Device Characterization                                      | 48  |

|-----------------------------------------------------------------|-----|

| 5.1. Flash memory cells                                         | 48  |

| 5.1.1. The tunnel oxide                                         |     |

| 5.1.2. The interpoly oxide                                      |     |

| 5.1.3. Static characteristics of the flash cells                |     |

| 5.1.4. Transient behaviour of the flash cells                   |     |

| 5.1.5. Flash cell reliability                                   | 65  |

| 5.2. High voltage MOSFETs                                       | 72  |

| 5.3. BiCMOS devices                                             | 74  |

| 5.3.1. CMOS transistors                                         |     |

| 5.3.2. SiGe:C HBT                                               | 75  |

| 5.3.4. Modularity of the technology                             | 76  |

| 6. Full Circuit Demonstration                                   | 77  |

| 6.1. Building blocks and memory organization                    | 77  |

| 6.2. Functional testing                                         | 79  |

| 6.2.1. Test sequence and results                                |     |

| 6.3. Summary of the memory chip functional testing              | 83  |

| 7. Summary and Conclusions                                      | 84  |

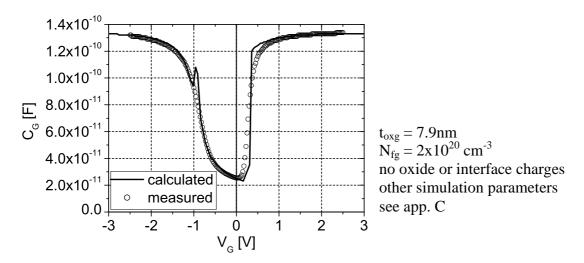

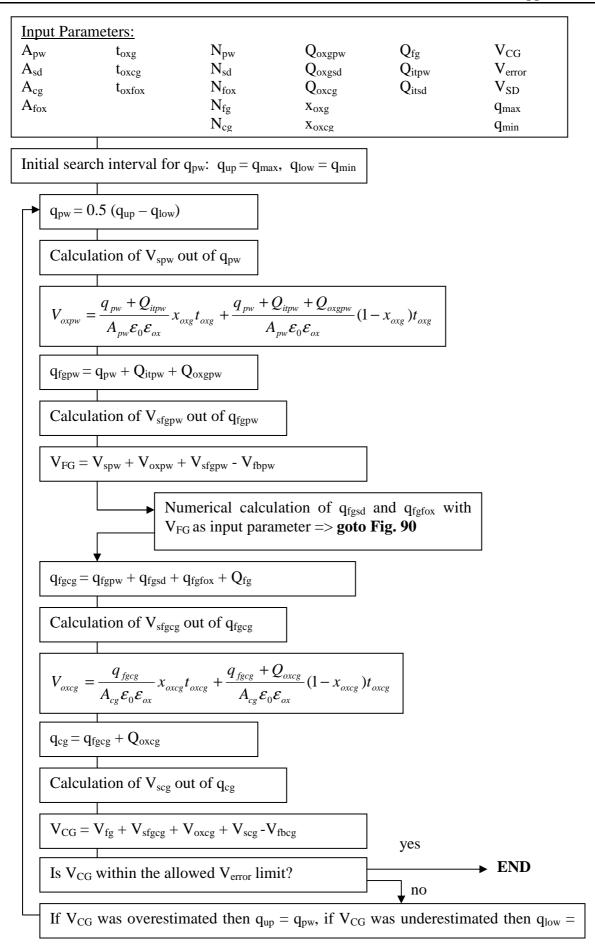

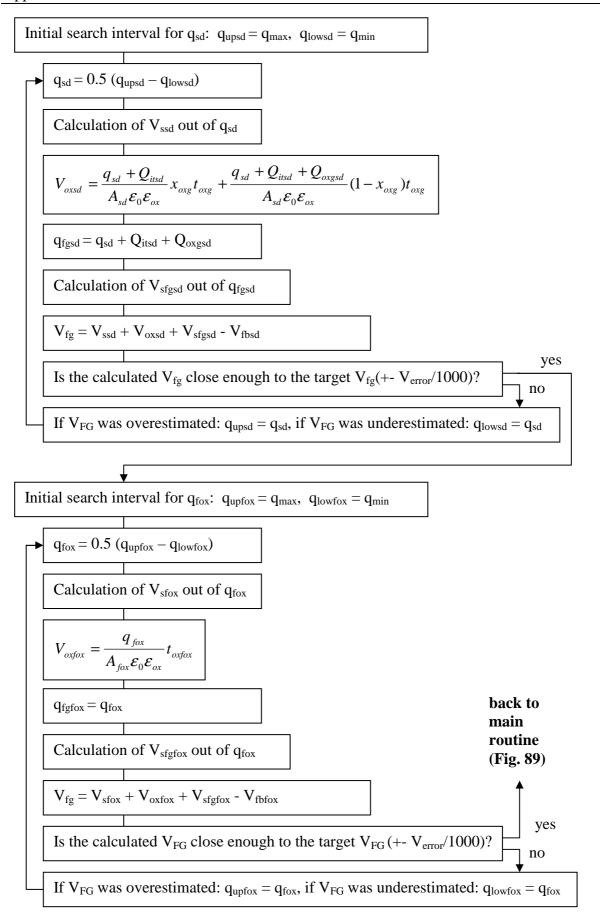

| Appendix A: Calculating the transient cell behaviour            | 87  |

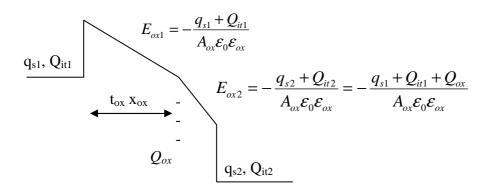

| Calculation of the oxide electric field                         | 87  |

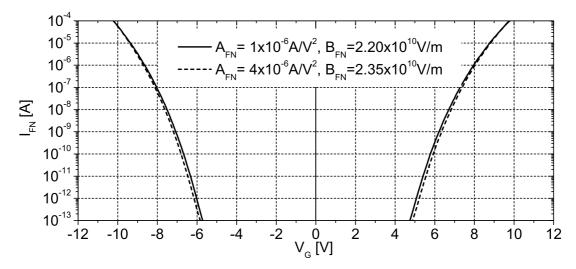

| The current through the tunnel oxide: FN and SILC               | 93  |

| The current through the interpoly oxide: modified FN tunnelling | 95  |

| Transient simulation                                            | 96  |

| Appendix B: Oxide Charge Extraction                             | 98  |

| Appendix C: Summary of Simulation Parameters                    | 101 |

| Appendix D: Dimensions of the Test Devices                      | 102 |

| Appendix E: Determination of V <sub>T</sub> and t <sub>OX</sub> | 103 |

| List of Abbreviations                                           | 104 |

| List of Symbols                                                 | 107 |

| Physical Constants and Material Parameters                      | 110 |

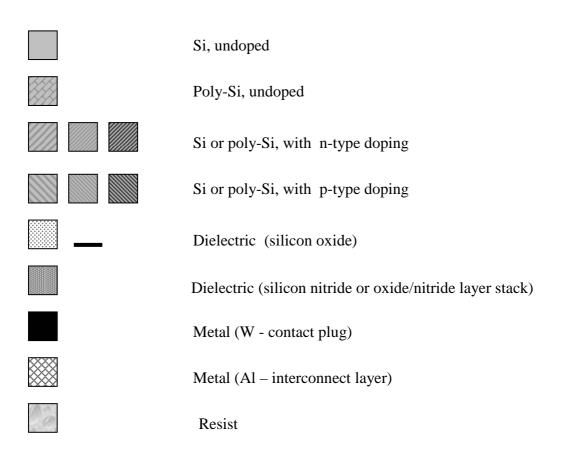

| Legend: Cross Section Views | 111 |

|-----------------------------|-----|

| Legend: Layout Views        | 111 |

| Index of Figures            | 112 |

| Index of Tables             | 118 |

| References                  | 119 |

| Publications                | 125 |

| Index                       | 126 |

## **Chapter 1**

## Introduction

Today's SiGe:C BiCMOS technologies are key enablers for single chip wireless and broadband communication systems. They combine high performance RF-bipolar transistors required for analogue functions, e.g. wireless data transmission, with VLSI CMOS for digital data processing. A cost effective process technology makes this functionality feasible for the consumer market. We see today, for example, a rapidly growing spectrum of wireless applications, starting from mobile phones, Bluetooth or WLAN up to wireless sensors or sensor networks, which are in return drivers for technology development. This dissertation describes for the first time in detail the integration of a suitable embedded flash memory module into such a SiGe:C BiCMOS process technology.

The SiGe and subsequently the SiGe:C HBT pushed the silicon technology towards high frequency applications, which were earlier covered by costly III-V-semiconductor based processes [1][2], thus making RF-applications available for a mass market which were only niche products before. Additionally, the compatibility with VLSI CMOS allowed the combination of dense digital with analogue functions and paved the way for complete single chip solutions [3]. Research directions are on the one hand improving the SiGe-HBT itself towards higher frequencies, thus principally demonstrating the potential of this material, and on the other hand developing less complex process technologies compatible with standard CMOS. Besides SiGe BiCMOS for highest frequencies also Si-only BiCMOS or RF-CMOS technologies are being developed for similar applications.

Many research and development activities are going on to further combine different components on the same chip, e.g. high quality passives (inductors, capacitors, resistors or transmission lines), high voltage power MOS-devices (LDMOS), different kinds of memories (SRAM, DRAM, NVM), up to micromechanical components (MEMS) and sensors. The main reasons for this system-on-chip integration (SOC) [4], away from multi-chip solutions, are saving costs, reducing size, saving power (less output drivers), enhancing reliability, optimizing the design of clock, bus and control signals, reducing electromagnetic interferences, at board level, and, especially for embedded memories, enhancing system flexibility (by reconfigurable non-volatile memories), and achieving faster access times (reduced capacitive coupling) [5]. This has to be bought by more complex process technologies, issues like interference of the integrated components (e.g. noise problems) and complex functional testing requirements.

In the special case of mass market wireless communication systems, which are often battery-driven portable applications (e.g. mobile phones), cheap process technologies in terms of number of required mask levels and number of process steps are needed, which offer the required RF-performance and allow designing circuits with low power consumption. These boundary conditions are also valid for all additionally integrated components, and have thus also a big influence on the choice of a concept for an embedded memory.

For embedded non-volatile memories the most mature technology today is the floating-gate flash memory. The information is stored by charging an isolated piece of silicon in a MOS-

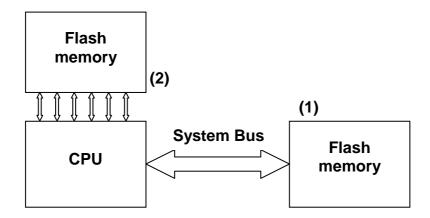

**Figure 1:** Flash memory incorporation in a System-on-Chip, (1) communication via system bus, (2) direct memory access by the CPU

transistor-like memory cell. The advantage of this concept is the CMOS compatibility, as no new materials or new kinds of process steps are needed. Much work was done understanding the reliability issues, scaling the cell size, reducing the operation voltage (which is significantly higher than CMOS operation voltage due to the high electric fields needed for cell-programming), or enhancing the memory's speed. Since the further development in all of these areas appears to reach some limits, more research was done in the last years to develop alternative memory concepts (SONOS, FeRAM, MRAM, PCM, etc.), which means in most cases investigating new materials and their process integration. These technologies are emerging and will in future take over the mainstream position of the floating gate embedded flash memory.

Floating-gate embedded flash memories are offered today in different forms by most Sifoundries as an optional module for their CMOS and also RF-CMOS processes, and semiconductor companies offer ICs with integrated NVMs. The combination of a Si-only BiCMOS process with an embedded flash memory is reported [6][7]. The integration of an embedded flash memory into SiGe:C BiCMOS is a consequent development, but not yet established. No literature is available on the process integration issues, and, to my knowledge, only one company has announced a SiGe process with NVM option to be available in future [8], but yet without further specification.

As SiGe:C applications evolve from mainly RF products to real BiCMOS products, which make use of the VLSI CMOS possibilities, memories ranging from low density (a few byte, e.g. non-volatile registers) up to medium density (~Mbit, e.g. for operation system storage) are required. The embedded flash process technology needs to produce cells that fulfil the size and performance requirements for such a memory, allow memories operating at low supply voltages and with low power consumption, and add only low additional cost to the process. An important requirement is the read access time. Fig. 1 shows two ways of how a flash memory can be incorporated into a system. The CPU can communicate with the flash memory via the system bus (1) or be directly connected with the flash memory (2). In the first case the speed requirements are more relaxed, while in the second case the flash memory should be readable at the clock frequency of the CPU. This makes, for embedded applications, the read access time more critical than other memory parameters. A modular integration scheme with low impact on the original CMOS and HBT devices would be favourable, e.g. for reusability of libraries.

This dissertation describes the development and characterisation of a process technology for an embedded floating-gate flash memory within a SiGe:C technology platform. The baseline process is a fully featured SOC SiGe:C RF-BiCMOS process developed at the IHP microelectronics research institute [9]. It consists of an industry standard  $0.25\mu m$  CMOS part and different integrated high performance SiGe:C HBTs. It is optimized for cost effective processing, e.g. different HBTs are integrated with only one mask level on top of the CMOS part. The flash memory integration is done with the main targets of achieving a process with low added cost and allowing memories with low power consumption, while cell size and performance need to fulfil the boundary condition of realizing up to Mbit memories.

The low cost issue is addressed by a process integration scheme with a low number of additional mask steps. This is achieved by the choice of the flash cell concept and by sharing masks and process steps for different purposes.

The target of low power consumption is addressed by the memory concept. Cells with a Fowler-Nordheim (FN) programming scheme were chosen, having intrinsically low power consumption during write and erase operations.

An additional task is the realization of devices capable of handling the required voltages for cell programming. These are well above the standard CMOS supply voltages, especially for FN-writing. A concept for integrating high voltage MOS transistors is presented, again targeting low added processing cost.

One more goal is to reduce the impact on the original CMOS and HBT devices as much as possible, which results in a modular process, to be able to offer an optional embedded flash memory only on demand.

The primary result of this dissertation project is the successful realization of a process technology for integrating an FN-programmed, floating gate embedded flash memory into the  $0.25\mu m$  SiGe:C BiCMOS process of the IHP. The integration of flash cells and high voltage devices is done with 4 mask levels on top of the baseline BiCMOS flow, which is among the lowest numbers for embedded FN-programmed cells reported so far. The process implementation has been investigated geometrically by means of SEM and TEM. The different newly developed devices have been characterised electrically. The results indicate that the process is capable of fabricating devices with the required performance. To demonstrate the feasibility of the process for fabricating medium density memories, a 1-Mbit circuit has been demonstrated in cooperation with the Technical University of Kiev.

The dissertation was done as a research project at the IHP microelectronics research institute, using the process technology and characterisation facilities of the IHP. I acted as project leader and was working on myself on all of the process integration issues. The IHP process research department, where the single process steps were developed, supported my work, as well as the characterisation department, where the measurements were performed, the clean-room staff, who prepared the wafers, and the CAD department of the Technical University of Kiev, who worked on designing the 1Mbit memory chip based on the developed technology. Results of this work have been published at the ICM 2004 [10]. The complete SOC BiCMOS technology, including embedded Flash, has been presented at the BCTM 2005 [11].

### The thesis is structured as follows:

#### **Chapter 1**: Introduction.

**Chapter 2** briefly introduces the field of non-volatile memories, then gives an overview of existing embedded non-volatile technologies and finally describes the fundamentals of the chosen memory concept, from single cell functionality to memory-array operation.

**Chapter 3** explains the process integration scheme. Starting with a presentation of the baseline BiCMOS process, the newly developed additional process modules for integrating the flash cells and the peripheral high-voltage devices are described and discussed in detail.

Chapter 4 presents the results of implementing the proposed technological process flow in the  $0.25\mu m$  pilot-line of the IHP. A geometrical analysis of the different devices is presented, followed by a discussion of important process steps, as well as the impact of these steps on the original BiCMOS devices.

**Chapter 5** presents the results of electrical characterization of the individual devices. DC and transient characteristics of the flash cells are shown and discussed, also with respect to their dependence on important technological parameters. The results of basic reliability investigations done at single memory cells are shown. A DC characterisation of the high voltage MOS transistors is done. Finally the impact o the flash memory integration on the DC characteristics of the CMOS transistors and the HBT is discussed.

**Chapter 6** shortly introduces the 1Mb demonstrator circuit and shows the most important results of functional testing.

Chapter 7 closes this work giving a summary and conclusions.

## **Chapter 2**

## The chosen embedded NVM concept

This chapter gives a brief introduction into the field of non-volatile memories, describes examples of technologies for embedded flash memories, before explaining more in detail the chosen memory concept. The aim is to range the chosen memory concept within the field of existing embedded non-volatile memories. The principles of different approaches are introduced and discussed. A more detailed description of the different memory concepts can be found in textbooks [5][12][13], review papers [14][15][16][17][18][19][20][21], and the respective specific publications given below.

For easier understanding of layouts and schematic cross section views please refer to the respective legends.

#### 2.1. Non - volatile memories

Non-volatile memories are memories that keep their information without regularly refreshing their contents (unlike DRAM) and without a power supply connected (unlike SRAM). Two important performance parameters are the retention (-time) and the endurance. The retention states how long the information can be stored. This refers to the fact that the information is lost after some time, which is in floating gate memories due to electrons leaking off the floating gate. Typically a retention time of 10 years is specified. The endurance of a memory cell says how often the contents of a memory cell can be changed. This refers to the fact that each programming process of a cell leads to some degradation of its characteristics and can be done only a limited number of times. For floating-gate memories the limitation is given by the degradation of the tunnel-oxide caused by electrons passing through it. Typical values are  $10^5$  maximum allowed write / erase cycles.

## 2.1.1. Floating gate memories

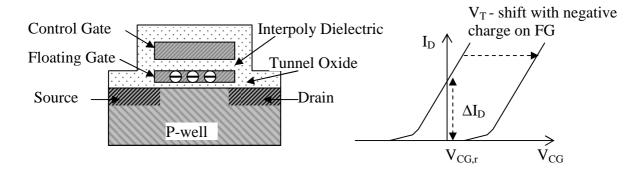

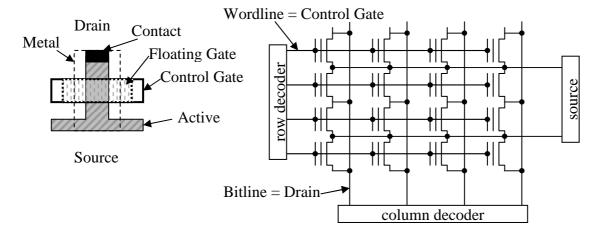

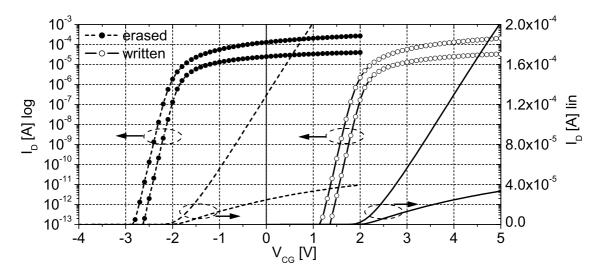

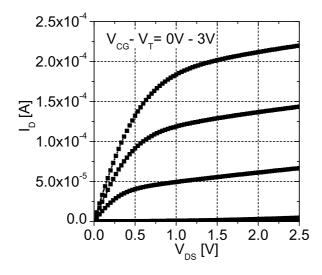

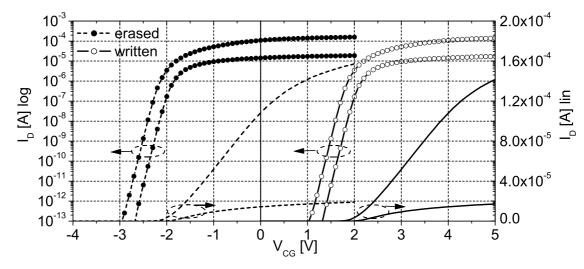

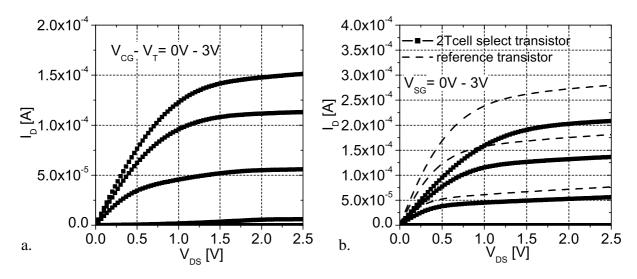

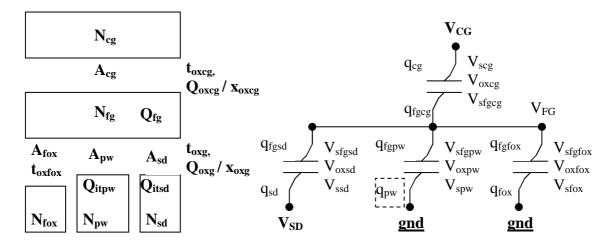

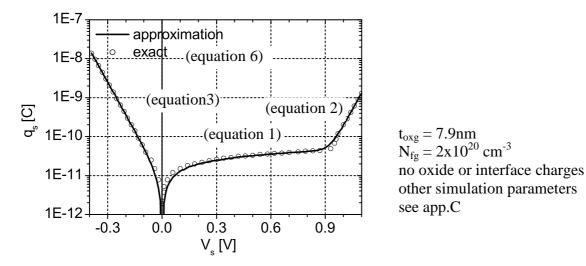

These are today's mainstream non-volatile memories. A schematic cross-section and characteristics are shown in Figure 2. The information is remembered by the charging state of an isolated piece of silicon, the floating gate (FG), which is placed between a control gate (CG) and a channel in the silicon substrate or well area. This structure forms a MOS-like transistor (usually n-Type) whose threshold voltage  $V_T$  is determined by the amount of charge on the floating gate. The  $V_T$ -shift is detected by measuring the change in the drain-current at a control-gate voltage  $V_{CG,r}$ . The voltage applied to the control gate is capacitively coupled to the floating gate via the interpoly-dielectric. This coupling is determined by the control-gate coupling ratio  $k_{Cg}$ , being the ratio of the CG/FG capacitance and the FG/"rest of the world" capacitance. A high coupling ratio is usually favourable, as high FG-potentials are needed to get the required electric field for cell programming.

The floating gate's history goes back to UV-erasable EPROMs [22], then the invention of the electrically erasable EEPROM [23], and subsequently the flash-EEPROM [24], which allowed larger memories due to a reduced cell size, and introduced this technology to a broad market in the late '80s, after its reliability was demonstrated [25].

Figure 2: Schematic cross-section and characteristics of a floating gate memory transistor

The first differentiation that can be made is between (full feature-) EEPROM and Flash (-EEPROM) memories. In EEPROMs every single byte can be written and erased separately. In Flash memories only the writing is on byte level, while the erase operation is performed for all cells of a defined memory sector simultaneously. For selecting a single cell in EEPROMs, a select transistor is required in series with the actual memory transistor in every cell, leading to the two-transistor cell structure. Due to their larger cell size, EEPROMs are mainly used for smaller memory sizes and functions like parameter storage. The smaller cell size of the 1-transistor Flash memory cell, which in principle does not need a select transistor, leads to the feasibility of this technology for code and mass storage applications [14].

Programming of the cells, which means transferring electrons on or off the floating gate, is in most cases done by one of two different mechanisms, either Fowler-Nordheim (FN) tunnelling or hot-electron injection. At sufficiently high electric fields electrons overcome the oxide barrier by FN tunnelling. This mechanism can be used in both directions, getting electrons on and off the floating gate. FN tunnelling can be realized between the floating gate and the silicon substrate, either in a separate tunnelling area or in the channel area, from the floating gate to the source or drain, or between two poly-silicon layers. In the latter case it can be locally enhanced by a specially designed geometry. Hot-electron injection uses the possibility for electrons to gather enough energy in the lateral electric field at the drain side of the transistor to get over the oxide barrier, if the vertical electric field is also favourable for them to do so. Only a fraction of the total drain current is injected to the floating gate this way. The injection efficiency has been raised by optimized drain engineering, means like substrate enhanced injection (CHISEL [26]), and optimized cell architectures, e.g. split-gate cells for the so-called source side injection (see also below, section "HIMOS"), which divides the formation of the lateral and vertical electric fields to two separate gates, thus allowing optimization of the conditions for both separately. Hot-electron injection can only be used to get electrons onto the floating gate. Discharging is in any case done by FN-tunnelling. FN programming requires higher voltages, while hot-electron programming consumes more current. A comprehensive comparison, also with respect to the reliability issues of the different mechanisms, is for example given in [20].

Another difference between types of flash memories is the memory array's architecture. The most important are NOR and NAND arrays. The NOR array allows fast random access to each byte during writing and reading. The wordline connects all control gates of one row, while in the crossing bitline each drain is contacted by ½ contact (two cells share one contact). The sources are all connected together via (silicided) active areas. This is the widely used, so-called common ground NOR array (Figure 5, in the description of the ETOX memory below). In the NAND array a number of cells belonging to one bitline are connected in series [5]. This leads to very compact cells (no separate bit-line drain contacts are necessary), at the expense of a slow random access time, as the reading current has to be passed through all cells connected in series. Mass data storage, stand-alone Flash memories up to 8 Gb have been

realized in NAND architecture [27]. NOR type memories are used for code storage applications with medium density requirements. Due to the specific requirements (medium density and high speed), NOR is the main architecture for embedded memories. Other concepts like AND [28], AG-AND [29] or DiNOR [30] play in general only minor roles.

A big issue in floating gate memory devices is the reliability in terms of endurance and retention. This is also one main limiting factor for progress in cell scaling, operation speed and operation voltage scaling. For array functionality always the behaviour of the worst cell is important, making statistical measures necessary when investigating reliability. Much work has been undertaken to understand the physical background and optimize the memory cell structure, the operating conditions and the process technology in this respect. Major roles play the tunnel-oxide and the interpoly-dielectric. The tunnel-oxide has to be produced without defects. Then, its characteristics change with continued cell writing and erasing. Stressinduced leakage current (SILC) occurs with the generation of electron traps within the oxide, thus affecting the retention. The transient programming characteristics change due to oxide charge build-up within the oxide. The reading current decreases due to degradation of the Silicon/Oxide interface. Other, more recently investigated effects are statistical fluctuations in the tunnel-oxide conduction behaviour, which have especially an impact on cell-array functionality. All these effects limit the minimum allowed tunnel-oxide thickness, which in return has an impact on the other cell properties [31]. Typical tunnel-oxide thickness is 8-10nm. The interpoly-dielectric is in most cases an ONO layer-stack. One reason for this is a reduction of enhanced electric fields at corners of the floating gate. In such corner situations, which occur as the control-gate is formed over an already patterned floating-gate, an intentionally introduced charge-build-up at the oxide/nitride interface shields the geometry related field enhancement. This leads to a reduced poly-poly leakage and thus enhanced reliability. The higher dielectric constant of the ONO leads additionally to a reduced EOT, which has a positive influence on the coupling ratio. Typically the EOT is around 20nm; minimum values of 11nm have been reported. Cappelletti has presented comprehensive summaries on flash memory reliability at the IEDM in 1994 and 2004 [32][33]. Other general summaries are given in [34][35][36]. SILC and related effects are investigated in [37][38][39][40]. Investigation of interpoly-dielectric related issues can be found in [41][42][43][44].

#### 2.1.2. Nitride trap memory

This kind of memory distinguishes itself from the floating gate memory by storing electrons not in a single piece of silicon, but in discrete traps in a silicon-nitride layer or at the interface between silicon nitride and silicon oxide. It has the same transistor-like structure, where the charge-trapping layer or layer stack, placed between the control-gate and the channel, replaces the floating-gate. The concept is actually even older than that of the floating-gate cell, but it suffered for a long time from reliability problems and worse performance compared to floating gate cells. During the last years, as the floating-gate cell reaches its scaling limits, more research was done again in this area to overcome the obstacles. Advantages are, besides scalability, the relatively simple process integration (e.g. no second poly level is required) and the possibility to store 2 bits per cell by localized charge injection at source and drain. Advanced scaled layer stacks (SONOS – Silicon / Oxide / Nitride / Oxide / Silicon, and recently the introduction of high-k materials) enhance the performance of this technology[45][46]. Nanocrystal memories, where the charge is stored in small silicon dots embedded in an oxide layer, are a similar concept [47].

### 2.1.3. Advanced memory concepts

Driven by the known limitations of the floating-gate memory cell and by the idea of developing a "unified memory", being a memory that combines the advantages of the

different existing kinds of memories (short access times, small cell size, non-volatile, high/unlimited endurance, low power consumption, CMOS compatibility), research activities are in various directions today to explore new memory concepts. The main directions are FeRAM, MRAM and PCM. Some of these concepts have reached a level of first products or demonstrators [48]. For CMOS integration many open questions exist, mainly because of the new materials involved. For embedded memory application those concepts will be especially interesting, which are integrated in the backend-of-line part (metallization) of the fabrication process. This reduces the interference with the fabrication of the other active devices.

## 2.2. Embedding flash memories

Embedding of Flash memories into standard logic took place almost from the beginning, as required materials and process steps were compatible. First embedded memory processes, derived from the stand-alone EEPROM processes, were complex and thus costly. For the integration of memory cells and the required high-voltage devices 7-9 extra mask levels were needed on top of the baseline CMOS process [21]. For applications with low-density CMOS parts also modified Flash-memory processes with embedded CMOS capabilities have been developed [21]. With the upcoming demand for small to medium density NVM within complex CMOS devices, specific processes for embedded Flash memories have finally been developed with the goal to reduce the added process complexity and cost, while achieving the required performance. The number of additionally required mask levels could be reduced to 2-5 extra mask levels, depending on the properties of the baseline flow [49]. The single-poly cell approach for low-density embedded memories works with even less.

Some selected examples of important embedded Flash memory technologies will be described in following. The aim is to give an overview of the topic and what is going on in the world. More detailed information can be found in the respective references.

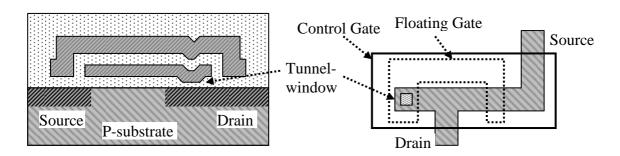

#### 2.2.1. FLOTOX

The FLOTOX cell is the original EEPROM cell with a 2-transistor structure [5][23]. It has been thoroughly investigated and modelled, e.g. [50][51], and is also used as embedded memory. It is both, written and erased by FN-tunnelling. A separate tunnelling-area (tunnel-window) outside the actual transistor part of the cell, located within the drain diffusion region, is formed for this purpose. The drawbacks of this concept are the relatively big cell area due to the select-transistor and the separate diffusion area, as well as the high number of mask steps and complex process technology for realizing an embedded EEPROM including high-voltage devices. The implementation in a modern CMOS technology, where the CMOS gate oxide is thinner than the minimum allowed tunnel oxide thickness, also needed a re-thinking

**Figure 3:** Schematic cross-section and layout of the FLOTOX memory cell (without select transistor)

|         | Source | Control- | Drain  |

|---------|--------|----------|--------|

|         |        | Gate     |        |

| Read    | GND    | 5V       | 1V     |

| Program | GND    | 12V      | 5 – 7V |

| Erase   | 5V     | -8V      | Float  |

Typical voltage values after [5]

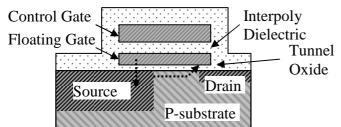

Figure 4: Schematic cross-section of the ETOX memory cell and operation conditions

of the concept. An example of a scaled process technology for a 0.35µm embedded EEPROM has been presented in [52]

## 2.2.2. ETOX<sup>TM</sup>

This approach, presented for the first time by Intel in 1988 [53], is called the "industry standard" flash memory cell [5][19]. It realizes a NOR, common ground, stacked gate, one transistor flash memory. It is programmed by hot-electron injection at the drain and erased by FN tunnelling to the source. A schematic cross section is shown in Figure 4, together with the operating conditions. Typical tunnel-oxide thickness is 8-10nm. An ONO stack forms the interpoly dielectric. Due to the different operation modes for write and erase, the source and drain junctions need to be optimized separately. The source is formed with a smooth profile, having a large overlap with the floating gate. This is to allow applying high erase-voltages. avoiding junction breakdown and high BTBT currents, which are the main reliability problem in this technology. The drain junction is steep and optimized for hot electron injection efficiency. The channel implant has to be optimized to get a compromise between the diverging requirements of the source and drain junctions. The structure is critical for shortchannel effects (due to the smooth and deep source junction), leading to scalability limitations. In modern technologies the erasing scheme has been changed to a channel erase scheme [54], where source, drain and substrate have the same potential and the current is distributed over the whole tunnel oxide area. High voltage transistors are formed separately by introducing an additional HV-gate-oxide and dedicated well implants. The arrangement of one-transistor cells in the common ground NOR array leads to a relatively compact cell layout as shown in Figure 5. Control gate and floating gate are formed self-aligned to each other. The technology has reached the 90nm technology-node in 2004 [55], and is thus one of the most

**Figure 5:** ETOX cell layout and cell arrangement in the common ground array

|    | S   | D    | CG   | PG  |

|----|-----|------|------|-----|

| W  | gnd | 3.3V | 0.9V | 9V  |

| DE | -   | 3.3V | -6V  | -6V |

| PE | -   | gnd  | 5.5V | -5V |

| R  | gnd | 1V   | 1.7V | gnd |

W: Write, DE: Drain Erase, PE: Poly erase, R: Read

**Figure 6:** The HIMOS cell: layout, schematic cross section and operating conditions [49]

advanced NVM technologies. To use it in combination with CMOS for wireless applications, in most cases the CMOS is embedded in the flash process [54][56], but also the other way, an ETOX-like embedded flash in CMOS, has been presented [57]. Issues for embedding are the complex technology (number of mask steps) and the current consumption at the drain during programming, with drain voltages above the usual supply voltage in modern technologies (which is a problem for low-voltage and low-power applications).

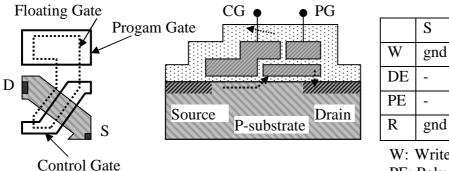

## 2.2.3. HIMOS<sup>TM</sup>

This is a real dedicated embedded flash technology. It has been invented at the IMEC in the early 90's, and was further developed and optimized until today [58][59][49][60]. The goal was to reduce the process complexity and the operating voltages, thus reducing both, the entry cost of the technology and the chip costs by reduced complexity of the periphery. This has been achieved by a new cell concept, which is a split-gate cell combined with an additional program gate. This structure significantly enhances the efficiency of the hot-electron injection, as it allows controlling the lateral and vertical electric field separately, and thus achieving the optimum injection conditions. The drain voltage could be reduced to a minimum value of 3.3V. The drain current during writing is low, because of the low voltage at the control gate (1V), leading to low power consumption. The source-side injection relieves the requirements to the drain junction as the injection point is now shifted to the source-side of the floating gate. The split-gate structure overcomes the overerase problems of 1-transistor cells (see below in this chapter, section 2.3.2. "Array operation"), and gives the possibility to have an erased V<sub>T</sub> well below 0V, which results in high reading currents and fast read access times. Also, a low excess charge in the written state has a positive impact on reliability. Erasing can be done by FN tunnelling to the drain or by FN poly-poly erase. As the drainerase leads to enhanced short-channel effects, similar to the ETOX source-erase, scaled technologies use the poly-poly erase option. The cell size is bigger than for ETOX, because of

**Figure 7:** Process flow for HIMOS integration in CMOS (after [60]). *Bold/italic* are additional masks needed

|   | S    | D   | CG   |

|---|------|-----|------|

| W | -5μΑ | 9V  | 1.7V |

| Е | gnd  | gnd | 12V  |

| R | 1V   | gnd | 1.7V |

W: Write, E: Erase, R: Read

**Figure 8:** The Superflash cell: schematic cross section and operating conditions [64]

the additional program gate. The control gate and floating gate are not self-aligned. The cell-layout, together with a schematic cross section and a table with operating conditions are shown in Figure 6. The arrangement in a "quasi virtual ground" array is described in [61], together with 1Mb circuit results. The CMOS integration only needs 2-5 masks, depending on the baseline process. An example is given in [60]. The process flow is shown in Figure 7. Here, 3 additional masks are needed, one for the HV-n-well, one for the tunnel oxide/high-voltage-oxide dual oxide process, and one for patterning the floating gate. The required medium voltage transistors for the 3.3V operation are already available in the process and are not counted. The first poly layer is here used for the floating gate and the high voltage transistors. The second poly forms the control gate, the program gate, the medium voltage transistors and the CMOS transistors. The process has been presented for the 90nm technology node [60], and concepts for 45nm have already been discussed.

## 2.2.4. Superflash

This is also a pure embedded flash concept. It was developed by SST [62], and is used by different companies (including TSMC) as CMOS embedded flash option. It is a NOR, common ground, split-gate, double poly silicon technology. It is written by source-side hot electron injection and erased by poly-poly FN tunnelling [63][64]. For erasing, an electric field enhancement is achieved geometrically by forming a tunnel-injector tip. This is achieved by using effects of corner shaping at oxidation of patterned poly silicon. A high drain/floating gate coupling is achieved by a dedicated implant forming a big drain overlap. This is needed for controlling the floating gate potential during erasing. Not much is published about the CMOS integration, or the high-voltage concept. The concept provides the advantages of source-side injection and the split-gate structure described above.

### 2.2.5. Single poly cells

In this technology a separate active area forms the control-gate. The integration is very simple (e.g. no second poly silicon level is required), at the cost of a bigger cell size, which makes it the technology of choice if only small memory density is needed. Fig. 9 shows the schematic cross section of one possible realization presented by IBM in 1994 [65], other solutions are presented in [66][67]. In the IBM cell, one part of the floating gate overlaps an n-well area, which acts like the control gate of a stacked gate cell. It can only be positively biased, because of the pn-junction to the substrate. Single poly cells can be programmed either by hot electron injection or by FN tunnelling. The process integration of the flash cell itself only needs one additional process module, the formation of an additional oxide layer, forming the tunnel oxide. This usually requires one lithographic mask level. Additional processing is usually necessary to make the required on-chip high-voltage handling possible.

|   | S     | D    | CG   |

|---|-------|------|------|

| W | 0V    | 5.5V | 6.5V |

| Е | float | 7.0V | 0V   |

| R | 0V    | 1.5V | 3V   |

W: Write, E: Erase, R: Read

**Figure 9:** Example of a single poly cell. Schematic cross section and typical operation conditions

## 2.3. The chosen memory concept

The embedded flash memory concept that has been chosen for integration into the RF-BiCMOS process is a uniform channel FN programmed, channel FN erased, stacked gate, double poly silicon, triple well, dual voltage, NOR flash memory.

The idea to use FN tunnelling for both, writing and erasing, in an embedded flash memory, especially for portable applications in the mobile communication field, has already been proposed in 1993 [68]. It describes a split gate cell structure, written by FN tunnelling to the drain and erased by FN tunnelling from the channel (states are switched here compared to e.g. hot-electron-written ETOX). In 1997 a similar concept has been proposed for a 1-transistor stacked gate cell [69], also applying drain-side FN tunnelling for writing and channel FN erasing. Uniform channel FN writing and erasing, thus achieving a completely symmetrical cell, has been published in 1999 [70], proposing a 2-transistor cell, arranged in a common ground NOR array, embedded in an 0.25µm CMOS process. In 2000 two publications, [71] and [72], at the same time proposed a uniform channel FN writing and erasing, 0.25µm, 1transistor embedded flash technology using a triple well that allows splitting the high voltage between control-gate and well. In [72] the STI is used to separate the wells of each bitline, to allow bit-by-bit control of writing and erasing. In 2002 an uniform channel FN written, channel FN erased, stacked gate, double poly silicon, 2-transistor, triple well, dual voltage, common ground NOR technology as low-voltage, low power embedded flash technology, implemented in a 0.18µm CMOS process has been proposed [73]. The publication describes it as the embedded flash technology of choice due to its robustness, reliability and cost effectiveness. It should be noted that the select transistor in the 2-transistor cell does not allow a full feature EEPROM usage of the cell (= bit-wise erasing) in the case of uniform channel programming. It is merely used during reading, where it leads to immunity against the overerase problem and to more freedom in the choice of the V<sub>T</sub>-window used for memory

The advantages of using uniform channel FN tunnelling for both, writing and erasing are the following:

- Uniform channel FN-tunnelling has the highest programming efficiency. Virtually all of the current flowing in the selected cell is the FG charging current. Only junction leakage and, in array operation, the leakage of the unselected cells reduce the efficiency. This results in a low power consumption during programming.

- FN tunnelling requires high voltages, but these can easily be generated on-chip by charge-pumps, also from low supply voltages, due to the low power consumption required for programming. This also results in a small area consumption of the charge-pump, compared to other flash memory solutions. The low voltage operation capability is an advantage compared to concepts using hot electron injection, especially for battery-driven systems.

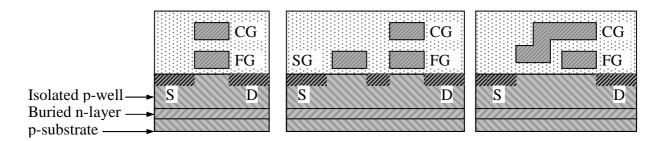

**Figure 10:** Schematic cross sections of the 1-transistor cell, the 2-transistor cell and the split-gate cells

- The low power consumption makes highly parallel writing of cells possible, which in principle allows reducing the average writing time to a fraction of the actual cell writing time.

- For uniform channel FN programming no separate optimization of the source or drain junction is necessary. This results in a reduced process complexity and thus easier and cheaper process integration. It also favours a modular integration scheme, which has an advantage because of reusability of libraries, thus saving technology entry costs.

- No enhanced short-channel effects, as observed in source or drain erasing schemes, are present.

- Channel erasing has good reliability properties, as one of the main issues, the BTBT at biased junctions, is not present

- The implementation of a triple well technology relieves the high voltage requirements on the devices involved, as the total programming voltage can be split between the control gate and the well/channel.

The low power consumption, low supply voltage operation and the low cost process technology match the requirements of portable, mobile communication applications.

The realization of a 1-transistor memory cell leads to a small cell size, while a 2-transistor cell or split-gate cell have the advantages of

- overerase immunity

- the possibility of low voltage reading without word line boosting, as required in other technologies. This is because the erased V<sub>T</sub> can be low, even below 0V in this case, leading to high reading currents at low control gate voltages.

- a reduced complexity, and thus reduced area of the peripheral circuitry [73].

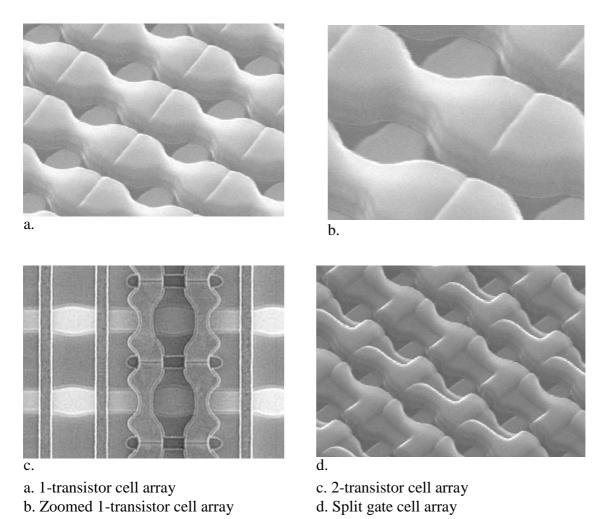

The developed process technology allows the formation of all three types of memory cells, 1-transistor, 2-transistor and split-gate cells. Schematic cross sections are shown in Figure 10. A NOR configuration of stacked gate cells allows realizing medium density memories (several Mbit) with fast random access times, as required by the targeted applications.

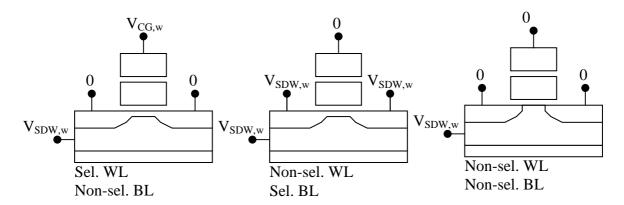

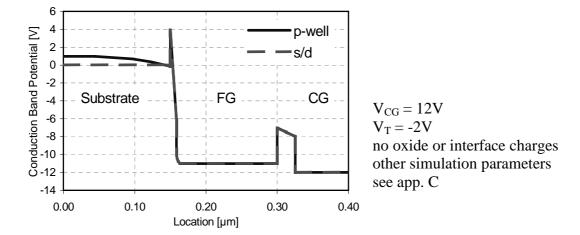

## 2.3.1. Cell operation

The applied voltages in write, erase and read mode are shown in Figure 11. The principal functionality is the same for all of the three cell types, thus only the 1-transistor case is shown. All voltages are given with respect to the substrate. For **writing**, a high positive voltage  $V_{CG,w}$  is applied to the control gate and a high negative voltage  $-V_{SDW,w}$  is applied to the source, drain and isolated p-well simultaneously. Alternatively either source or drain can be floating. The buried n-layer is kept at 0V in this case. Under such bias conditions, a high positive voltage is coupled to the floating gate, depending on its charging state even higher than  $V_{CG,w}$  for erased cells ( $V_T$ <0V). An inversion layer is formed under the oxide and electrons start tunnelling from the channel to the floating gate in the whole tunnel oxide area. For **erasing**, a high negative voltage  $-V_{CG,e}$  is applied to the control gate, and a high positive voltage  $V_{SDW,e}$  is applied to the source, drain and isolated p-well simultaneously. The buried n-layer is on the

**Figure 11:** Operating conditions for channel FN programming; typical values:  $V_{CG,w} = -V_{CG,e} = -V_{SDW,w} = V_{SDW,e} = 6V$ ;  $V_{CG,r} = 0V$ ;  $V_{DS,r} = 1.5V$

same potential as the isolated well in this case. A high negative voltage is coupled to the floating gate, again possibly exceeding  $-V_{CG,e}$ , now in the case of written cells. The channel area is in accumulation, while the overlap areas of the source and drain with the floating gate are inverted. This again leads to a uniform tunnelling current through the tunnel oxide. A more detailed analysis of the programming kinetics is given in chapter 5 and appendix A. For **reading**, the control gate is biased with a voltage  $V_{CG,r}$  between the written and the erased  $V_T$  state, see also Figure 2. It must be as much as possible above the erased  $V_{T,e}$  to get a high reading current, but keep a safe distance to the written  $V_{T,w}$ , so that the current of a written cell is still low and its state can be correctly determined. The drain voltage should be as high as possible for high reading currents. The limit is given by the read disturb effect, which is an unintentional change of the floating-gate charging state during reading (soft-writing). It is typically specified that the cell's state should be safely kept for 10 years of continuous reading.

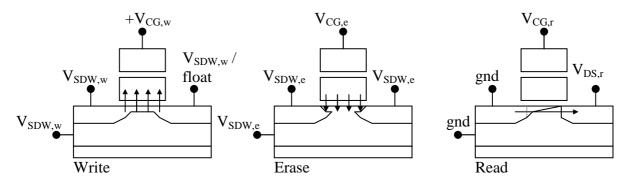

### 2.3.2. Array operation

The arrangement of the cells in an array and the operation conditions for writing and erasing are shown in Figure 12. Unlike usual common ground NOR, for each bitline the sources and drains have to be connected separately, leading to 2 metal lines per bitline. The reason for this becomes clear after a closer look to the operating conditions.

**Figure 12:** NOR array configuration and operating conditions for FN programmed memory cells. Thick lines mark selected lines.

Figure 13: Inhibit conditions for different cells in the array.

For writing, the wordline of the selected bit (here WL2) is set to a high potential and the drain and source lines of the corresponding bitline (here D1 and S1) are set, together with the isolated p-well of the whole array, to a high negative potential. This leads to the writing conditions described above for the selected cell. To prevent the other cells of WL2 from being written, their source and drain lines are set to 0V, and to prevent the other cells of bitline 1 from being written, their wordlines are set to 0V. These inhibit conditions leave also the unselected cells biased with some voltages. Three cases can be distinguished as shown in Figure 13, (1) cells in the selected wordline, in a non-selected bitline, (2) cells in a nonselected wordline, but in the selected bitline, and (3) cells in a non-selected wordline and a non-selected bitline. These voltages lead to the so-called write disturb effect, which is discussed in chapter 5. The different potentials of the selected and non-selected source lines do not allow the usual common-ground configuration. One exception is the 2-transistor cell, if the possibility is used to leave the source floating (which is possible as there is an inverted channel under the gate). If the select-transistor is able to keep the voltage difference between a selected and unselected bitline without too much leakage, a common ground configuration is theoretically possible (and used for example in [70]).

For **erasing**, simply all wordlines are biased with a high positive potential and all bitlines and the isolated p-well are on a high negative potential.

For **reading,** the selected wordline is biased with  $V_{CG,r}$ , the selected drain line with  $V_{DS,r}$  and the selected source line is grounded. The unselected source and drain lines are all grounded, as well as the isolated p-well. For the unselected wordlines the conditions are different for the different cell types. (1) For one transistor cells the unselected wordlines must be set to a voltage  $V_{off}$ , which must be well below the  $V_{T,e}$  of the erased cell, to prevent a current in non-selected cells of the selected bitline. Consequently, for the case of a  $V_{T,e}$  oV a negative voltage must be provided within the memory circuit for reading. At this point also the overerase problem of one-transistor cell-arrays becomes clear. If only one cell of a bitline has a  $V_{T,e}$  below  $V_{off}$ , its drain current is sensed when reading any other cell in the same bitline, leading to wrong reading results. (2) For the split-gate cell the  $V_T$  of erased cells can't be below the  $V_T$  of the select-transistor-part of the cell, which is above 0V, so the unselected wordlines are switched off by the select-transistor part of the cell when applying 0V to the control gate. (3) In a 2-transistor cell the current in unselected cells is switched off by the select transistor, also in the case of a negative  $V_{T,e}$  of the cell. The control-gates of the unselected cells as well as the select-gates are set to 0V.

Overerased cells do not disturb reading in split-gate or two transistor memories, making these solutions more robust. In general, the 2-transistor cell gives most freedom in choosing the  $V_T$ -window of all three cell-types.

## Chapter 3

## The Flash / BiCMOS Process Integration Scheme

This chapter presents the developed process integration concept. First, the baseline BiCMOS process is introduced followed by the description of the integration scheme for the flash memory devices, including the different options for memory cells themselves as well as the high-voltage MOS transistors. After a presentation of the overall process flow, the processing of the individual devices is explained more in detail.

For easier understanding of layouts and schematic cross section views please refer to the respective legends given in the appendix of this dissertation (p.111).

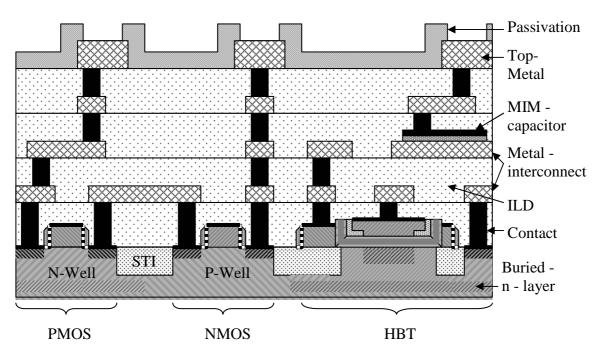

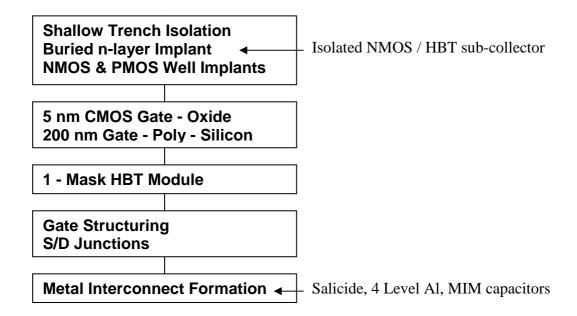

## 3.1 The baseline BiCMOS process

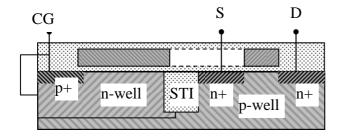

The baseline process is a 0.25 $\mu$ m BiCMOS process, consisting of an industry standard CMOS part, combined with a low-cost, high performance SiGe:C HBT module and different passive devices for RF circuit design [9]. Fig. 14 shows a schematic cross section. The main features are: STI isolation; a triple well approach (n-well, p-well and an isolated p-well formed by an implanted buried n-layer); MOS transistors for digital applications ( $V_{DD}=2.5V$ ), including the possibility of an isolated NMOS for improved signal isolation; a Co salicide process for reduced poly silicon resistance; low-cost integrated SiGe:C HBTs with epi-free, implanted collectors, allowing on the same chip 3 different HBTs ( $f_T/BV_{CEO}$  of 28GHz / 7.5V, 52GHz / 3.8V, 75GHz / 2.4V) by layout variation; poly silicon resistors of different sheet resistances; high-Q MOS varactors; a 4 level Al-interconnect system, including a 2 $\mu$ m thick top metal layer for high-Q inductor fabrication; and a 1fF /  $\mu$ m² MIM capacitor.

Figure 14: Cross section view of different devices of the BiCMOS technology

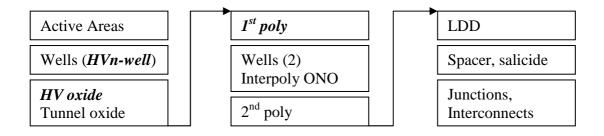

Figure 15: Schematic BiCMOS process flow without embedded flash memory

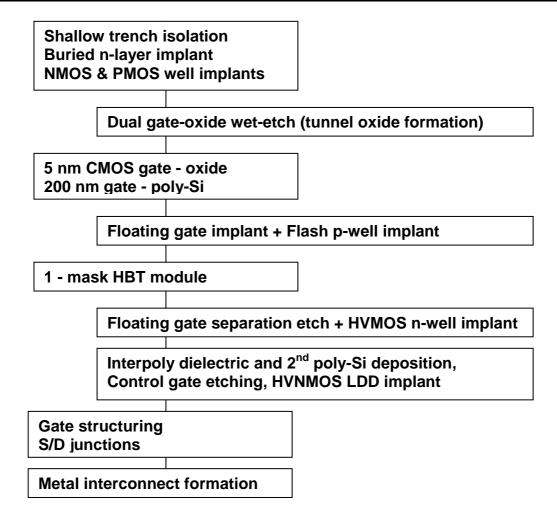

The principle process flow can be seen in Fig. 15. It starts with the formation of the shallow trench isolation by trench-RIE, oxide filling and CMP planarization. In a next step the different wells are implanted in the respective areas. A 5nm gate oxide is thermally grown, and a 200nm poly silicon layer is deposited, which form the gate stack of the MOS transistors. At this stage of the process the HBT is fabricated, requiring only one lithographical step. The HBT process is described below more in detail. After the HBT module the CMOS gates are formed. First the poly silicon is structured by RIE. After a poly silicon re-oxidation and the formation of sidewall spacers, the source and drain junctions are implanted. The silicon surfaces are silicided in a Co-salicidation process. Finally the interconnect system is produced by subsequent deposition of the interlayer dielectrics, CMP planarization, contact hole etching, contact filling, metal deposition and metal structuring. On top of the last metal layer a passivation layer stack is deposited and opened again by RIE on the contact pads. The complete process flow requires 19 lithographic mask steps. The CMOS part is a typical process sequence for industrial fabrication in this technology node, while the integration of the HBT is an advanced process for low cost, high-performance BiCMOS applications.

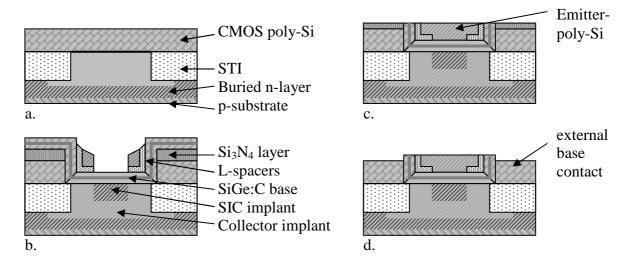

The description of the HBT module of [9] will be shortly repeated in following. The basic steps of the 1-mask HBT module are presented in Fig. 16. Fig. 16a shows the situation after the CMOS poly silicon deposition. The poly silicon layer fully covers the HBT area; STI defines the base area of the HBT and separates it from the collector contact area (not drawn in Fig. 16), which is connected with the intrinsic collector area under the base via the buried nlayer. The HBT fabrication starts with the deposition of an Si<sub>3</sub>N<sub>4</sub> protection layer. The HBT mask is used to remove the Si<sub>3</sub>N<sub>4</sub> and the gate poly silicon from the HBT regions by RIE, and to carry out a chain of P-implants, which form and adjust the collector doping. After removing the gate oxide from the base area by wet etching, the SiGe:C base and a low-doped poly-Si emitter layer are successively deposited by CVD. L-shaped inside spacers are formed and a SIC implantation is carried out (Fig. 16b). An in-situ n-doped poly-Si emitter layer is deposited. All silicon material is then removed from the Si<sub>3</sub>N<sub>4</sub> layer by CMP, thus isolating the emitter from the external base (Fig. 16c). After removing the Si<sub>3</sub>N<sub>4</sub> from the CMOS poly-Si by wet etching, the CMOS device fabrication is continued as described above. The state at the end of the HBT module is shown in Fig.16d. CMOS gate etching and PMOS S/D implants are used to complete the HBTs external base contact area later in the process.

- a. After CMOS gate oxide growth and CMOS poly deposition

- b. After Si<sub>3</sub>N<sub>4</sub> deposition, bipolar window etching, collector implant, SiGe:C epitaxy, inside L-spacer formation and SIC implant

- c. After emitter poly-Si deposition and CMP

- d. After residual Si<sub>3</sub>N<sub>4</sub> removal

Figure 16: 1-mask HBT module

The HBT fabrication leaves the regions outside the HBT in the same state as they have been before the module and adds only little topography, so the following CMOS steps can be performed without modification. The position of the HBT-module in the process flow ("HBT before gate" – integration scheme) minimizes the impact of the thermal steps during HBT formation on the MOS devices. This integration scheme is possible due to the C incorporation in the base layer, which leads to a reduced B out-diffusion and thus prevents degradation of HBT parameters by CMOS thermal steps, e.g. poly re-oxidation and S/D RTA.

## 3.2 Flash Memory Integration

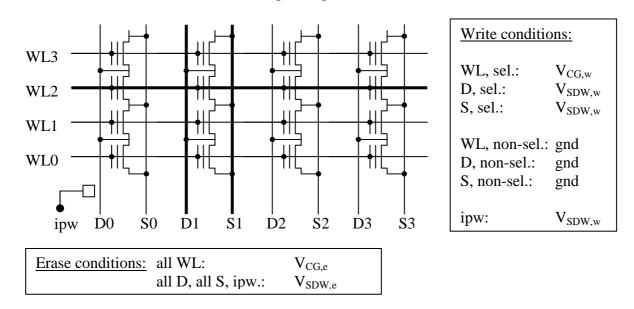

In following, the process steps for realizing the 4-mask-layer, modular integration of the flash memory will be described. After presenting the integration scheme, the process flow for the different possible flash cells and for the high-voltage MOS transistors is explained in detail.

### 3.2.1. Integration scheme

Fig. 17 shows the integration scheme for the flash memory module. The additional processing can be separated into 4 blocks, corresponding to the 4 additional lithographic mask levels needed to include the flash memory fabrication into the BiCMOS process.

The first block is carried out before the CMOS gate oxide growth, and is the formation of the tunnel oxide by a standard dual oxide process. This process consists of a masked removal of the thick oxide (tunnel oxide) outside of the areas of the later tunnel oxide by wet etching, before the thin oxide (CMOS gate oxide) is grown. Please note that, if the baseline process already has a dual gate oxide option with a suitable thick oxide thickness, the integration of the flash memory only requires 3 additional mask steps, as this block is not needed.

The second block is a masked chain of ion implantations for doping the floating gate and the flash p-well, which is used for both, the flash-cells and the high-voltage transistors. This is done before the HBT module is carried out, thus using the HBTs thermal steps for annealing the implantation damage.

The main structuring steps are carried out after the HBT module and before the CMOS gate formation. In the third block a masked RIE of the first poly silicon layer is done. This etching separates the floating gates belonging to one wordline from each other. The same etching step

Figure 17: Embedded flash memory integration scheme

is used to remove the first poly silicon layer from the HVMOS areas. Before removing the resist, the ion implantation of the n-well for the HVPMOS is carried out.

In the last block the interpoly dielectric layer and the control gate poly silicon layer are deposited and structured. Using the same mask, an LDD implant for the HVNMOS is done.

The process continues with the CMOS processing steps, which also do the self-aligned floating gate etching and the formation of the source and drain junctions of the memory cells and the high-voltage transistors, thus saving extra processing.

By the position of flash memory module in the overall process flow the impact on the CMOS devices is minimized, as the integration is completed before the CMOS gate formation. The integration after the HBT module minimizes the interference of HBT processing with flash memory processing, which could be a problem because of the flash cells' relatively high topology. This integration scheme takes benefit from of the above mentioned stability of the SiGe:C HBT to degradation to added thermal budget. A low cost process is achieved by using the same mask layers and process steps for different purposes, and by using CMOS process steps also for flash memory fabrication. Especially the fabrication of the HVMOS transistors does not require any additional mask layer.

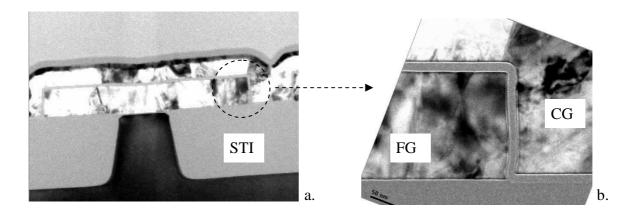

### 3.2.2. Fabrication of the floating gate memory transistor

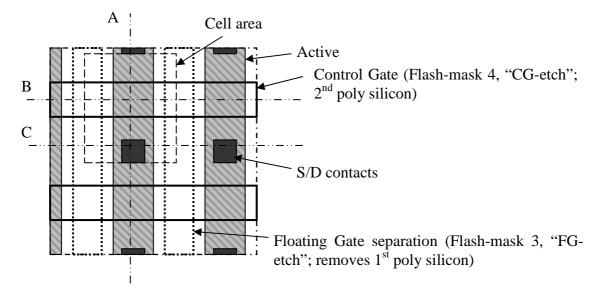

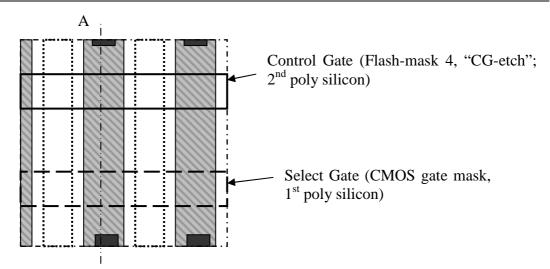

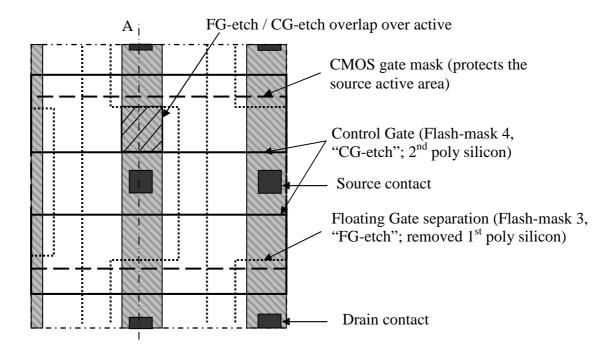

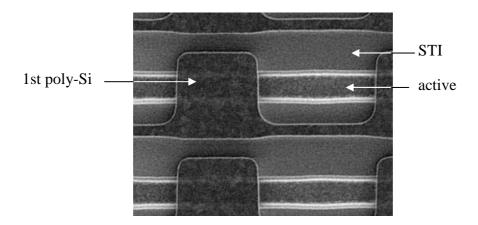

Fig. 18 shows the schematic layout fragment of a 1-transistor memory array. The following Figures 19 - 22 show cross section views at different stages of the process. The cuts are along line A in bitline direction, crossing the wordline; line B in wordline direction in the area of the control gate; and line C in wordline direction, but outside the CG area. In both directions (x

Figure 18: Schematic layout fragment of a 1-transistor cell array

and y) the chosen fragment of the array covers a distance of about 2 memory cells. Not shown are the metal interconnects, only the placement of the contacts is drawn in Fig. 18. The metal connection can, for example, be done in a way that a metal-1 line and a metal-2 line are drawn in parallel, one for connecting the sources, the other connecting the drains of the memory cells belonging to one bitline. The first two masks of the flash module are not drawn in Fig. 18, as the first mask (DGT) completely covers the flash cells, while the second mask (FImp) is open in the whole area of the flash cells.

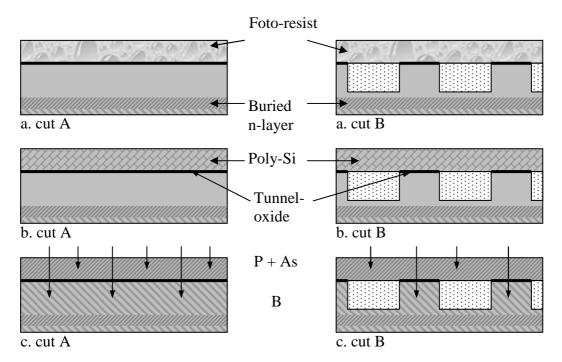

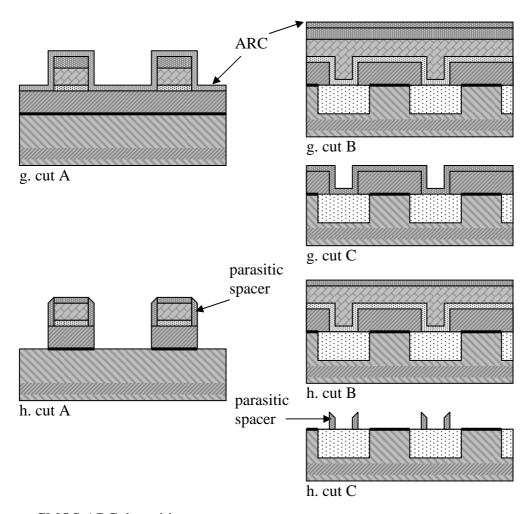

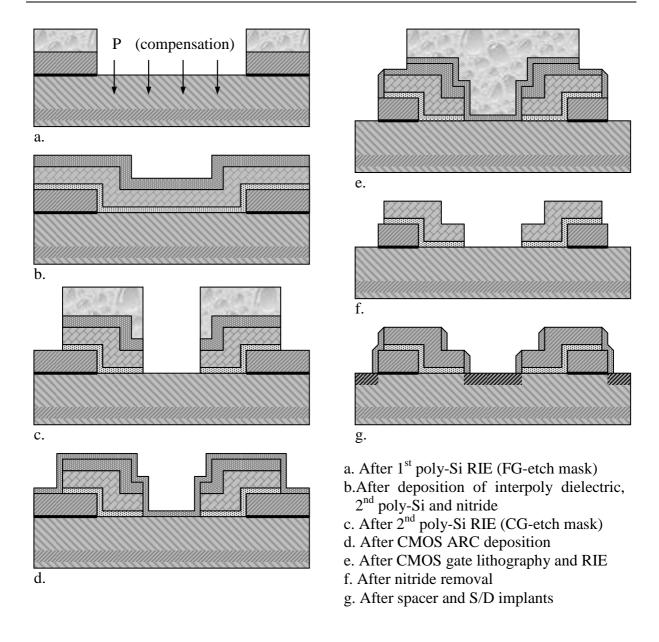

Figure 19 shows the application of the first two masks of the embedded flash process for cut

- a. Flash-mask 1 (DGT): dual gate-oxide wet-etch (resist open outside tunnel oxide areas)

- b. CMOS gate-oxide growth and gate poly-Si deposition (1<sup>st</sup> poly silicon layer)

- c. Flash-mask 2 (FImp): Floating gate and flash-p-well implant (resist covers areas outside flash cell)

**Figure 19:** Process flow for flash memory cell: flash-mask 1 (DGT) and flash-mask 2 (FImp); cut lines A and B according to Fig. 18

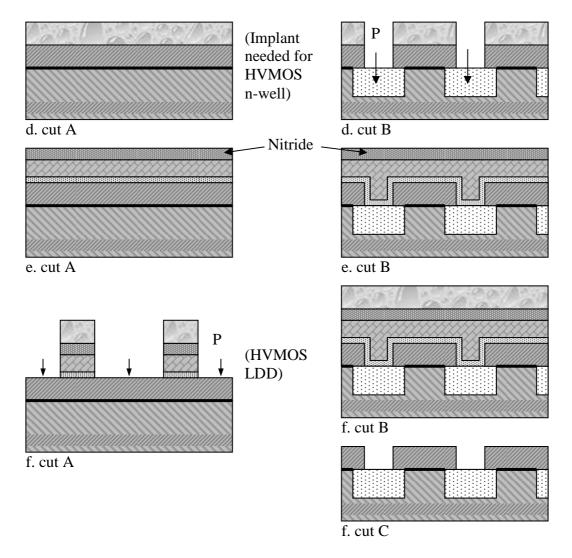

- d. Flash-mask 3 (FG-etch): floating gate separation etching

- e. Interpoly dielectric, second poly silicon and nitride deposition

- f. Flash-mask 4 (CG-etch): control gate etching

**Figure 20:** Process flow for flash memory cell: flash-mask 3 (FG-etch) and flash-mask 4 (CG-etch); cut lines A, B and C according to Fig. 18

lines A and B (C is the same as B at this stage). The STI has been formed and the well implants have been carried out. On the active areas an oxide has been grown that will become the tunnel oxide later on. The first resist mask (DGT) covers the active areas at the places where the tunnel oxide is formed, while all oxide is removed from the silicon surfaces of the other active regions in an HF-wet etching step. After resist removal and a cleaning step the CMOS gate oxide is grown. The tunnel oxide looses a bit of thickness during the cleaning and reaches its final thickness during the thermal gate oxidation. The first (CMOS) poly silicon layer is subsequently deposited.

The second resist mask of the flash module (FImp) covers all areas outside the flash cell array and protects them from the following ion implantations. A first ion implantation is done for highly n-doping the first poly silicon layer in the areas of the floating gate. As in this technology the floating gate is the same poly silicon level as the MOS transistor gates, this has to be a masked process, unlike in many other embedded flash technologies, where the MOS transistors are made of the second poly silicon layer. The same resist mask is used to do the well and  $V_T$  doping for the flash cells (flash p-well). The doping is done by a chain of B implantations of different doses and energies, resulting in a retrograde profile that provides a

- g. CMOS ARC deposition

- h. CMOS gate etch, self-aligned floating gate structuring

**Figure 21:** Process flow for flash memory cell: CMOS steps, gate etching; cut lines A, B and C according to Fig. 18

compromise between the requirements of a low  $V_T$  and punch-through immunity. The B implants are carried out through the first poly silicon layer, with energies ranging from 90 keV to 360 keV. This process block ends with the removal of the resist mask, leaving the wafer ready for the HBT module.

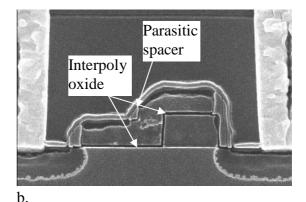

After completing the HBT module, which has no impact on the areas of the flash memory, besides thermal implant annealing, the flash fabrication is continued with applying the third flash mask (FG-etch). This mask is used to etch narrow slits in the first poly silicon layer to separate the floating gates that will later be covered by the same control gate (Fig. 20d, cutB). The etching can not be done using the CMOS gate etching mask, which is also used for structuring the 1<sup>st</sup> poly silicon layer, as the deposition of the interpoly dielectric and the second poly silicon is still to come. Some conflicts would appear later in the process (parasitic spacers etc.) if the MOS gates were already structured then. The distance of the slits defines the width of the floating gate (the length is defined later by self-aligned etching with the control gate). As indicated by the arrows in Fig.20d, cut B, an implantation is carried out after the etching. This is needed for the formation of the HVMOS transistors, and has no impact on the flash cells, as here it only goes into the oxide of the STI.

As a next step the interpoly dielectric is formed, using a thin thermal oxidation step, followed by a thermal, low pressure CVD oxide deposition and a thermal oxide-densification step. On top of the dielectric the second poly silicon layer is deposited. By using a conformal

- i. Nitride wet-etch (original step from BiCMOS flow)

- j. CMOS spacer formation; source and drain junction implants

**Figure 22:** Process flow for flash memory cell: CMOS steps, S/D junctions; cut lines A, B and C according to Fig. 18

deposition, the narrow slits between the floating gates are filled with poly silicon during this step, leaving a more or less planar surface. Finally, a silicon nitride layer is deposited. This layer is needed later in the process as hardmask for self-aligned floating gate etching during the CMOS gate RIE (Fig. 20e).

The fourth flash mask (CG-etch) is used to structure the second poly silicon layer. The RIE process consists of different steps for etching the silicon nitride hardmask and the poly silicon layer. By a long overetch, the poly silicon is removed out of the slits outside the control gate areas (Fig. 20f, cut C). Moreover the CMOS and HBT areas are cleared from the 2<sup>nd</sup> poly silicon during this step. The interpoly oxide is etched partly by RIE and partly by a subsequent HF cleaning step, in order to remove it also from the sidewalls in the FG slits. At this point also a shallow P ion implantation is carried out, as indicated by the arrows in Fig.20f, cut A. This is required for the HVMOS fabrication to form LDD extensions. The last block of the flash module ends with removing the resists mask. The regions outside the flash memory are now in the same state again as after the gate poly silicon deposition, which was before the second block of the flash memory integration (not counting the influence of the thermal steps and the HVMOS LDD implant; for a detailed discussion of the impact of the flash integration on the CMOS process see chapter 4.3.). The flash memory transistor is not finished yet. This happens during the following processing steps of the CMOS core.

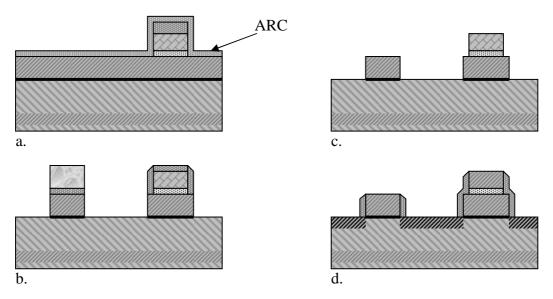

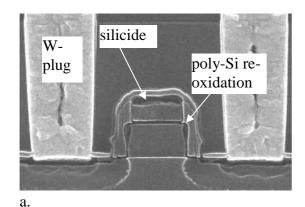

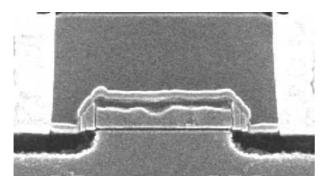

The CMOS gate processing starts with the deposition of an antireflective coating (ARC) (Fig.21g). The ARC is a silicon rich silicon nitride layer with adjusted optical properties. In the following gate RIE step, the flash cell is not covered by any resist. The formerly deposited

**Figure 23:** Schematic layout fragment of a 2-transistor cell array

silicon nitride hardmask protects the control gate during this step, and leads to a self-aligned etching of the floating gate. The gate length of the floating gate is larger than that of the control gate, due to spacers formed by the CMOS ARC layer (Fig.21h, cut A). These spacers also appear in the floating gate separation slits outside the control gate (Fig.21h, cut C). They will be removed later in the process (Fig.22i).

At this point a poly silicon re-oxidation is carried out in the CMOS flow, also affecting the memory transistor. All nitride layers, including the ARC on the CMOS gates, the parasitic nitride spacers and the hardmask on the floating gate are then removed by a wet etching step in phosphoric acid (Fig.22i).

The source and drain junctions are implanted after the formation of sidewall spacers (Fig. 22j). The spacers are produced by conformal oxide and nitride deposition, followed by an anisotropic RIE. The source and drain ion implantation is a combined As and P implant for the NMOS transistors and a B implant for the PMOS transistors. After an RTA step for dopand activation a salicide process forms a low resistance CoSi layer on the silicon surfaces. Finally the formation of the metal interconnect-system is carried out, forming the contacts, metal layers, MIM capacitors and the passivation.

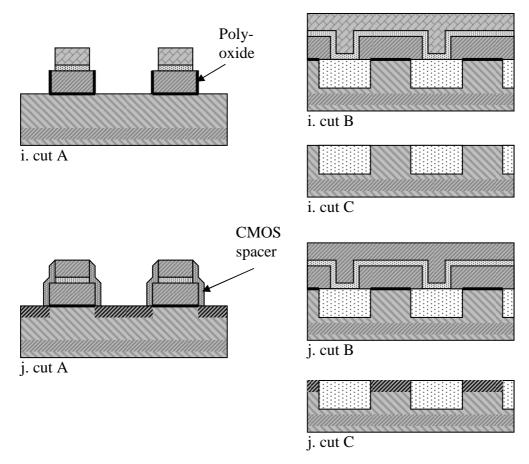

### 3.2.3. The 2-transistor cell

The schematic layout of the 2-transistor cell is shown in Fig. 23. The difference compared to the 1-transistor layout is the placement of the select gate (=CMOS gate mask) parallel to the control gate (=CG-etch mask), between the control gate and the source contact, resulting in a bigger cell size.

The fabrication of the 2-transistor cell is done with the same technological process flow as the 1-transistor cell; only the cell layout is changed. Fig. 24 shows the fabrication of the select transistor after the flash memory module has been completed. The control gate of the memory transistor has been structured at this stage of the process. The ARC for CMOS gate lithography has been deposited (Fig. 24a). In following the gate lithography is done and the select transistor's gate is etched together with the CMOS gates and the floating gate (Fig. 24b). The next steps are poly silicon re-oxidation, nitride removal (Fig. 24c), spacer formation and source / drain junction ion implantation (Fig. 24d).

The select transistor consists, like the CMOS transistors, of the first poly silicon layer only. It has the tunnel oxide as gate oxide and the same p-well and  $V_T$  implants as the flash cell. The latter makes the optimization of these ion implantation processes different compared to the 1-transistor or split-gate cells. This will be discussed more in detail in chapter 5.1.

- a. After all flash memory process modules and CMOS ARC deposition

- b. After CMOS gate etching

- c. After nitride wet-etching

- d. After spacer formation and S/D junction implantation

**Figure 24:** Process flow for 2-transistor cell: building the select transistor; cross section along line A (Fig. 23)

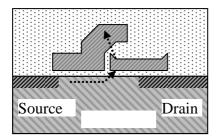

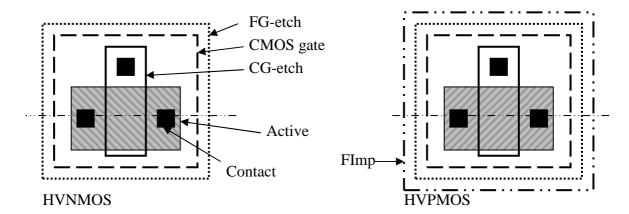

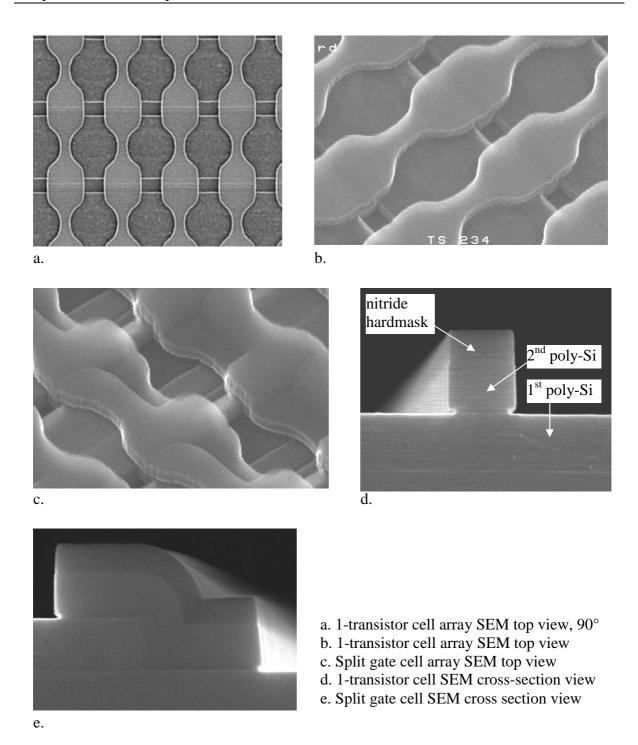

## 3.2.4. The split-gate cell

The schematic layout for fabricating a split gate cell structure with this process flow is presented in Fig. 25. By producing an overlap of the FG-etch and CG-etch masks in the memory transistor's channel area, the split gate structure can be achieved. The CMOS gate mask is needed in this case to protect the source area from the CMOS gate RIE. Cross

**Figure 25:** Schematic layout fragment of a split gate cell array

**Figure 26:** Split-gate cell process flow; cross sections along cut line A (Fig. 25)

sections of a cut along line A of Fig. 25, perpendicular to the wordline direction, are shown at different stages of the process in Fig. 26.

The tunnel oxide formation, floating gate ion implantation and flash-p-well ion implantation are done in the same way as for the 1-transistor cell. The floating gate etching mask ( $3^{rd}$  mask of the flash module, FG-etch) is opened here also in the active transistor area. The floating gate and the tunnel oxide are removed in this place (Fig. 26a). With the same mask a P-implant is carried out as indicated by the arrows, which is needed for fabrication of the HVMOS transistors. This implant also adjusts the  $V_T$  of the select transistor part of the split-gate cell, as it reduces the net doping (the P compensates the B partly). Fig. 26b shows the state after deposition of the interpoly dielectric layer, the  $2^{nd}$  poly silicon layer and the silicon nitride hardmask layer. The  $4^{th}$  mask of the flash module (CG-etch) is now applied, placed over the former edge of the FG-etch mask (Fig. 26c). The overlap of the CG-etch mask over the remaining floating gate produces the memory transistor part of the cell, while in the already etched area the select-transistor part is formed. The process continues with the CMOS process steps. The CMOS ARC layer is deposited (Fig. 26d) before the gate lithography and etching are performed. Here, the CMOS gate mask has to be placed over the cell's source

Figure 27: Schematic layout of the HVMOS transistors

area, where the 1<sup>st</sup> poly silicon layer has already been removed by the FG-etch, to protect the active layer from being unintentionally etched during the CMOS gate RIE (Fig. 26e). The next steps are silicon nitride removal by wet etching (Fig. 26f), the spacer formation, and the ion implantation to produce the source and drain junctions (Fig. 26g).

It should be noted that the CG-etch mask in this concept defines the total gate-length of floating gate + select gate. The adjustment of the CG-etch mask and the FG-etch mask with respect to each other defines the actual length (or the proportion) of both, which makes this a critical process parameter here, and special care must be taken to minimize the misalignment during the respective lithography steps. It should also be noted that the select transistor part is similarly constructed as the HVNMOS transistor described below, with the interpoly oxide layer as gate dielectric and a partly compensated flash p-well.

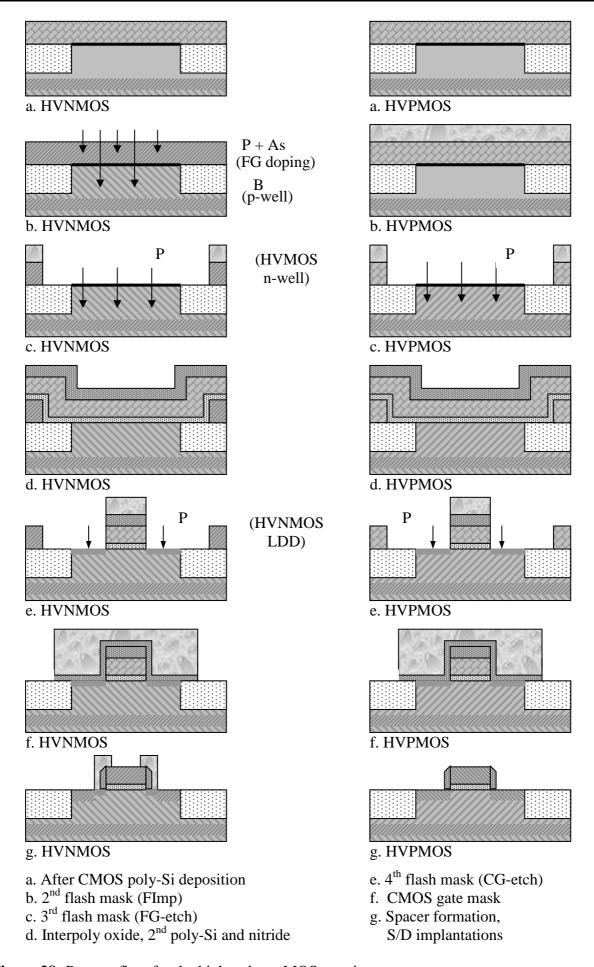

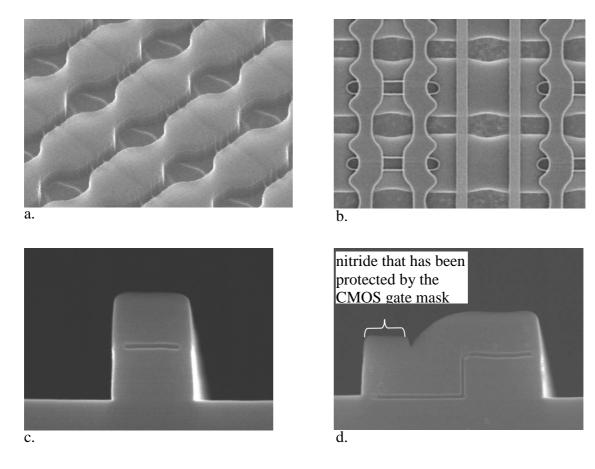

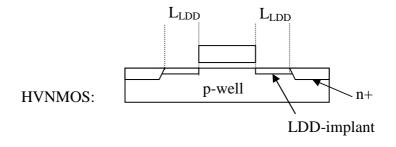

## 3.2.5. High voltage MOS transistor integration

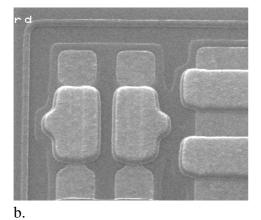

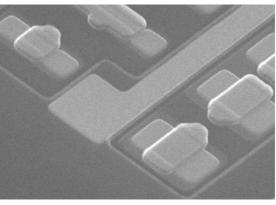

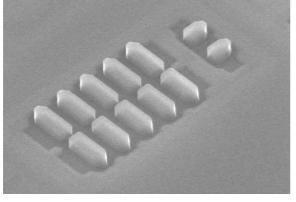

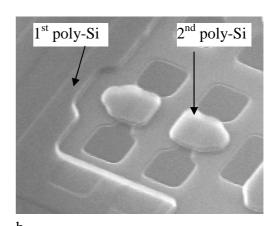

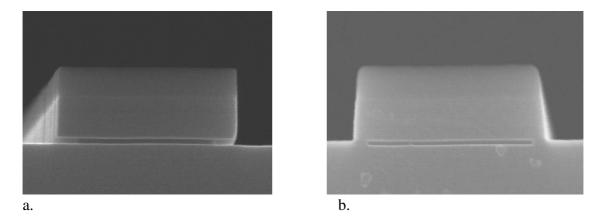

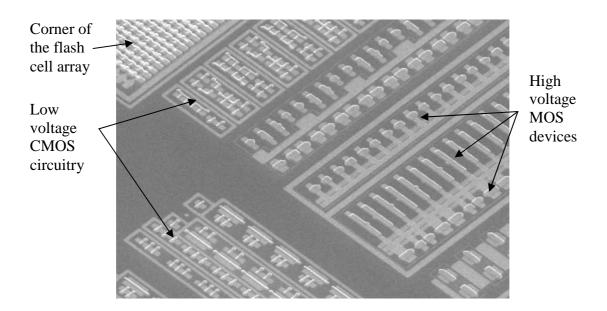

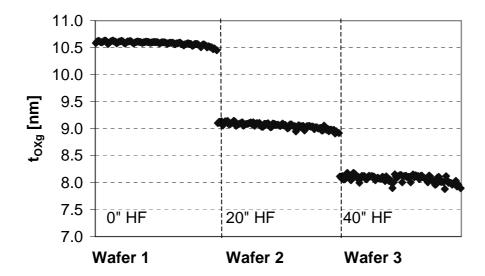

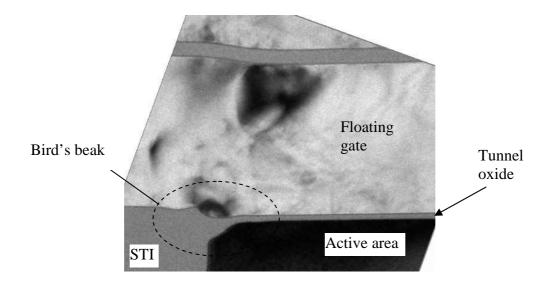

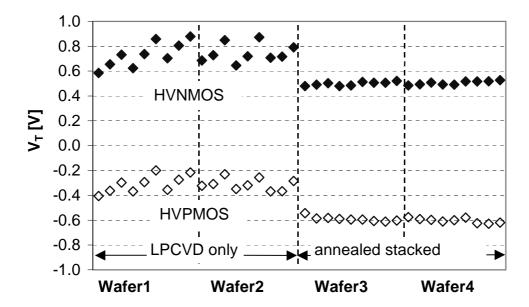

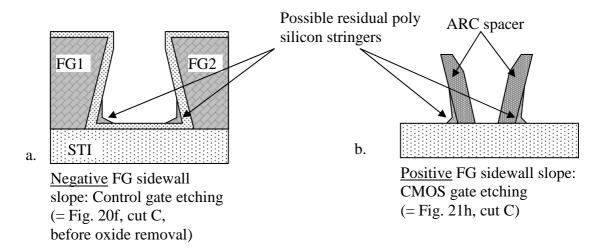

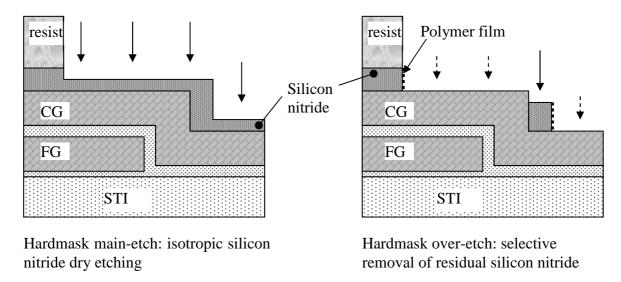

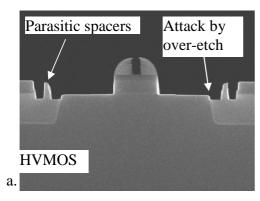

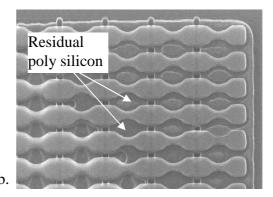

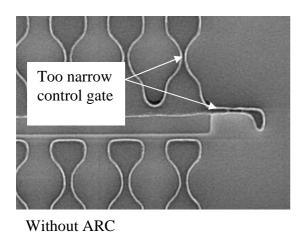

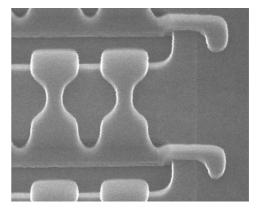

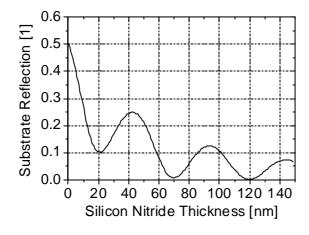

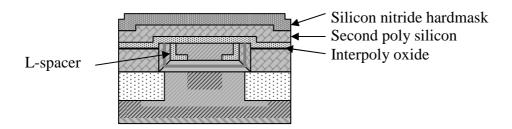

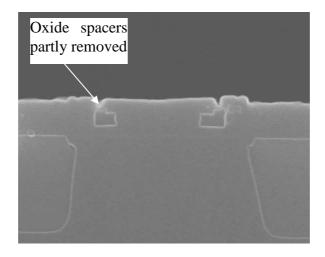

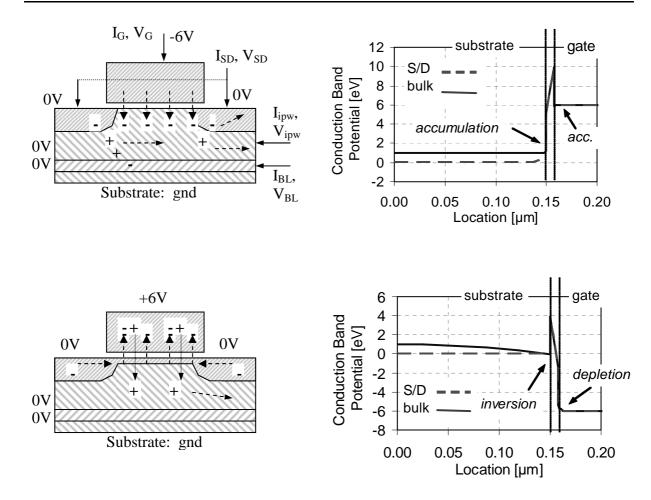

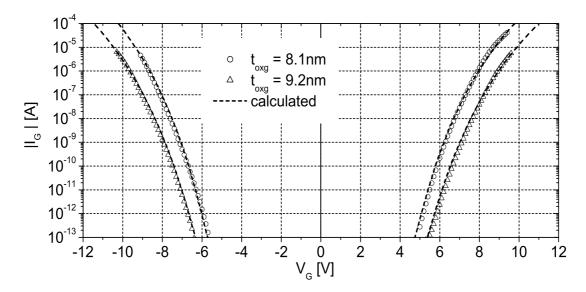

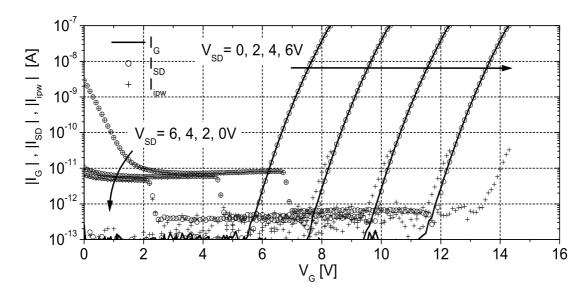

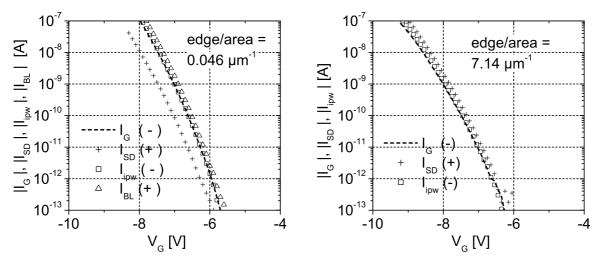

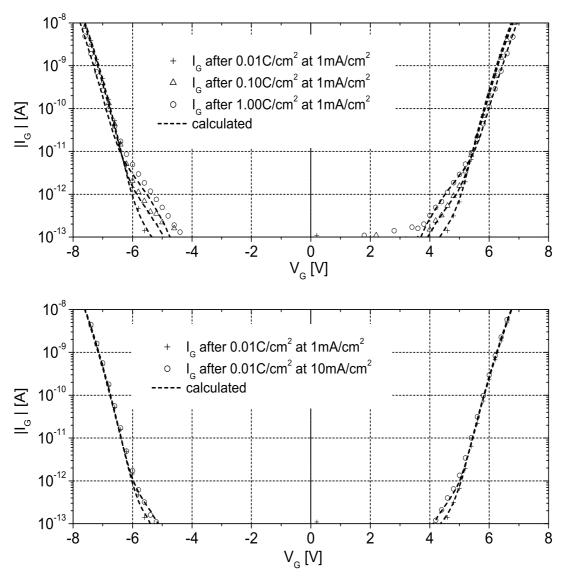

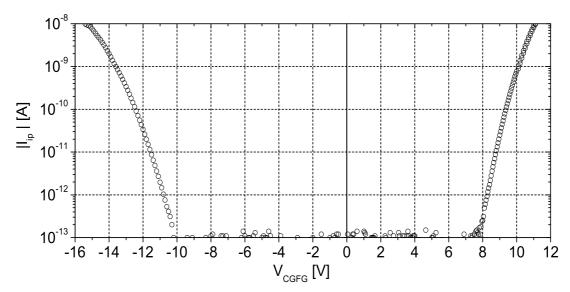

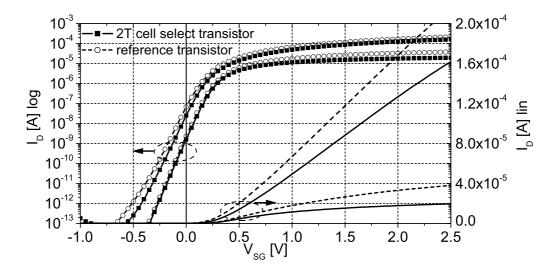

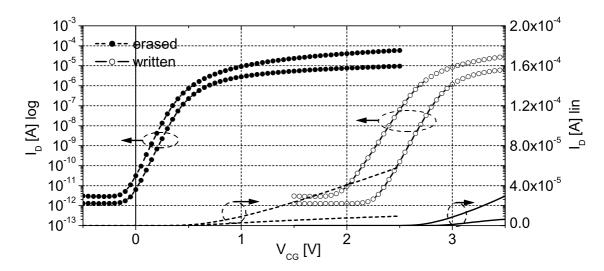

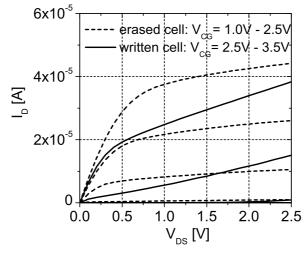

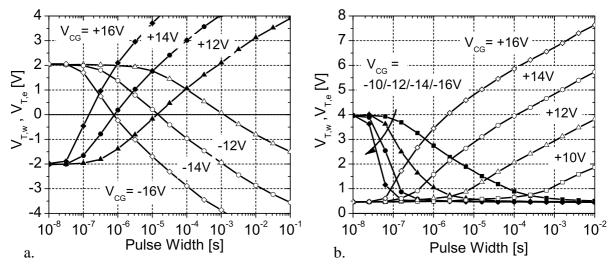

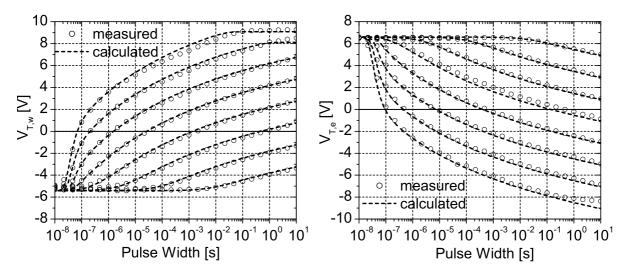

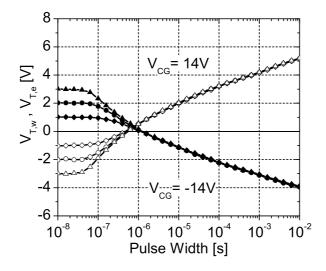

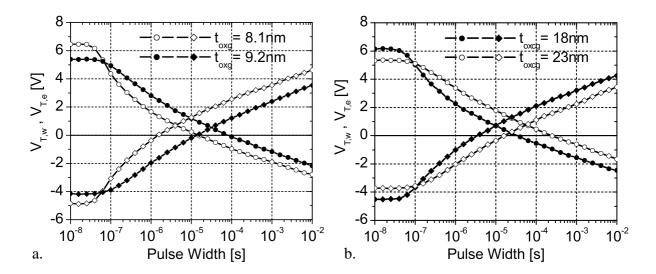

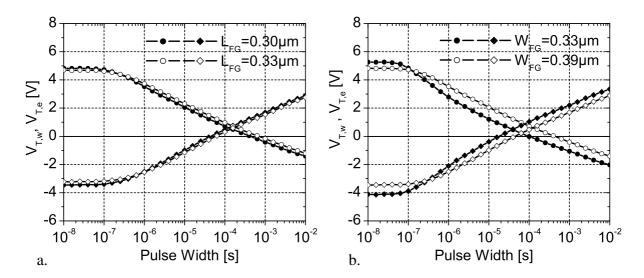

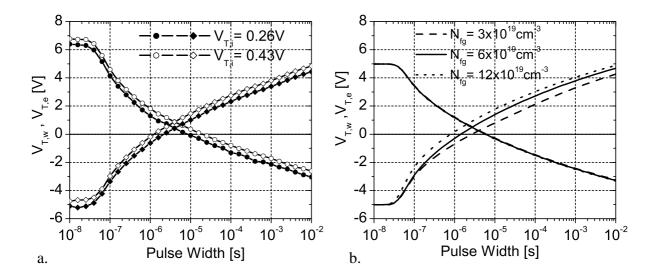

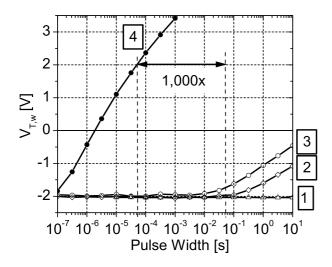

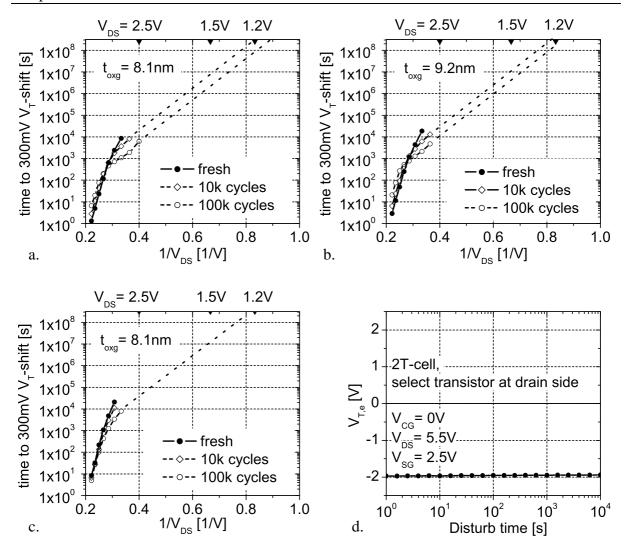

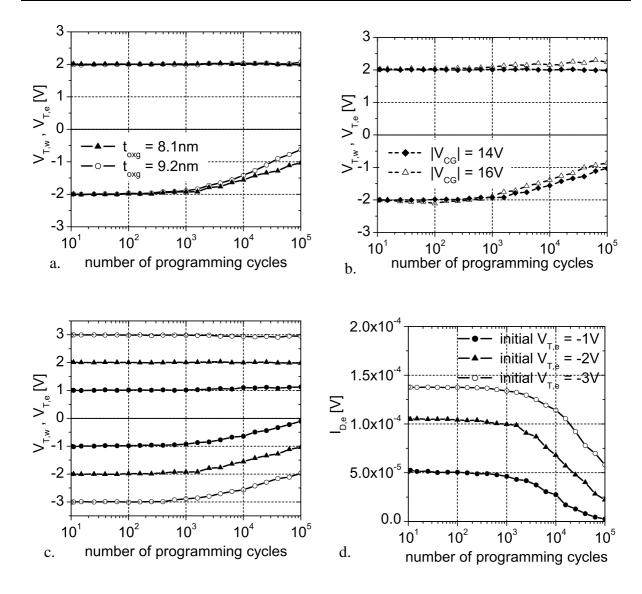

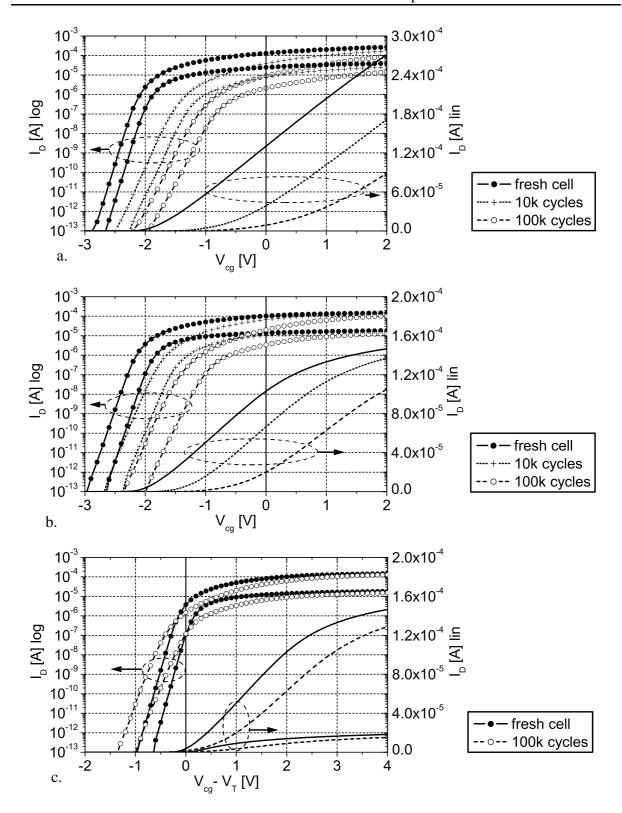

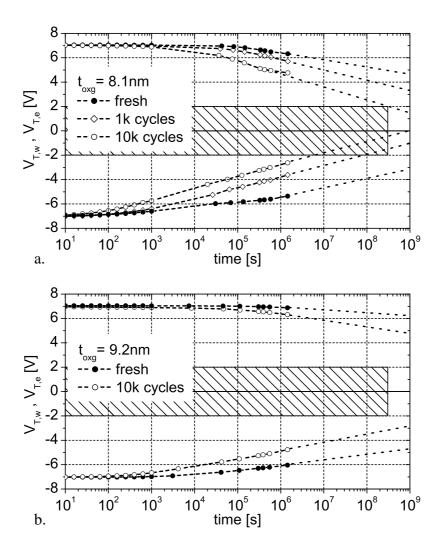

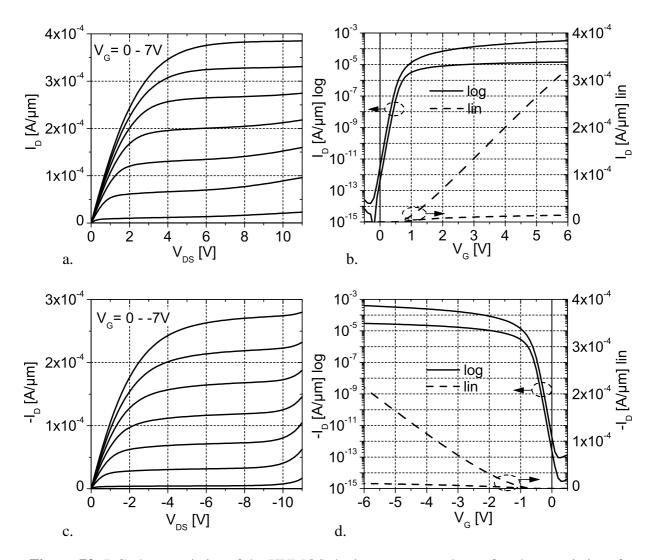

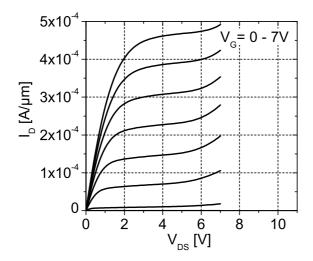

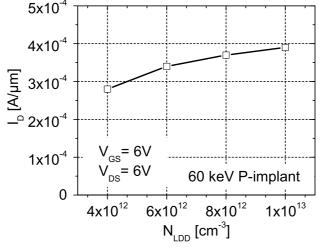

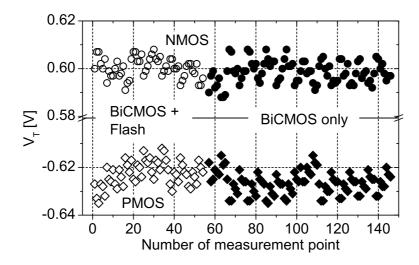

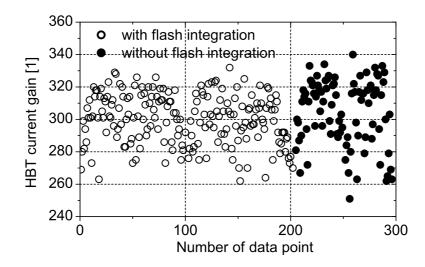

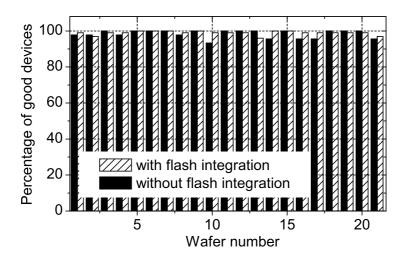

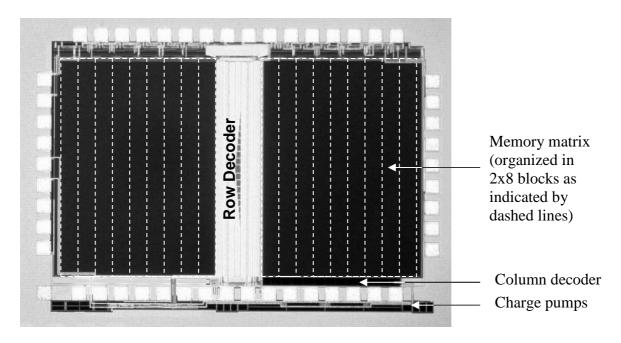

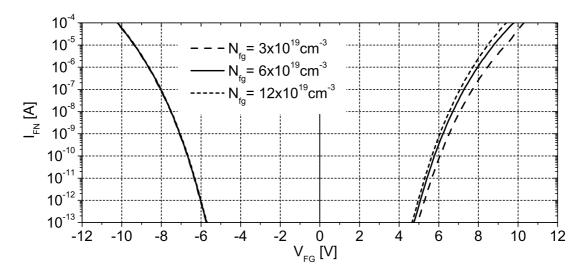

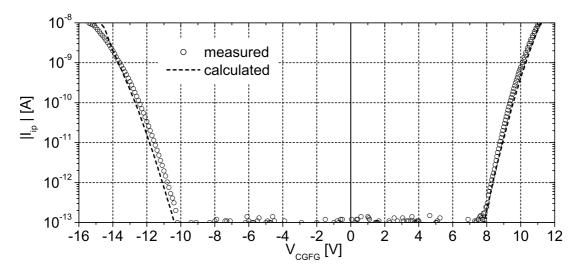

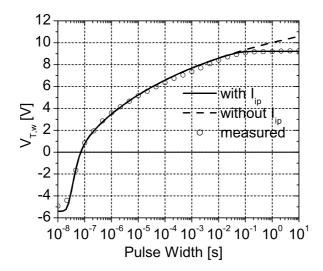

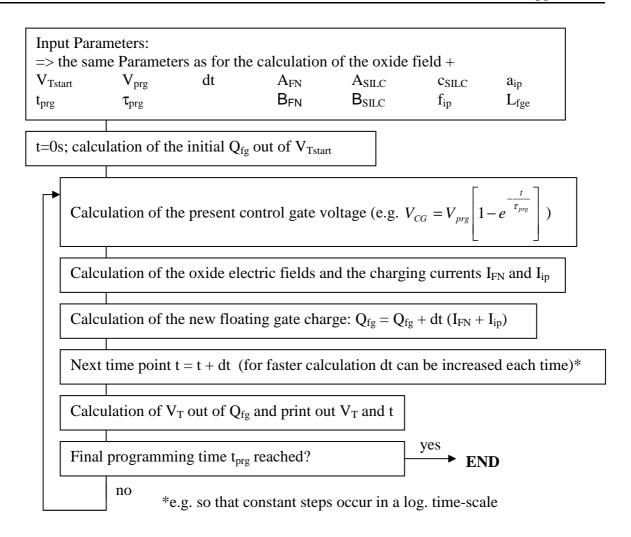

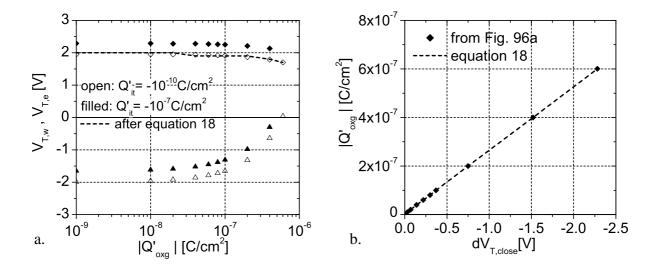

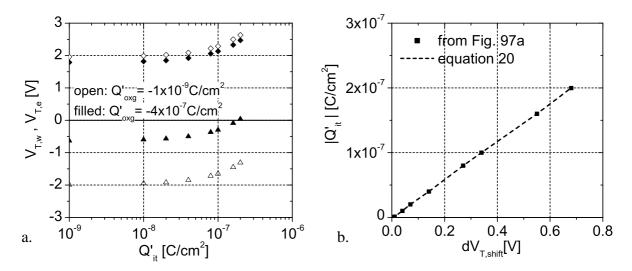

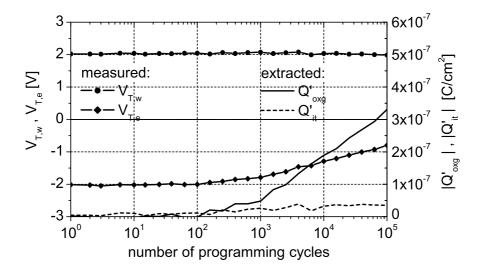

The Integration of the high voltage transistors is in general critical with respect to the cost of the embedded memory process. By the way it is done here it does not need an additional lithographic step, which is achieved by reusing process steps of the memory transistor fabrication and of the CMOS fabrication. At different steps the process is adjusted with respect to the HVMOS fabrication. Firstly, the adjustment of the doping profile in the flash-pwell is also done with respect to the HVMOS. Secondly, an additional P-implantation for adjusting the wells of the HVMOS transistors, which is not required for the memory cell itself, is done after FG-etching. Thirdly, the interpoly oxide fabrication is optimized with respect to the HVMOS transistor. The fourth point is another additional shallow P - implantation carried out after the control gate etching for forming LDD extensions.