© 2016 IEEE. Personal use of this material is permitted. Permission from IEEE must be obtained for all other uses, in any current or future media, including reprinting/republishing this material for advertising or promotional purposes, creating new collective works, for resale or redistribution to servers or lists, or reuse of any copyrighted component of this work in other works.

Digital Object Identifier (DOI): 10.1109/PEDG.2017.7972558

International Symposium on Power Electronics for Distributed Generation Systems

Comparative analysis of MAB dc-dc converters configurations in modular smart transformer

Levy Ferreira Costa Felix Horffmann Giampaolo Buticchi Marco Liserre

# **Suggested Citation**

L. F. Costa, F. Hoffmann, G. Buticchi and M. Liserre, "Comparative analysis of MAB dc-dc converters configurations in modular smart transformer," 2017 IEEE 8th International Symposium on Power Electronics for Distributed Generation Systems (PEDG), Florianopolis, 2017, pp. 1-8.

# Comparative Analysis of MAB DC-DC Converters Configurations in Modular Smart Transformer

Levy F. Costa, Felix Hoffmann, Giampaolo Buticchi and Marco Liserre Christian-Albrecht-University of Kiel (Uni-Kiel) / Power Electronics Chair (PE) Kaiserstr. 2, 24143, Kiel, SH, Germany Email: {lfc, hfo, gibu, ml}@tf.uni-kiel.de

Abstract—In this work, the quadruple active bridge dc-dc converter (QAB) is proposed to be used as a building block to implement the dc-dc stage of a Smart Transformer. Different configuration for this converter are possible and all of them are considered for investigation. Thus, four different architectures of ST, including one based on the Dual Active Bridge (DAB) converter, are presented and compared in terms of cost, efficiency, reliability and implementation complexity. As an additional contribution, different semiconductors technology (silicon IGBT and silicon carbide MOSFETs) are evaluated in order to verify their impact on ST application. The design for each architecture is described and the results are compared. In order to validate the theoretical analysis developed in the paper, a 20 kW prototype was built and experimented.

#### I. INTRODUCTION

The high penetration of distributed generation and the integration to the grid of new loads (e.g. electric vehicles) has changed the distribution electric system and new challenges has emerged. Among them, the reverse power flow requirement, storage integration, management of hybrid grids (dc and ac) and power quality improvement are highlighted [1]–[4]. Smart Transformer (ST), a power electronics-based system with advanced control and communication functionalities, is a promising solution for the aforementioned problems.

One of the biggest challenge of this system lays on the implementation of the dc-dc stage, responsible to connect the medium voltage (MV) to the low voltage (LV) dc sides with medium/high frequency (MF/HF) galvanic isolation. Hence, this stage has requirements, such as: high voltage capability in the MV side, high current in the LV side, high voltage isolation, power flow control and overload and shortcircuit protection (working as a dc breaker to protect possible load/source/microgrid connected to the LV dc-link) [1]-[5]. To meet all of them, the modular architecture bring several advantages, like fault tolerant capability by using redundant modules concept, scalability in power and voltage, reduced dv/dt and di/dt (low EMI emission and isolator stress on the HF transformer) and the possibility to use standard low voltage/current rating devices. For these reasons, modular architectures are preferable for ST applications.

Based on this approach, several dc-dc converters have been investigated to be used as a building-block of the dc-dc stage, but the Dual-Active-Bridge (DAB) have received more attention, due to its advantages of soft-switching, high efficiency 978-1-5090-5339-1/17/\$31.00 2017 IEEE.

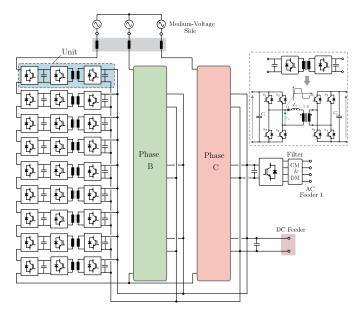

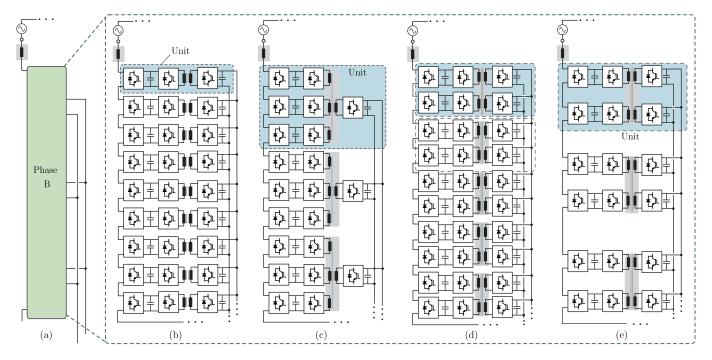

Figure 1. Modular smart transformer architecture using the dual active bridge converter as a building block of the dc-dc stage.

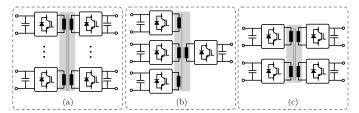

and high power density [3]–[5]. Fig. 1 depicts the modular ST using the DAB converter as a basic cell of the dc-dc stage. This converter, that is composed by two active bridges connected to a high frequency transformer, was generalized in [6]–[9], where more bridges were connected to a multiwinding transformer, leading to the concept of the multiple-active-bridge (MAB), as shown in Fig. 2 (a). The MAB converter presents a reduced number of transformers and modules, when compared to the design based on DAB, while still preserving the same advantages. Consequently, the MAB converter became a attractive solution in ST application, as presented in [1], [2], [8], and this converter was deeply investigated in [8], where four active bridges, named Quadruple-Active-Bridge (QAB), were employed.

The QAB converter has the degree of freedom to be connected symmetrically (two input and two output) or asymmetrically (three input bridges and one output bridge), as shown in Fig. 2, but the particularities and advantages of each of them have not yet been discussed on the literature. In this context, this work uses the QAB converter as a building block of the dc-dc stage of the modular ST, where the possible configurations are investigated. Therefore, the configurations

Figure 2. Multiple-Active-Bridge converter topology and its particular case of four bridges (Quadruple-Active-Bridge, QAB): (a) MAB topology, (b) asymmetrical configuration of the QAB converter, (c) symmetrical configuration of the QAB converter.

are analyzed and compared in term of efficiency, cost, reliability and complexity, considering the ST specifications and requirements. Furthermore, the classical solution based on the DAB converter is included in the analysis, as a matter of comparison. The main goal of this work is to investigate the feasibility of the QAB converter in ST application, with respect to the standard solution (the QAB converter) and verify which configuration offers more advantages to the system. As an additional contribution, Silicon (Si) IGBT and Silicon Carbide (SiC) MOSFETS are used on the QAB design and their performances are compared, in order to investigate the potential of different semiconductors technology in ST application.

The paper is divided as follow: in section II, the theoretical analysis of the QAB converter is presented, where its equivalent model is shown and the main equations are derived. The different configuration of the QAB are analyzed and compared in section III, considering the ST scenario, while several design aspect are discussed. In this section, the configurations are compared and a discussion, showing the most promised one is presented. Finally, a 20 kW prototype of the QBA converter was built and experimental results are provided in Section IV.

#### II. OPERATION PRINCIPLE OF THE QAB CONVERTER

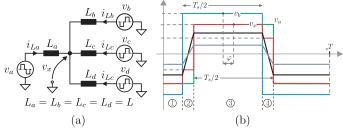

The QAB is composed by four active bridges and for the analysis, each of them is denoted by the letters a, b, c and d. The elements of the bridges have sub-index  $i = \{a, b, c, d\}$  to indicate the bridge the element belongs to. To analyze the converter, an equivalent circuit based on the Y-model and depicted in Fig. 4 (a) is used, in which the bridges are replaced by rectangular voltage sources  $(v_a, v_b, v_c \text{ and } v_d)$ . The voltage on the central point  $v_x$  and the current slope of each inductor are given by (1) and (2), respectively, where  $k = \{a, b, c, d\}$ .

To modulate the converter, the Phase-Shift Modulation (PSM) strategy is employed. Using this modulation scheme, rectangular voltages  $v_a$ ,  $v_b$ ,  $v_c$  and  $v_d$  with phase shift  $\varphi_a$ ,  $\varphi_b$ ,  $\varphi_c$  and  $\varphi_d$ , respectively, and constant switching frequency  $f_s$  are applied to the transformer. The power is controlled by the phase difference among the bridges and it can be generally described in (3), where, i = a, b, c, d and k = a, b, c, d, according to [9], [10]. The main waveform of the PSM is shown in Fig. 4 (b).

The PSM is characterized by ZVS turn-on, but this features depends on the input and output voltages relation and also the load. As the input and output voltage are considered constant,

Figure 4. Model of the QAB converter and main waveforms, using the PSM.

Figure 5. Current and voltage waveforms on the LV side semiconductors  $(i_{S1a}, v_{S1a}, i_{S2a}, v_{S2a})$  and MV semiconductors  $(i_{S1b}, v_{S1b}, i_{S2b}, v_{S2b})$  of the QAB converter.

the converter can be properly designed to work with ZVS operation for its entire range of operation. Consequently, this scheme offers several advantages for the converter operation.

The voltage and current waveforms on the semiconductors of the MV side bridge and LV bridge of the QAB converter are depicted in Fig. 5. If properly design, the current and voltage waveforms on the semiconductors will be same as depicted in 5, regardless the configuration of the QAB converter presented in Fig. 2 (b) and (c). To calculated the current effort on the semiconductors and transformer and consequently the losses, the equations (3) and (4) are used, considering the current waveforms presented in Fig. 5. As a results, the rms and avg current in each semiconductors of the bridges connected to the LV and MV sides are calculated by (1) to (4).

$$i_{D(avg)} = \frac{1}{\pi} \left( A_m \frac{\phi^2}{4} + I_0 \frac{\phi}{2} \right) \tag{1}$$

$$i_{D(rms)} = \sqrt{\frac{1}{\pi} \left( \frac{1}{3} A_m^2 \frac{\phi^3}{2} + A_m \frac{\phi^2}{2} + I_0^2 \frac{\phi}{2} \right)}$$

(2)

$$i_{S(avg)} = \frac{A_m}{\pi} \left( \frac{\phi^2}{8} \right) \tag{3}$$

$$i_{S(rms)} = \sqrt{\frac{1}{\pi} \left( \frac{1}{3} A_m^2 \left( \phi - \frac{\phi^3}{2} \right) + A_m \left( \frac{\phi}{2} \right)^2 + I_0^2 \frac{\phi}{2} - I_0 \frac{\phi}{2} \right)}$$

(4)

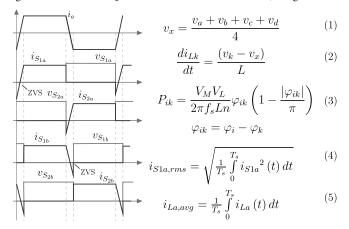

Figure 3. Smart transformer architecture based on different building blocks configuration of the dc-dc converter: (a) DAB - Arch: DAB converter as the building block, (b) AQAB - Arch: QAB converter in asymmetrical configuration, (c) SQAB-V - Arch: QAB converter in symmetrical configuration, preserving the same voltage level of the asymmetrical configuration, (d) SQAB-P - Arch: QAB converter in symmetrical configuration, preserving the same power level of the asymmetrical configuration.

#### III. SYSTEM CONFIGURATION AND DESIGN

As mentioned before, the main goal of this work is to investigate the potential of the QAB converter in ST application, besides to analyze its possible configurations and compare them, considering the standard DAB as a basis of comparison. Therefore, to implement the dc-dc stage of the ST, four different architectures are investigated for in this work and they are shown in Fig. 3. The first one is a modular architecture based on the standard DAB solution (see Fig. 3 (a)), that will be used as a basis of comparison. The second architecture depicted in Fig. 3 (b) is based on the QAB converter configured asymmetrically. The third and fourth cases, shown in Fig. 3 (c) and (d), respectively, are based on the symmetric configuration of the QAB converter. The analysis of the symmetrical configuration was divided in two cases, with the purpose for making it wider: the first one (Fig. 3 (c)) uses more units, keeping the same voltage level over the QAB cells (and over the semiconductors) in comparison with the asymmetrical QAB architecture, whereas the second case (Fig. 3 (c)) uses the same number of units with respect to the asymmetrical OAB architecture, keeping the same power level for each unit.

As can be noticed, all theses architectures uses the Cascaded H-Bridge (CHB) topology as a front-end rectifier, because it offers several advantages, as described in [1]. In addition, the CHB cells are considered part of the unit, for the repairability purposes. Regarding the number of units selection, three units are chosen for the asymmetric QAB architecture, resulting in 9 CHB cells, and then 9 units are used in the DAB architecture

Table I GRID SPECIFICATION

| Rated Power | MVAC  | LVAC  | Grid frequency | LVDC  |

|-------------|-------|-------|----------------|-------|

| 1 MVA       | 10 kV | 400 V | 50 Hz          | 700 V |

Table II

QAB SPECIFICATION AND DESIGN CONSIDERATION

| Total MVDC link     | $V_{MVDC} = 10.2 \text{ kV}$ |

|---------------------|------------------------------|

| LVDC link           | $V_{LVDC} = 700 \text{ V}$   |

| Unit Power          | $P_{unit} = P_{ST}/N_{unit}$ |

| Switching frequency | $f_s = 20 \text{ kHz}$       |

| Nominal PS angle    | $\varphi_{nom} = 35^{\circ}$ |

to keep the same CHB structure. This number provides a good trade-of between the number of components and the usage of the employed semiconductors (voltage and current rating).

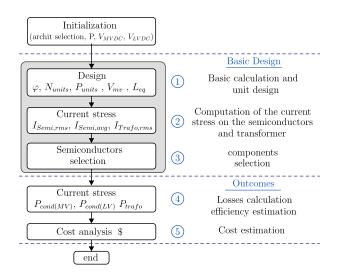

# A. Design Consideration of the Units

For the comparative analysis, each of the architectures presented in Fig. 3 must be carefully design and the losses, efficiency and cost must be calculated. To do so, a computer-aided design approach was used, and the flowchart of the implement design algorithm is presented in Fig. 6. The ST architectures are designed considering the grid specification presented in Table I. The QAB converter is designed according to [9], [10]. For the design, it was considered a nominal phase shift angle of  $\phi=35^\circ$  to reduce the reactive power processed by the converter, but still keeping the power controllability. Further design considerations for the QAB converter design are summarized in Table II.

Figure 6. Simplified flowchart of the algorithm used to design the power units of the ST architectures.

## B. Semiconductor Selection and Losses Analysis

Considering the voltage and power level of the converter, Silicon IGBT module are often used. On the other hand, the new technology of Silicon-Carbide MOSFETs has emerged as a high performance and economically viable solution. These devices have been used to implement the power converters of the ST architecture in [11], [12]. However, the potentialities of such semiconductors is still an open question in power electronic field. For these reasons, both aforementioned semiconductors technologies (Si IGBT and SiC MOSFETs) are taken into account on the design of the power converters, presented in Fig. 6.

For the semiconductor selection, devices from the biggest market players on IGBT modules sector and SiC MOSFETs sector were considered and they are: *Powerex Power Semiconductors/Mitsubishi Electric* and Wolfspeed/CREE [13], [14]. Several different devices from both manufactures were considered on the converter's design and they are listed in Table III.

To estimate the efficiency of each architecture, the losses in each component must be calculated. The conduction losses of the SiC MOSFETs are calculated by (5), where the onresistance ( $R_{ds(on)}$ ) is function of the drain-source current ( $i_{dc}$ ), junction temperature ( $T_J$ ) and gate voltage ( $V_{gs}$ ). Assuming a constant junction temperature of  $100^{\circ}C$  and a constant gate voltage of 15 V, the equation is simplified to (6). Similarly, the losses on the IGBT are calculated by (5), in which can be simplifies by (8). Therefore, applying (5) in (6) and (8), the losses on the MV side semiconductors are obtained for the SiC MOSFETs and IGBT cases, respectively. Similarly, the losses on the LV side semiconductors are obtained replacing the equation (6) in (6) and (8). For the HF transformer, only the wire losses are considered and they are calculated using (6) and (9).

Table III

SPECIFICATION OF THE SEMICONDUCTORS CONSIDERED IN THE DESIGN

| Si-IGBT Power Modules   |        |       |               |                          |  |  |  |

|-------------------------|--------|-------|---------------|--------------------------|--|--|--|

| Reference               | V      | I     | $V_{CE(on)}$  | r <sub>(on)</sub> (25 C) |  |  |  |

| CM50DU-24F              |        | 50 A  | 1.25 V        | $10.71m\Omega$           |  |  |  |

| CM75DU-24F              |        | 75 A  | 1.2 V         | $8m\Omega$               |  |  |  |

| CM100DY-24A             | 1.2 kV | 100 A | 1.2 V         | $5m\Omega$               |  |  |  |

| CM150DX-24S             |        | 150 A | 1.2 V         | $3.5m\Omega$             |  |  |  |

| CM200DX-24S             |        | 200 A | 1 V           | $3.3m\Omega$             |  |  |  |

| CM300DX-24S1            |        | 300 A | 1 V           | $3.1m\Omega$             |  |  |  |

| CM75DY-34A              | 1.7 kV | 200 A | 1.2 V         | $18m\Omega$              |  |  |  |

| QID331006               | 3.3 kV | 100 A | 1 V           | $32m\Omega$              |  |  |  |

| QIC6508001              | 6.5 kV | 50 A  | 2 V           | $40m\Omega$              |  |  |  |

| SiC MOSFETs             |        |       |               |                          |  |  |  |

| Reference               | V      | I     | $V_{(Diode)}$ | $R_{ds(on)}$             |  |  |  |

| C2M0040120D             | 1.2 kV | 60 A  | 3.1V          | $40m\Omega$              |  |  |  |

| C2M0025120D             |        | 90 A  | 3.1V          | $25m\Omega$              |  |  |  |

| C2M0045170D             | 1.7 kV | 72 A  | 3.6V          | $45m\Omega$              |  |  |  |

| Cree Preliminary 3.3 kV | 3.3 kV | 45 A  | 3.1V          | $40m\Omega$              |  |  |  |

$$P_{mosfet(cond)} = \frac{1}{T} \int_{0}^{T} R_{ds(on)} \left( i_{ds}(t), T_{J}, V_{gs} \right) \cdot i_{ds}^{2}(t) dt \quad (5)$$

$$P_{mosfet(cond)} = R_{ds(on)} \cdot I_{S_1(rms)}^2 \tag{6}$$

$$P_{IGBT(cond)} = \frac{1}{T} \int_{0}^{T} V_{CE}\left(i_{C}\left(t\right), T_{J}, V_{gate}\right) \cdot i_{C}\left(t\right) dt \qquad (7)$$

$$P_{IGBT(cond)} = V_F \cdot V_{CE(avg)} + R_F \cdot I_{C(rms)}^2$$

(8)

$$P_{Tr(wire)} = R_{wire} \cdot (I_{Tr(rms)})^2 \tag{9}$$

# C. Further Considerations

For the economic comparison of the different architectures, the cost of the main components are considered. In that case, only the cost of the semiconductors and also an simplified cost of the transformer is considered. For the IGBT, the cost are obtained directly with the manufacturer [15], while for the SiC case, the cost were obtained from the distributor (Mouser Electronics). To compute the cost of the MFT, only the amount of cooper of the wires used to implement the transformer is considered to simplify the analysis. The required amount of cooper used on the winding is proportional to the rms current of each winding. Thus, the cost will be proportional to the current effort in each winding of the transformer. The auxiliary components, like gate driver unit (GDU), auxiliary power supply (APS) and control and communication system (CCS), for each cell, are also considered on the cost and reliability analysis. It is assumed that the same components can be used for each cell of the DAB and OAB converters, regardless the voltage and current rating the of semiconductors employed. Consequently, the cost of the individual components is the same, regardless the architecture that they are employed, and only the quantity is different, according to the architecture. Additionally, those components are also considered for the reliability analysis.

#### IV. COMPARATIVE EVALUATION

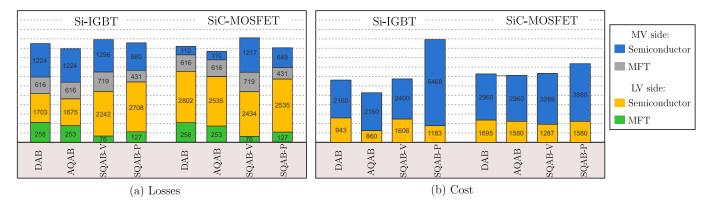

The results from the previous described design are presented in Table IV and in Figs. 7, for each architecture . As can be seen, they are divided in two cases, according to the employed semiconductors technology. The first case uses Si-IGBT, whereas the second SiC-MOSFETs, and each case is discussed as follow.

The DAB - Arch has more power unit, but the power level of each unit is the lowest, compared to the others architectures. Analyzing the parameters of the MV side, the current effort on the semiconductor are the same for all architectures, independently from the voltage and power level. Hence, the current rating of the employed semiconductor is also the same. With respect to the voltage level of the semiconductors, only the SQAB-P - Arch needs to use 3.3 kV devices, while the others require 1.7 kV. Then, DAB - Arch, 2 and 3 uses the same devices on the MV side. In spite of the availability of 3.3 kV IGBT on the market, there is no SiC-MOSFET available yet with this voltage rating. According to [13], [14], the 3.3 kV SiC-MOSFET was already developed and it is under test process to be launch on the market in the next years. Previous information for such device were provided in [13], [14], as well as a price estimation. Thus, these information were used in this investigation, to calculated the losses and cost of SQAB-P - Arch.

Analyzing the LV side, the AQAB - Arch has less cells connected in this side, demanding then higher current rating devices, in respect to the others architectures. As can be observed in Table IV, AQAB - Arch requires devices rated for 200 A and such devices are not available for the SiC-MOSFETs considered in this study (see Table III). Thus two devices C2M0025120D (1.2 kV / 90 A) were used in parallel, in which is a usual practice. Regarding the voltage level, 1.2

kV devices were used for this side in all architectures, because the LV cells are in parallel in this side.

#### A. Losses and Cost Comparison

The cost and efficiency are the most important parameters evaluated in this work and they are compared follow.

From the losses analysis presented in Fig. 7, it can be seen that the AQAB - Arch presents the best performance, while SOAB-V - Arch the worst, regardless the employed semiconductors. The fewer number of components associated to the high performance of this selected IGBT and MOSFETs on the LV side of AQAB - Arch played an important role to provide the best performance. The DAB - Arch, used as basis of comparison, has presented the second better performance, but only slightly better compared to the SQAB-P - Arch. As an overall analysis, it can be noticed that the losses for all architecture are very similar to each other, with a difference of only 10% between the best one and the worst one. Note that this design concerns the specifications provided in Table I. Different grid specification might imply in different results. Still from this results, the application of SiC MOSFETs has improved the performance in terms of efficiency of the architectures 1,2 and 4, but deteriorate the efficiency of SQAB-V - Arch. Due to high number of employed modules in this last architectures, the current in the LV side bridges are very reduced, allowing the use of lower current rating devices, compared to the others. As a result from the design, the SiC MOSFETs C2M0040120D (1200V / 60 A) was selected for the SQAB-V - Arch, while the device C2M0025120D (1200V / 90 A) was selected for the others architectures, providing lower on resistance and better performance. Of course, the device C2M0025120D can also be used in SQAB-V - Arch, improving its performance, but also increasing its cost.

Table IV COMPARATIVE ANALYSIS OF THE ARCHITECTURES

|                                        | Basic Inform | ation (per Phase) |               |                         |  |  |  |

|----------------------------------------|--------------|-------------------|---------------|-------------------------|--|--|--|

|                                        | DAB - Arch   | AQAB - Arch       | SQAB-V - Arch | SQAB-P - Arch           |  |  |  |

| Number of Units per Phase              | 9            | 3                 | 5             | 3                       |  |  |  |

| Power Level of the Unit                | 37.04 kW     | 111.11 kW         | 66.66 kW      | 111.11 kW               |  |  |  |

| MVDC link                              | 1.13 kV      | 1.13 kV           | 1.02 kV       | 1.7 kW                  |  |  |  |

| Semiconductor Voltage Rating (MV side) | 1.7 kV       | 1.7 kV            | 1.7 kV        | 3.3 kV                  |  |  |  |

| Total N° of semiconductors (MV side)   | 36           | 36                | 60            | 36                      |  |  |  |

| Total N° of semiconductors (LV Side)   | 36           | 12                | 20            | 12                      |  |  |  |

| Selected Semiconductor                 |              |                   |               |                         |  |  |  |

| Si-IGBT (MV side)                      | CM75DY-34A   | CM75DY-34A        | CM75DY-34A    | QID3310006              |  |  |  |

| Si-IGBT (LV side)                      | CM75DU-24F   | CM200DX-24S       | CM75DU-24F    | CM75DU-24F              |  |  |  |

| SiC-MOSFET (MV side)                   | C2M0045170D  | C2M0045170D       | C2M0045170D   | Cree Preliminary 3.3 kV |  |  |  |

| SiC-MOSFET (LV side)                   | C2M0040120D  | C2M0025120D       | C2M0040120D   | C2M0025120D             |  |  |  |

| Medium-Frequency Transformer           |              |                   |               |                         |  |  |  |

| N° of MFT                              | 9            | 3                 | 5             | 3                       |  |  |  |

| Equivalent inductance                  | 27.3 μ       | 187.96 μH         | 54.56 μH      | 34.54 μH                |  |  |  |

| Isolation requirement (Prim. to Prim.) | 1.7 kV       | 1.7 kV            | 1.7 kV        | 3.3 kV                  |  |  |  |

| Isolation requirement (Prim. to Sec.)  | 10 kV        | 10 kV             | 10 kV         | 10 kV                   |  |  |  |

| Isolation requirement (Sec. to Sec.)   | 700 V        | 700 V             | 700 V         | 700 V                   |  |  |  |

|                                        | Auxiliary    | Components        |               |                         |  |  |  |

| Auxiliary Power Supply                 | 18           | 12                | 20            | 12                      |  |  |  |

| Gate Driver Unit                       | 36           | 24                | 40            | 24                      |  |  |  |

| Control and comm system                | 36           | 24                | 40            | 24                      |  |  |  |

Figure 7. Comparative results for the investigated ST architectures, considering the Si-IGBT and SiC-MOSFETs devices: (a) losses comparison, (b) cost comparison.

Regarding the cost analysis, the AQAB - Arch has also presented the best results, regardless the semiconductor. However, when SiC-MOSFETs are employed, DAB - Arch, 2 and 3 presented similar costs with a small difference of 1%. Only SQAB-P - Arch has presented a significant high cost compared to the other, because of the prices of the higher voltage devices required on the MV side of this architecture.

A more detail discussion about the QAB configurations, semiconductor technologies and the feasibility to use QAB in comparison to DAB in ST are presented as follow.

# B. QAB Configurations

As can be notices from the results, the AQAB - Arch that uses the asymmetric configuration of the QAB converter is more advantageous in terms of efficiency and cost. The main reason for that is the fewer number of cells and MFT, compared to SQAB-V - Arch, associate to the fact that lower voltage rating devices are required in the MV side, compared to SQAB-P - Arch.

Although higher current rating devices are required to implemented the LV cell of the AQAB - Arch (see Table IV), the individual device cost does not differ much from the cost of the devices required by the others solutions, bringing economic advantages to this solution.

As SQAB-P - Arch requires semiconductors with voltage rating of 3.3 kV on the MV side, only IGBT can be used to implement currently. Besides, the price of this device is very high, increasing drastically the cost of the system. For that reason, SQAB-P - Arch is the most costly solution, reaching almost twice the cost of the AQAB - Arch.

# C. Si-IGBT vs. SiC-MOSFETs Comparison

As expected, the performance of all architecture are improved in terms power dissipation, when SiC MOSFETs are used, demonstrating the high performance of such semi-conductor technology. On the other hand, its price is still very high, when compared to the classic Si-IGBT solution. Using the results obtained from the AQAB - Arch, i.e. the most promised one, the SiC-MOSFETs offers around 10% of losses reduction, but the system cost increases in almost 40%. Then,

the energy saving throughout the system operation needs to be economically evaluated according to the application, to verify if the additional installation investment when SiC-MOSFET are used is economically viable.

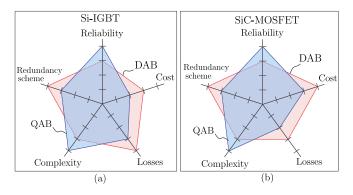

# D. Further Comparison

Another point that should be taken into account is the reliability and availability of the system. On one hand, the classical reliability approach based on the constant failure rate concept suggests that the reliability is inversely proportional to the number of components, because each component is a potential failure source. On the other hand, the reliabilityoriented approach described in [16] suggests that each component has a specific failure rate, according to its application and operation condition, e.g. operation temperature, humidity, etc. Although the research in this last approach has advanced considerably, a very advanced study for each condition is required and the failure rate of the auxiliary components (e.g. GDU, APS) is still difficult to compute. Hence, as a matter a simplicity, the classical approach is used in this comparison, where only the number of components, including the auxiliary, is considered.

AQAB - Arch and 4 have less cell in total, 12 cells against 18 and 20 of the DAB - Arch and 3, respectively. It implies in less power devices and auxiliary components, contributing to the reliability improvement. Then, these architecture are more advantageous from the reliability viewpoint.

The system can also be compared in terms of complexity and possibility to implement redundancy. Regarding the complexity, discussion regarding the control the QAB indicates higher complexity, when compared the DAB control, mainly because of balanced power issues. The multiwinding transformer is also more complex to be designed in respect to the classic two winding transformer. In this aspect, the DAB - Arch, based on DAB solution, might be more advantageous. On the other hand, such complexity can be overcome by increasing the research and development in these topics. The DAB is also very advantageous in terms of the redundancy scheme implementation, because the unit is more simple to be

Figure 8. Qualitative comparison of the standard solution based on DAB converter with the proposed QAB solution, considering the most promised configuration (asymmetric configuration): (a) Si-IGBT, (b) SiC-MOSFETs.

implement. Then, an additional unit be used with less impact on the system cost.

A qualitative comparison of all architectures is presented in Fig. 8, when Si-IGBT and SiC-MOSFETs are used. Although DAB might be more advantageous in terms of complexity and possibility do implement redundancy scheme, the QAB converter is presented as a most promised in term of efficiency, reliability and cost. Then, these results demonstrate the high potential of the QAB converter in ST application.

## E. QAB vs. DAB

To evaluate the potential of the QAB converter in ST application, the best configuration (AQAB - Arch) is individually compared to the standard solution based on DAB (DAB - Arch). Due to the fewer number of components (Cells and MFT), the QAB solution is more advantageous economically, as presented in Fig. 7 (b). Adopting this solution instead of

DAB, and considering the specification of the Table I, the system cost can be reduced in around 20%, when Si-IGBT are employed.

Regarding the efficiency, the QAB solution presented similar performance with the DAB, although the first one performs slightly better. As the QAB operates similarly to the DAB converter, when processing balanced power, then similar power losses dissipation is also expected. Of course, semiconductor with different electric characteristic are used in the LV cells for both cases, and also the quantity of semiconductors, resulting in this power dissipation difference between the solutions.

It is important to point-out that the DAB converter might be more advantageous for the implementation simplicity view-point. Since it is a classic solution and it has been intensively investigated for a while, its control system and design procedure is already well-known. Nevertheless, the MAB converter topology has been more often investigated recently [8], [9]. Then, QAB converter is presented as an economically viable solution and its potential in ST application has been demonstrated from the results obtained in this work.

#### V. EXPERIMENTAL RESULTS

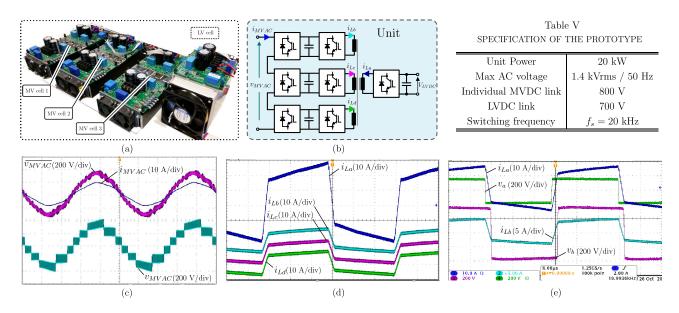

In order to evaluate experimentally the operation and performance of the QAB converter in ST, a downscaled prototype has been developed and tested. As the asymmetric configuration of the QAB was presented as the most advantageous one from the theoretical studies, it was chosen to be implemented and experimentally investigated. Fig. 9 (a) shows the picture of the implement prototype, while the specification is presented in Table V. In this picture, the cells of the CHB associated to the QAB converter is observed, sharing the same cooling system. For the implementation, the SiC MOSFETs C2M0025120D

Figure 9. Experimental results of the implemented ST prototype: (a) picture of the implemented unit, (b) asymmetric configuration used in the implementation, (c) main waveforms of the MV stage, (d) inductor current waveforms on the LV side  $(i_{La})$  and MV side  $(i_{Lb})$  and  $i_{Ld}$  of the QAB converter, (e) main voltage and current waveforms on the LV side  $(v_{La}, i_{La})$  and MV side of the QAB  $(v_{Lb}, i_{Lb})$  converter.

$(1200 \text{ V} / 25 m\Omega)$  and C2M0040120D  $(1200 \text{ V} / 40 m\Omega)$  from CREE were used on the MV side and LV side, respectively.

For the previous demonstration, the experiments are run with an input voltage of 230 V/50 Hz (available grid voltage) and a power level of 2 kW and the results are depicted in Fig. 9 (c). However, to demonstrate the operation and potential of the QAB converter, it was tested individually with power level of 10 kW, as presented in Fig. 9 (e).

In Fig. 9 (a), the main waveforms of the front-end MV stage is presented, where the input voltage before and after the ac filter  $(V_{MVAC})$  and the input current  $(i_{MVAC})$  are observed. From this results, a high power factor operation of the system is observed. Fig. 9 (d) shows the main waveforms of the dc-dc stage, where the currents on the LV cell  $(i_{La})$  and MV cells  $(i_{Lb}, i_{Lc}, i_{Ld})$  are presented. From these results, the balanced operation of the QAB converter is noticed, where each MV cell process the same amount of power. Furthermore, soft-switching operation is also observed from the current waveforms. Similarly, Fig. 9 (c) shows voltage and current on the ac side of the MV bridge  $(v_{Lb}$  and  $i_{Lb})$  and also on the LV bridge  $(v_{La}$  and  $i_{La})$ , where the phase-shift operation of these bridges is observed.

Finally, the efficiency of the QAB converter was measured experimentally and a value of 97.5% was obtained.

## VI. CONCLUSION

In this work, the multiple active bridge dc-dc converter using four bridges (QAB) is proposed to be used as a building block to implement the dc-dc stage of a Smart Transformer. Four different architectures of ST are presented and compared in terms of cost, efficiency, reliability and implementation complexity. One of this architectures are based on the standard DAB solution (used as a basis of comparison), while the others three are based on the QAB converter with different configuration. The design for each architecture is described, as well as the semiconductors employed. As an additional contribution, different semiconductors technology (silicon IGBT and silicon carbide MOSFETs) are evaluate in order to verify their impact on ST application.

As a result of this analysis, the architecture based on QAB converter configured asymmetrically (three bridge connected in the MV side and one on the LV side) has presented the best performance in terms of efficiency and cost. Compared to the classic DAB solution, the architecture based on QAB offers a cost reduction of around 20%. The efficiency of both solution are very similar, only a slightly improvement of 5% is obtained when the QAB is employed.

Regarding the potential of SiC-MOSFETs in ST application, this devices offers a losses reduction of around 10%, but is increase the system cost in around 40%. Therefore, to verify the economic feasibility of such devices in this application, a study considering the energy saving over time and the installation cost should to be realized. Note that this design concerns the specifications provided in Table I. Different grid application might imply in different results cost and losses.

Finally, experimental results were provided, in order to verify the performance of the ST architecture based on the QAB converter. Then, a 20 kW prototype of the ST based on asymmetrical configuration of the QAB converter was developed and tested, providing an efficiency of around 97.5%.

Then, this paper has demonstrated the high potential of the QAB converter as building block of the smart transformer.

#### ACKNOWLEDGMENT

The research leading to these results has received funding from the European Research Council under the European Union's Seventh Framework Programme (FP/2007-2013) / ERC Grant Agreement n. [616344] - HEART.

#### REFERENCES

- [1] M. Liserre, G. Buticchi, M. Andresen, G. D. Carne, L. F. Costa, and Z. X. Zou, "The smart transformer: Impact on the electric grid and technology challenges," *IEEE Industrial Electronics Magazine*, vol. 10, no. 2, pp. 46–58, Summer 2016.

- [2] M. Liserre, M. Andresen, L. Costa, and G. Buticchi, "Power routing in modular smart transformers: Active thermal control through uneven loading of cells," *IEEE Industrial Electronics Magazine*, vol. 10, no. 3, pp. 43–53, Fall 2016.

- [3] X. She, A. Q. Huang, and R. Burgos, "Review of solid-state transformer technologies and their application in power distribution systems," *IEEE Journal of Emerging and Selected Topics in Power Electronics*, vol. 1, no. 3, pp. 186–198, Sept 2013.

- [4] J. Wang, A. Q. Huang, W. Sung, Y. Liu, and B. J. Baliga, "Smart grid technologies," *IEEE Industrial Electronics Magazine*, vol. 3, no. 2, pp. 16–23, June 2009.

- [5] X. She, X. Yu, F. Wang, and A. Q. Huang, "Design and demonstration of a 3.6-kv 120-v/10-kva solid-state transformer for smart grid application," *IEEE Trans on Power Elect*, vol. 29, no. 8, pp. 3982–3996, Aug 2014.

- [6] H. Tao, A. Kotsopoulos, J. L. Duarte, and M. A. M. Hendrix, "Family of multiport bidirectional dc-dc converters," *IEE Proceedings - Electric Power Applications*, vol. 153, no. 3, pp. 451–458, May 2006.

- [7] J. L. Duarte, M. Hendrix, and M. G. Simoes, "Three-port bidirectional converter for hybrid fuel cell systems," *IEEE Transactions on Power Electronics*, vol. 22, no. 2, pp. 480–487, March 2007.

- [8] L. Costa, G. Buticchi, and M. Liserre, "Quad-active-bridge dc-dc converter as cross-link for medium voltage modular inverters," *IEEE Transactions on Industry Applications*, vol. PP, no. 99, pp. 1–1, 2016.

- [9] L. F. Costa, G. Buticchi, and M. Liserre, "Quadruple active bridge dcdc converter as the basic cell of a modular smart transformer," in 2016 IEEE Applied Power Electronics Conference and Exposition (APEC), March 2016, pp. 2449–2456.

- [10] S. Falcones, R. Ayyanar, and X. Mao, "A dc-dc multiport-converter-based solid-state transformer integrating distributed generation and storage," *IEEE Trans on Power Elect*, vol. 28, no. 5, pp. 2192–2203, May 2013.

- [11] L. F. Costa, G. Buticchi, and M. Liserre, "Highly efficient and reliable dc-dc converter for smart transformer," in 2017 IEEE Applied Power Electronics Conference and Exposition (APEC), March 2017.

- [12] K. Mainali, A. Tripathi, S. Madhusoodhanan, A. Kadavelugu, D. Patel, S. Hazra, K. Hatua, and S. Bhattacharya, "A transformerless intelligent power substation: A three-phase sst enabled by a 15-kv sic igbt," *IEEE Power Electron Magazine*, vol. 2, no. 3, pp. 31–43, Sept 2015.

- [13] J. Casady, "Power products commercial roadmap for sic from 2012-2020," Direct-Drive Motor Workshop, 2014.

- [14] J. Palmour, "Power products rel data & pricing forecasts for 650v-15kv sic power modules, mosfets & diodes," Direct-Drive Motor Workshop, 2014.

- [15] "Powerex power semiconductor solution," http://www.pwrx.com/, accessed: 2017-03-09.

- [16] H. Wang, M. Liserre, and F. Blaabjerg, "Toward reliable power electronics: Challenges, design tools, and opportunities," *IEEE Industrial Electronics Magazine*, vol. 7, no. 2, pp. 17–26, June 2013.