© 2017 IEEE. Personal use of this material is permitted. Permission from IEEE must be obtained for all other uses, in any current or future media, including reprinting/republishing this material for advertising or promotional purposes, creating new collective works, for resale or redistribution to servers or lists, or reuse of any copyrighted component of this work in other works.

Digital Object Identifier (DOI): 10.1109/IECON.2017.8216734

<u>Industrial Electronics Society</u>, <u>IECON 2017 - 43rd Annual Conference of the IEEE</u>

Voltage control strategies of smart transformer considering DC capacitor lifetime

Rongwu Zhu Holger Jedtberg Marco Liserre

## **Suggested Citation**

R. Zhu, H. Jedtberg, M. Liserre, "Voltage control strategies of smart transformer considering DC capacitor lifetime," Industrial Electronics Society, IECON 2017 - 43rd Annual Conference of the IEEE, 4278-4283, 2017.

# Voltage Control Strategies of Smart Transformer Considering DC Capacitor Lifetime

Rongwu Zhu

Chair of Power Electronics

Christian-Albrechts-Universität zu Kiel

Kiel, Germany

rzh@tf.uni-kiel.de

Holger Jedtberg

Chair of Power Electronics

Christian-Albrechts-Universität zu Kiel

Kiel, Germany

hje@tf.uni-kiel.de,

Marco Liserre

Chair of Power Electronics

Christian-Albrechts-Universität zu Kiel

Kiel, Germany

ml@tf.uni-kiel.de

Abstract—Distribution grids unbalance challenges the DC-link of the Smart Transformer leading to higher ripples and then the lifetime of the DC aluminium electrolytic capacitors (AEC) is reduced. Additionally, dead time and nonlinearity characteristic of IGBT also may introduce ripple current in DC link, potentially decreasing the lifetime of AEC. Based on physical characteristic of AEC, the lifetime estimation of AEC is investigated considering aforementioned impacts. To suppress these impacts, an improved voltage control strategy that can reduce AEC current ripple and then preserve AEC lifetime is proposed. The theoretical analysis has been demonstrated by the simulation results.

Keywords—solid-state transformer, smart transformer, aluminum electrolytic capacitor, unbalanced load

#### I Introduction

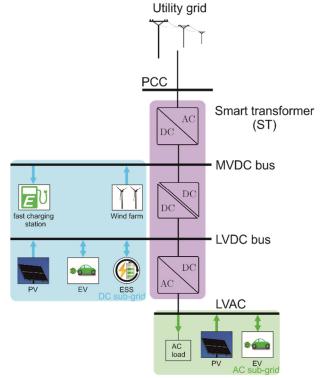

With the increasing of the penetration of the distributed generator (DG), the conventional power transformer (CPT)-based distribution grid suffers voltage variation, poor power quality, and great demand variability [1], [2]. Recently, the smart transformer (ST), which is based on the solid-state transformer, uses comunication and control to offer ancillary serverces for the distribution grid [3]–[6], as shown in Fig. 1.

Power converter system includes power semiconductors, DC capacitors and inductance components. Therefore, each component affects the whole system reliability. The leading manufactures could provide 20-year warranty for the power converter in renewable energy system. However, the average lifetime is 5-year for PV inverters [7], [8]. According to the recent investigation, the failure ratio is about 37% for photovoltaic inverters [7], [8] and is about 27% for the wind turbine converters [9], [10]. The failure ratio of electrolytic capacitor is 60%. Therefore, the lifetime estimation of the capacitor shall be correctly analyzed in every new application.

The lifetime of aluminium electrolytic capacitor (AEC) is mainly determined by the mission profiles and operation conditions (such as temperature, humidity, pressure, vibration, voltage and current) [3]. Even if the distribution grid planing is to keep three-phase load as balanced as possible, in practice three-phase grids are unbalanced. Therefore, the fundamental neutral-line current will degrade the lifetime of the AEC, significiantly.

In this paper, the effects of the dead time and nonlinear characteristic of the power semiconductor as well as the unbalanced loads on the AEC are studied in detail to indicate AEC lifetime reduction. Unlike CPT, the ST can actively regulate the PCC voltage, and in turn an improved voltage control strategy is proposed to preserve AEC lifetime.

Fig. 1 Smart Transformer feeding hybrid grids.

The rest of this paper is organized as follows. The effect of the dead time and unbalanced loads on the ST DC capacitor current ripple is studied in Section II. In Section III, the lifetime model of the AEC is presented to estimate the AEC lifetime under three cases. An improved voltage control strategy is proposed to preserve AEC lifetime in Section IV. Section V concludes this paper.

#### II SMART TRANSFORMER

The configuration of the ST is a three-stage AC/DC/DC/AC system, as shown in Fig. 1. The MV AC/DC converter is

controlled as the conventional front-end rectifier, which can compensate MV grid harmonic and reactive power. The DC/DC stage offers both MV and LV DC buses. The LV DC/AC converter forms the voltage of distribution grid, where the ST must feed four wires because of the single-phase customer.

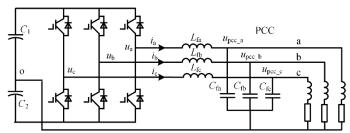

This paper only focuses on the ST LV side DC/AC converter voltage control and LV DC AEC lifetime improved. The detail structure of the ST LV side DC/AC converter is shown in Fig. 2. The neutral line is connected to the midpoint of the DC capacitors.

Fig. 2 Structure of the ST LV side converter

## A. Control system of the ST

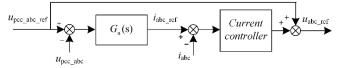

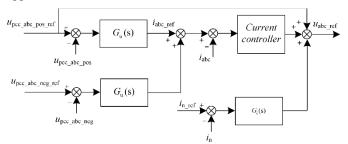

The overall control block diagram of the ST is shown in Fig. 3, where the outer loop controls three-phase PCC voltage and inner loop controls three-phase converter current.

Fig. 3 Control block diagram of the ST

As the basic function of the converter is to form the PCC voltage, the DC-link performances are affected by loads, directly. Assumed three-phase load unbalanced, the three-phase current will be unbalanced and then voltage drop on the internal impedance of ST (LC filter) will be unbalanced as well. Consequently, the PCC voltage may be unbalanced if the voltage controller can not effectively control the negative and zero sequence component. In order to increase the controllability on the negative and zero sequence component, a proportional and resonant controller (PR) is adopted.

$$G_{\rm u}({\rm s}) = k_{\rm p} + k_{\rm r} \frac{s}{s^2 + \omega_{\rm r} s + \omega_{\rm o}^2}$$

(1)

where  $\omega_0$  is the control signal frequency in rad.,  $\omega_c$  is the cutoff frequency in rad.  $k_p$ ,  $k_i$  and  $k_r$  are the proportional, integral and resonant gains, respectively.

## B. Effects of dead time and unbalanced loads

The dead time  $T_{\rm d}$  is needed to avoid short-circuit of the converter leg. The dead time and nonlinearity characteristic of power semiconductor introduce voltage disturbance, which can be equivalent as a zero sequence voltage, resulting in disturbance current in neutral line. The neutral line current flows into DC capacitor directly, as shown in Fig. 2. Additionally, the nonlinear characteristics of the power semiconductor also introduce voltage disturbance.

By neglecting the voltage drop on IGBT and parallel diode, the absolute value of voltage disturbance can be obtained as,

$$\left|V_{\rm d}\right| = \left|\frac{T_{\rm d} + t_{\rm ON} - t_{\rm OFF}}{2T_{\rm s}}\right| V_{\rm dc} \tag{2}$$

where  $V_d$  is the voltage disturbance,  $t_{ON}$ ,  $t_{OFF}$  and  $T_s$  are the turn-on time, turn-off time and switching period, respectively.  $V_{dc}$  is the DC-Link voltage.

Assumed that the power factor is 1.0, the Fourier Series of (2) can be expressed as,

$$V_{\rm d} = \frac{2(T_{\rm d} + t_{\rm ON} - t_{\rm OFF})V_{\rm dc}}{\pi T_{\rm s}} \left[ \sum_{n=1}^{\infty} (-1)^{n+1} \frac{1}{2n-1} \cos((2n-1)\omega t) \right] (3)$$

It depicts that the voltage disturbance includes odd-order harmonic component and the corresponding odd-order harmonic current will exist in DC capacitor.

On the other hand, when three-phase loads are unbalanced, PCC current may include positive sequence, negative sequence and zero sequence current. Obviously seen from Fig. 2, the zero sequence current flows into the DC capacitor directly through the neutral line.

In order to validate above theoretical analysis, the simulation is carried out based on Matlab/Plecs. The main circuit of the ST LV side DC/AC converter is the same as Fig. 2 and the simulation parameters are listed in TABLE I.

**Parameters** Value AC output voltage (V) 400 DC link voltage (V) 800 2250 DC capacitor (uF) Filter inductance (mH) 5.2 6.8 Filter capacitor (uF) 4 Load inductance (mH) 5 Load resistance (Ohm)

TABLE I SIMULATION PARAMETERS

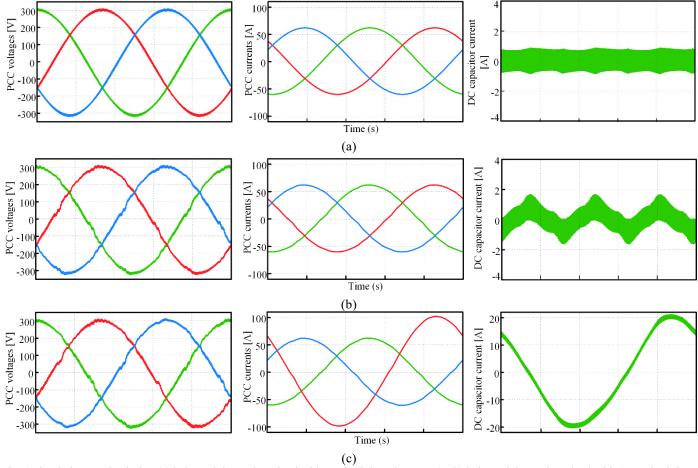

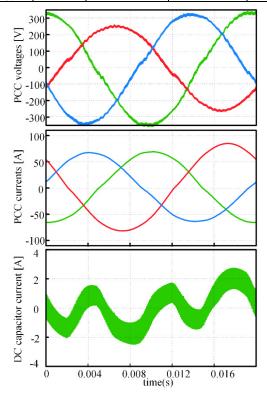

The performances of PCC voltage and current as well as the DC capacitor current under balanced load and neglecting the dead time conditions as base case are shown in Fig. 4 (a). Three-phase PCC voltages and currents are both balanced and sinusoidal, and the DC capacitor current ripple is less than 1A. In case 1, considering 2.5us dead time, the results are shown in Fig. 4 (b). Three-phase PCC voltages are still controlled well and balanced, while the DC capacitor current includes third and high order components, as shown in Fig. 4 (b). This matches with the theoretical analysis in (3).

In case 2, considering both 2.5us dead time and unbalanced loads, the results are shown in Fig. 4 (c), where three-phase load inductances are fixed at 4mH while load resistances are 5, 3 and 5 ohm, respectively. In comparison with Fig. 4 (a) and (b), the voltage is also balanced, due to the PR controller. However, the three-phase PCC current is unbalanced and DC capacitor current includes high 50Hz component with more than 40A peak-to-peak value, as shown in Fig. 4 (c). This also matches with the theoretical analysis.

In above three cases, the DC capacitor current performances

Fig. 4 Simulation results during (a) balanced three-phase load without dead time (base case), (b) balanced three-phase load with 2.5us dead time (case 1), and (c) unbalanced three-phase load with 2.5us dead time (case 2), the time scale is 0.004s/div.

are different, resulting in various impacts on DC capacitor lifetime, which will be discussed in the following section.

#### III LIFETIME ESTIMATION OF AEC

## A Lifetime Model of AEC

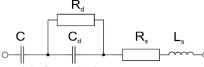

For AEC, the lumped model depicted in Fig. 5 is widely accepted in literature [11]–[13]. Apart from the ideal capacitance C, the model accounts for the frequency dependent dielectric losses by means of the parallel configuration of  $R_{\rm d}$  and  $C_{\rm d}$  as well as the constant ohmic resistance  $R_{\rm s}$  due to the foils, tabs and terminals of the construction. The inductive part of the AEC is modeled by the equivalent series inductance  $L_{\rm s}$ . The real part of the AEC impedance represents the equivalent series resistance (ESR)  $R_{\rm ESR}$  of the AEC which is of paramount importance to the lifetime and thus the reliability of the AEC.

Fig. 5 Lumped model of AEC [11]

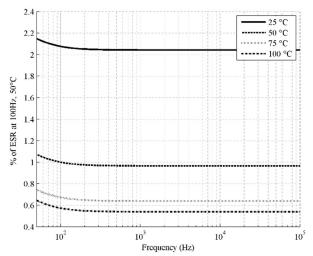

In addition to the frequency dependence, the ESR of an AEC exhibits a temperature dependence since the viscosity of the electrolyte, which is the main part of the AEC, changes with temperature [11]. Thus, the ESR is less for higher temperatures.

The impact of frequency and temperature on the AEC's ESR is depicted in Fig. 6. It is commonly known, that the power dissipation  $P_d$  of the AEC is determined by the square of RMS ripple current flowing through the capacitor and its ESR as given in Fig. 6. Since the ESR is frequency dependent the ripple current has to be decomposed into its spectral components.

$$P_{\rm d} = \sum I_{\rm RMS,h}^2 R_{\rm ESR,h} \tag{4}$$

The hotspot temperature  $T_{\rm h}$  of the AEC is determined by its thermal resistance  $R_{\rm th}$  and  $P_{\rm d}$ , which result in the hotspot temperature increase  $\Delta T_{\rm h}$ , and the ambient temperature  $T_{\rm a}$ .

$$T_{\rm h} = R_{\rm th}P_{\rm d} + T_{\rm a} = \Delta T_{\rm h} + T_{\rm a} \tag{5}$$

In order to approximate the lifetime L of the AEC, the lifetime model given in (6) can be applied, where  $L_0$  denotes the base lifetime as given by the manufacturer,  $V_0$  and  $T_{\rm h,0}$  are voltage and hotspot temperature at testing conditions, respectively, V and  $T_{\rm h}$  are the operating voltage and operating hotspot temperature, n is a voltage stress factor, which is manufacturer dependent [7].

$$L = L_0 \left(\frac{V}{V_0}\right)^{-n} 2^{\left(\frac{T_{h0} - T_h}{10K}\right)} = L_0 K_V K_T$$

(6)

Fig. 6 ESR of AEC over frequency for different temperatures [11]

The impacts of operating voltage and operating hotspot temperature on the lifetime can be represented by the voltage factor  $K_V$  and the temperature factor  $K_T$ , respectively. By inserting ( $T_h$  equ.) into (L equ.),  $K_T$  can be split into two parts as given in (7), where  $K_{Ta}$  and  $K_I$  denote the ambient temperature factor and the ripple current temperature factor, respectively.

$$K_{\rm T} = 2^{\left(\frac{T_{\rm h0} - T_{\rm a}}{10K}\right)} 2^{\left(\frac{-\Delta T_{\rm h}}{10K}\right)} = K_{\rm Ta} K_{\rm I}$$

(7)

By use of (7) the impact of ambient temperature and the hotspot temperature increase due to the ripple current on the AEC lifetime can be studied separately. Since the DC link

voltage can be considered constant, it is to be noted that the lifetime of the AEC is mainly dependent on the hotspot temperature. Thus, apart from the ambient temperature conditions, the ripple current can be considered the main stressor for the AEC. Therefore, examination of the latter is needed for AEC lifetime estimation purposes.

## B Lifetime estimation of AEC

In order to analyze the impact on the capacitor lifetime, it is assumed that both, operating voltage and ambient temperature, are the same for each case. Thereby, it is sufficient for the analysis of the relative lifetime  $L_{\rm rel}$  with respect to the base case to compare only the impacts of the corresponding capacitor ripple currents, as shown in (7), on the respective lifetime, where  $x = \{1, 2\}$  represents case 1 and 2, respectively.

$$L_{\rm rel,x} = \frac{K_{\rm L,x}}{K_{\rm Lbase}} \tag{8}$$

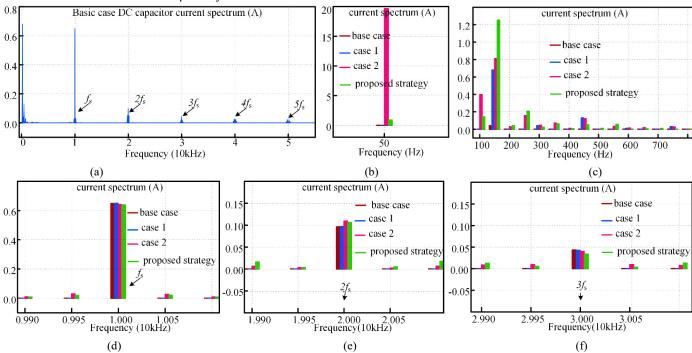

In order to clearly show the DC capacitor current ripples, the corresponding capacitor current spectrum is shown in Fig. 7. Under the base case, the capacitor current spectrum shows that the harmonic current has high amplitude in low frequency and switching frequency, as shown Fig. 7 (a). In Fig. 7 (b), since the unbalanced load leads to large fundamental current in neutral line, the 50Hz component has high value (19.65A) for case 2. Additionally, the 3<sup>rd</sup>-order component is also obvious for case 1 and 2, as shown in Fig. 7 (c). In high frequency range, the effects on DC current ripple are less and DC current ripples are similar for base case, case 1 and 2, as shown in Fig. 7 (d), (e) and (f).

Fig. 7 DC capacitor current spectrum, (a) under balanced load condition and dead time is zero (base case), comparison of base case, case 1, case 2 and proposed strategy at different frequency range (b), (c), (d), (e), (f) are capacitor current spectrum zoomed in at 50Hz, low frequency,  $f_s$ ,  $2f_s$ , and  $3f_s$ , respectively.

Moreover, the DC-link in this paper is configured by a series connection of two AECs, as shown Fig. 2, with the parameters given in Table II in order to meet the requirements in terms of operating DC-link voltage and capacitance. Thus, the full DC-link capacitor current is seen by both capacitors. For the analysis, it is further assumed that the capacitors share the DC-link voltage equally and that they have identical parameters. In addition, the temperature dependence of the ESR is neglected. Therefore, in combination with the parameters given in Table II the impact of the different control targets on the lifetime of a single capacitor can be estimated.

TABLE II DATA OF DC-LINK CAPACITORS

| Parameters                    | Values |

|-------------------------------|--------|

| Nominal capacitance (uF)      | 4500   |

| Nominal voltage (V)           | 500    |

| Nominal Resr at 100 Hz (mOhm) | 21.1   |

| Thermal resistance (K/W)      | 2.9    |

Based on the capacitor current spectrum depicted in Fig. 7 and the ESR characteristics discussed in Section II the losses of the capacitor for each case are calculated. Subsequently, with respect to the thermal resistance the hotspot temperature increase  $\Delta T_{\rm h}$  is obtained. The results are summarized in TABLE III

TABLE III HOTSPOT TEMPERATURE INCREASE AND RELATIVE LIFETIME OF DIFFERENT CASES

| Simulation case | AEC<br>RMS<br>current<br>Icap (A) | Hotspot<br>temperature<br>increase ΔT <sub>h</sub><br>(°C) | Relative hotspot temperature change $\Delta T_{h,rel}$ (°C) | Relative lifetime $L_{\rm rel}$ referred to base case (pu) |

|-----------------|-----------------------------------|------------------------------------------------------------|-------------------------------------------------------------|------------------------------------------------------------|

| Base case       | 0.47                              | 0.01                                                       | 0.00                                                        | 1                                                          |

| Case 1          | 0.69                              | 0.03                                                       | 0.02                                                        | 0.999                                                      |

| Case 2          | 13.90                             | 14.01                                                      | 14.00                                                       | 0.379                                                      |

The base case, is chosen as reference for the following analysis, resulting in  $L_{\rm rel}=1$  and  $\Delta T_{\rm h,rel}=0$ °C. It can be seen that in case of the considered dead time the relative hotspot temperature increase of the AEC is 0.03°C for case 1. This translates in to a relative lifetime of  $L_{\rm rel,1}$ =0.999. Thus, the impact of the dead time on the AEC's lifetime is negligible in this case. In the event of a load unbalance, the lifetime of the capacitor will be dramatically reduced due to the presence of the high 50 Hz component in the capacitor current spectrum. For this case the relative hotspot temperature increase is 14.00°C, which leads to  $L_{rel,2}=0.379$ , thus a reduction in the AEC's lifetime of 62.1% as compared to the base case. The tendency of the obtained results is also indicated by the AEC RMS currents given in Table III. From the analysis of the relative lifetime it is evident that the effect of a load unbalance needs to be considered when designing the DC-link for the LV side converter, since the direct connection of the neutral line causes significant low frequency ripple current components and, thus, high thermal stress for the AEC. Apart from design considerations improving the control strategy is another option for preserving the AEC's lifetime.

## IV VOLTAGE CONTROL STRATEGY TO REDUCE DC RIPPLES

The conventional strategy controls the three-phase AC voltage, as shown in Fig. 3, which includes the positive sequence, negative sequence and the zero sequence component, simultaneously. Thus, the negative and zero sequence component of the voltage at PCC is controlled to be zero, which leads to neutral line current during not ideal conditions. As analyzed above, the DC capacitor lifetime will be significantly reduced because of the large neutral current. In order to solve this problem, an improved control strategy is proposed.

The overall control diagram of the proposed strategy is shown in Fig. 8. The voltage control loop includes positive sequence PCC voltage and negative sequence PCC voltage, which are connected in parallel. The negative sequence voltage control is necessary due to the distribution grid code requirement on voltage unbalanced ratio, which is defined in (9) (less than 2% during most cases).

$$K_{\rm un} = \frac{U_{\rm neg}}{U_{\rm nos}} \tag{9}$$

In order to control the neutral line current and in turn to limit the capacitor current ripples, an extra current control loop is added as shown in Fig. 8. By tuning the neutral current controller gains, the neutral current can be effectively suppressed.

Fig. 8 Overall control diagram of the proposed voltage control

The simulation results of the proposed strategy is shown in Fig. 9. Compared to in Fig. 4 (c), considering the same dead time and unbalanced load, the capacitor current amplitude is significantly reduced, as shown in Fig. 9.

The corresponding DC capacitor current spectrum is also shown in Fig. 7 (b)-(g). It clearly shows that the capacitor current spectrum is significantly reduced, as compared to case 2. The lifetime estimation of the proposed strategy is given in TABLE IV.

The AEC RMS current is reduced to 1.2 A. Based on the DC current spectrum, the relative hotspot temperature change is  $\Delta T_{\rm h,rel}$ =0.08°C, which leads to a relative lifetime of  $L_{\rm rel,3}$ =0.995. Therefore, by applying the proposed control strategy, the current stress and, subsequently, the thermal stress for the AEC is reduced significantly. The reduction in lifetime is decreased to 0.5% and, thus, the AEC lifetime in case of load unbalance is nearly preserved completely.

TABLE IV HOTSPOT TEMPERATURE INCREASE AND RELATIVE LIFETIME OF DIFFERENT CASES

| Simulation case   | AEC<br>RMS<br>current<br>I <sub>cap</sub> (A) | Hotspot<br>temperature<br>increase ΔT <sub>h</sub><br>(°C) | Relative hotspot temperature change $\Delta T_{h,rel}$ (°C) | Relative lifetime $L_{\rm rel}$ referred to base case (pu) |

|-------------------|-----------------------------------------------|------------------------------------------------------------|-------------------------------------------------------------|------------------------------------------------------------|

| Proposed strategy | 1.2                                           | 0.09                                                       | 0.08                                                        | 0.995                                                      |

Fig. 9 Simulation results of the proposed strategy considering 2.5us dead time and unbalanced loads.

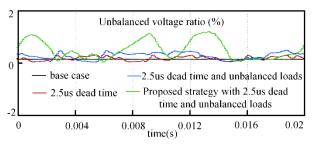

In Fig. 10, it clearly shows that the unbalanced voltage ratio for base case, case 1 and 2 and the proposed strategy are all smaller than 2%, which satisfies the grid code requirement on voltage unbalanced ratio in distribution grid.

Fig. 10 Unbalanced ratio of PCC voltage

#### V CONCLUSIONS

In this paper, challenges of the distribution grid on the ST DC-Link is studied. Based on these impacts, the DC electrolytic

capacitor lifetime is estimated for the ST low voltage side converter. The dead time, nonlinear characteristic of the IGBT and unbalanced loads can lead to increase of DC capacitor current ripples in low frequency range, especially at 50Hz and 150Hz. This ripple current significantly reduces DC electrolytic capacitor lifetime. An improved voltage control strategy is proposed to effectively suppress the neutral line current, significantly reduce the capacitor current ripple and in turn increase the lifetime of the electrolytic capacitor.

#### ACKNOWLEDGEMENT

This work was supported by the European Research Council under the European Union's Seventh Framework Programme (FP/2007- 2013)/ERC Grant Agreement 616344 HEART—the Highly Efficient And Reliable smart Transformer.

#### REFERENCES

- T. Ackermann and V. Knyazkin, "Interaction between distributed generation and the distribution network: operation aspects," *IEEE/PES Transmission and Distribution Conference and Exhibition*, vol. 2. pp. 1357–1362 vol.2, 2002.

- [2] E. J. Coster, J. M. A. Myrzik, B. Kruimer, and W. L. Kling, "Integration issues of distributed generation in distribution grids," *Proceedings of the IEEE*, vol. 99, no. 1. pp. 28–39, 2011.

- [3] G. De Carne, G. Buticchi, Z. X. Zou, and M. Liserre, "Reverse power flow control in a ST-fed distribution grid," *IEEE Trans. Smart Grid*, vol. PP, no. 99. p. 1, 2017.

- [4] M. Liserre, G. Buticchi, M. Andresen, G. De Carne, L. F. Costa, and Z. X. Zou, "The smart transformer: impact on the electric grid and technology challenges," *IEEE Ind. Electron. Magazine*, vol. 10, no. 2. pp. 46–58, 2016.

- [5] C. Kumar, Z. Zou, and M. Liserre, "Smart transformer-based hybrid grid loads support in partial disconnection of MV/HV power system," 2016 IEEE Energy Conversion Congress and Exposition (ECCE). pp. 1–8, 2016.

- [6] R. Zhu, G. De Carne, F. Deng, and M. Liserre, "Integration of large photovoltaic and wind system by means of smart transformer," *IEEE Trans. Ind. Electron.*, vol. PP, no. 99. p. 1, 2017.

- [7] M. Schmela, "PHOTON: Inverter survey 2012 stats," Present. PHOTON's 3rd PV Invert. Conf.

- [8] H. Wang, Y. Yang, and F. Blaabjerg, "Reliability-oriented design and analysis of input capacitors in single-phase transformer-less photovoltaic inverters," 2013 Twenty-Eighth Annual IEEE Applied Power Electronics Conference and Exposition (APEC). pp. 2929–2933, 2013.

- [9] Y. Ko, H. Jedtberg, G. Buticchi, and M. Liserre, "Topology and control strategy for accelerated lifetime test setup of DC-link capacitor of wind turbine converter," 2016 IEEE Applied Power Electronics Conference and Exposition (APEC). pp. 3629–3636, 2016.

- [10] P. Venet, F. Perisse, M. H. El-Husseini, and G. Rojat, "Realization of a smart electrolytic capacitor circuit," *IEEE Ind. Appl. Magazine*, vol. 8, no. 1. pp. 16–20, 2002.

- [11] M. L. Gasperi, "Life prediction modeling of bus capacitors in AC variable-frequency drives," *IEEE Trans. Ind. Appl.*, vol. 41, no. 6. pp. 1430–1435, 2005.

- [12] M. L. Gasperi, "A method for predicting the expected life of bus capacitors," Ind. Applications Conference, 1997. Thirty-Second IAS Annual Meeting, IAS '97., Conference Record of the 1997 IEEE, vol. 2. pp. 1042–1047 vol.2, 1997.

- [13] H. Wang and F. Blaabjerg, "Reliability of capacitors for DC-Link applications in power electronic converters-an overview," *IEEE Trans. Ind. Appl.*, vol. 50, no. 5. pp. 3569–3578, 2014.