## Management and Protection of High-Voltage Direct Current Systems Based on Modular Multilevel Converters

## **Dissertation**

zur Erlangung des akademischen Grades

Doktor der Ingenieurwissenschaften

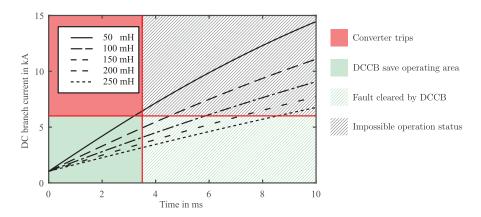

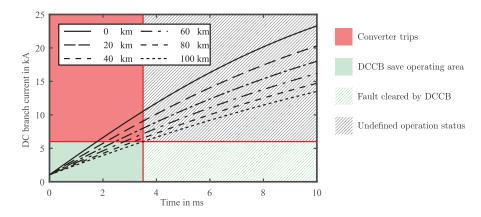

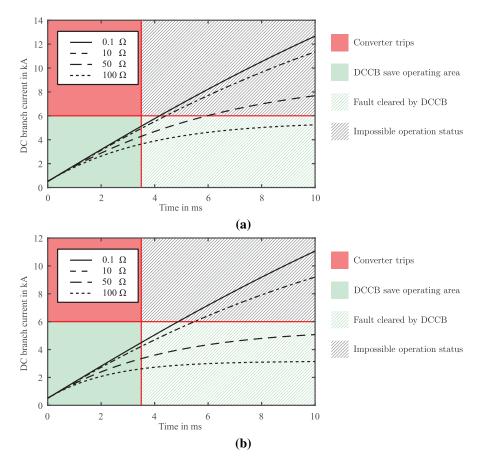

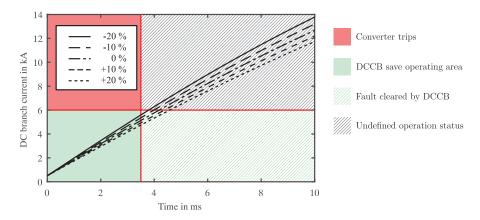

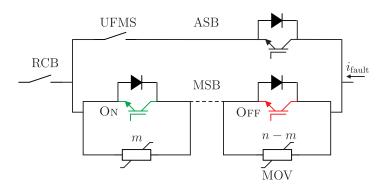

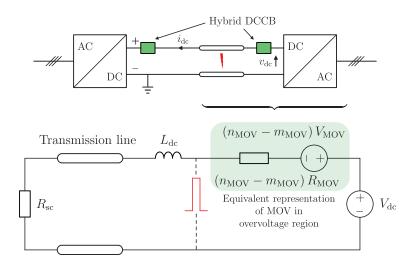

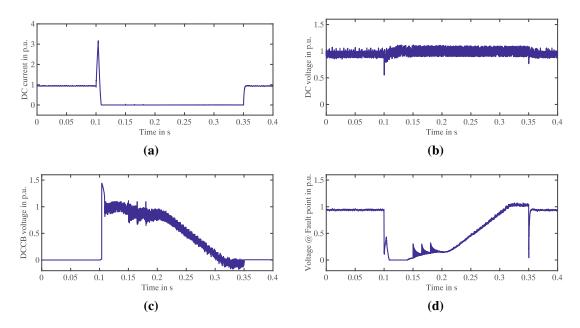

(Dr.-Ing.)

Technische Fakultät

der Christian-Albrechts-Universität zu Kiel

vorgelegt von

M. Sc. Marius Langwasser

*Kiel* 2021

## Erklärung

Ich erkläre an Eides statt, dass ich die Dissertation zum Thema:

Management and Protection of High-Voltage Direct Current Systems Based on Modular

Multilevel Converters

abgesehen von der Betreuung durch Herrn Prof. Marco Liserre selbstständig und ohne Hilfe angefertigt habe und bisher weder ganz noch zum Teil an einer anderen Stelle im Rahmen eines Prüfungsverfahrens vorgelegt, veröffentlicht oder zur Veröffentlichung eingereicht habe. Weiterhin versichere ich hiermit, dass ich die vorliegende Arbeit unter Einhaltung der Regeln guter wissenschaftlicher Praxis der Deutschen Forschungsgemeinschaft angefertigt habe und alle von anderen Autoren wörtlich übernommenen Stellen, wie auch die sich an die Gedankengänge anderer Autoren eng anlehnenden Ausführungen meiner Arbeit besonders gekennzeichnet und die entsprechenden Quellen angegeben sind.

Kiel, den 25. Mai 2021

Marius Langwasser Olshausenstraße 77 24106 Kiel

Gutachter: Prof. Marco Liserre, Ph.D.

Gutachter: Prof. Antonello Monti, Ph.D.

Datum der mündlichen Prüfung: 02.07.2021

Acknowledgment

First of all, I would like to thank my doctoral supervisor and mentor Prof. Marco Liserre,

who followed my research path from the beginning of my master's thesis to this final step

of my doctorate. He convinced me to start this journey and provided me comments and

suggestions on the way to guide me on how to carry out successful research.

I would like to thank also Prof. Antonello Monti (RWTH) for reviewing my thesis and the

interesting discussions and suggestions during the disputation.

A special thanks goes to my mentor and friend Dr.-Ing. Giovanni De Carne, who introduced

me to the power system world and always helped and reassured me, whenever the research

reality caught up with me.

I would like to thank also my colleagues at the Chair of Power Electronics not only for the

interesting topical discussions, but also for coffee and lunch breaks with lots of laughter.

Even though I cannot list all of them, I would like to especially mention Sebastian Brüske

and Holger Jedtberg, who started as supervisors, then became colleagues and finally friends

for introducing me to the research world, motivating me and jointly trying to limit our per-

fectionism.

A huge thanks goes to my family for always being at my side and supporting me during my

studies and the doctorate period.

Finally, I would like express my personal thankfulness and love to my wife Jasmin. There

are a million reasons, why I dedicated this thesis to you, as you encouraged and motivated

me throughout the whole doctorate and you gave me the strength and the belief in my own

abilities to finalize it.

Kiel, August 2021

Marius Langwasser

Contents

## **Contents**

| Det | itsche  | Kurzia   | issung der Arbeit                                                     | IV |

|-----|---------|----------|-----------------------------------------------------------------------|----|

| Eng | slish S | Summar   | у                                                                     | V  |

| Use | d syn   | nbols ar | nd abbreviations                                                      | VI |

| 1.  | Intro   | oduction | n                                                                     | 1  |

|     | 1.1.    | Motiva   | ation of advanced HVdc-based grid services                            | 3  |

|     | 1.2.    | Motiva   | ation of analytical design methods for HVdc circuit breakers          | 4  |

|     | 1.3.    | Motiva   | ation of modular multilevel converter-based HVdc protection           | 5  |

|     | 1.4.    | Resear   | ch proposal                                                           | 6  |

|     | 1.5.    | Structu  | are of this thesis                                                    | 8  |

|     | 1.6.    | List of  | publications                                                          | 9  |

| 2.  | Fun     | dament   | als of VSC-HVdc systems and modular multilevel converters             | 12 |

|     | 2.1.    | VSC-I    | HVdc applications                                                     | 14 |

|     | 2.2.    | VSC-I    | HVdc terminal configurations                                          | 18 |

|     |         | 2.2.1.   | Asymmetrical monopole configuration                                   | 18 |

|     |         | 2.2.2.   | Symmetrical monopole configuration                                    | 19 |

|     |         | 2.2.3.   | Bipolar configuration                                                 | 19 |

|     | 2.3.    | HVdc     | terminals based on modular multilevel converter                       | 21 |

|     |         | 2.3.1.   | Fundamental operation of the MMC                                      | 22 |

|     |         | 2.3.2.   | MMC-HVdc terminal inner control loops and controller design           | 26 |

|     | 2.4.    | Funda    | mentals of HVdc control: External control loops and HVdc grid control | 36 |

|     |         | 2.4.1.   | HVdc converter external control strategies                            | 37 |

|     |         | 2.4.2.   | HVdc grid control strategies                                          | 40 |

|     | 2.5.    | Funda    | mentals of modeling power electronics in grid integration studies     | 43 |

|     | 2.6.    | Funda    | mentals of HVdc protection                                            | 49 |

|     |         | 2.6.1.   | Fault types in HVdc grids                                             | 50 |

|     |         | 2.6.2.   | HVdc grid protection methodologies                                    | 51 |

|     |         | 2.6.3.   | HVdc grid protection philosophies                                     | 52 |

|     | 2.7.    | Summ     | ary and conclusions of the section                                    | 55 |

| 3.  | HV      | de servi | ce provision to ac grids                                              | 56 |

|     | 3.1.    | Overv    | iew of HVdc grid services                                             | 56 |

|     |         | 3.1.1.   | Power flow control and congestion management                          | 57 |

|     |         | 3.1.2.   | Steady-state grid voltage support and fault ride through              | 57 |

|     |         | 3.1.3.   | Black start and system restoration                                    | 59 |

|     |         | 3.1.4.   | Power oscillation damping                                             | 60 |

|     |         | 3.1.5.   | Primary frequency regulation                                          | 63 |

|     |         | 3.1.6.   | Inertia emulation                                                     | 71 |

|     |         | 3.1.7.   | Research questions                                                    | 74 |

II Contents

|    | 3.2. | Primai   | ry frequency regulation with HVdc systems controlling voltage depen-     |      |

|----|------|----------|--------------------------------------------------------------------------|------|

|    |      | dent lo  | oads                                                                     | 75   |

|    |      | 3.2.1.   | Fundamentals of primary frequency regulation controlling voltage         |      |

|    |      |          | dependent loads                                                          | 75   |

|    |      | 3.2.2.   | Analytical results of primary frequency regulation with HVdc sys-        |      |

|    |      |          | tems controlling voltage dependent loads                                 | 84   |

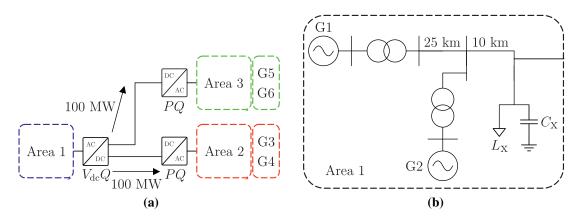

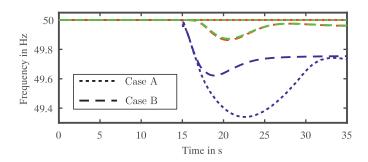

|    |      | 3.2.3.   | Simulations results: Simplified test system - HVdc interconnector .      | 94   |

|    |      | 3.2.4.   | Simulations Results: Large interconnected system - IEEE 39 bus           |      |

|    |      |          | system                                                                   | 98   |

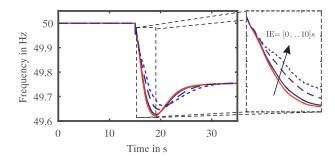

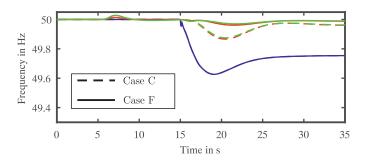

|    | 3.3. | Optim    | ization of frequency support with multi-terminal HVdc systems            | 101  |

|    |      | 3.3.1.   | Analytical results of optimized frequency support in MTdc systems        | 103  |

|    |      | 3.3.2.   | Simulation results of optimized frequency support in MTdc systems        | 106  |

|    | 3.4. | Summ     | ary and conclusions of the section                                       | 112  |

| 4. | Des  | ign of d | lc circuit breakers                                                      | 115  |

|    | 4.1. | Requir   | rement analysis of high voltage dc circuit breakers                      | 115  |

|    |      | 4.1.1.   | Generalized qualitative criteria to evaluate high-voltage dc circuit     |      |

|    |      |          | breaker                                                                  | 116  |

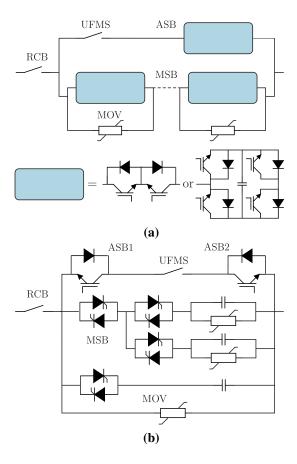

|    |      | 4.1.2.   | High-voltage dc circuit breaker topologies                               | 118  |

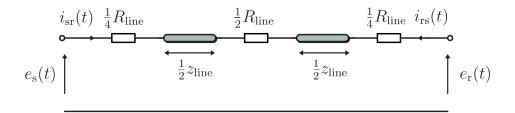

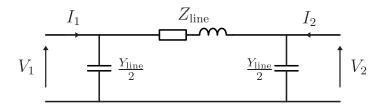

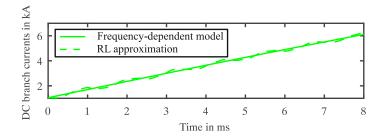

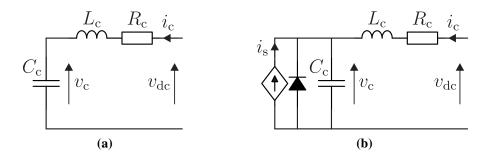

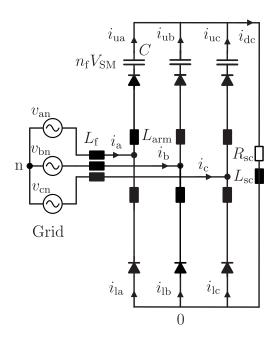

|    | 4.2. | Model    | ing power electronics in dc fault studies                                | 121  |

|    |      | 4.2.1.   | Transmission system modeling                                             | 122  |

|    |      | 4.2.2.   | Modular multilevel converter modeling                                    | 124  |

|    | 4.3. | Fault of | current estimation in multi-terminal HVdc grids considering MMC          |      |

|    |      | contro   | 1                                                                        | 127  |

|    |      | 4.3.1.   | Review of fault current estimation methods                               | 127  |

|    |      | 4.3.2.   | Pole-to-pole fault current calculation in symmetrical monopole MTdc      |      |

|    |      |          | grids considering control dynamics                                       | 134  |

|    |      | 4.3.3.   | Fault current calculation in bipolar MTdc grids considering control      |      |

|    |      |          | dynamics                                                                 | 138  |

|    |      | 4.3.4.   | Simulation results                                                       | 141  |

|    | 4.4. | Fault i  | dentification and adaptive auto-reclosing with modular dc circuit breake | r150 |

|    | 4.5. | Summ     | ary and conclusions of the section                                       | 157  |

| 5. |      |          | ultilevel converter-based HVdc protection                                | 160  |

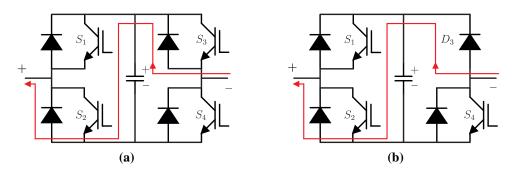

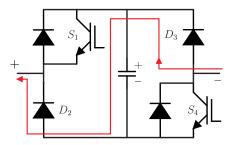

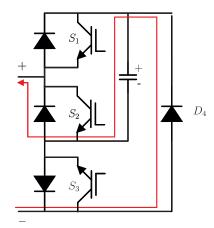

|    | 5.1. | Submo    | odule types for MMC                                                      | 160  |

|    |      | 5.1.1.   | Submodule types for MMC without fault blocking capability                | 160  |

|    |      | 5.1.2.   | Submodule types for MMC with fault blocking capability                   | 162  |

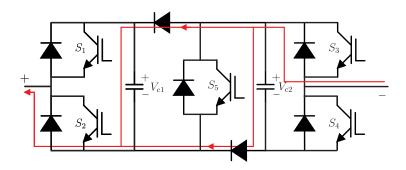

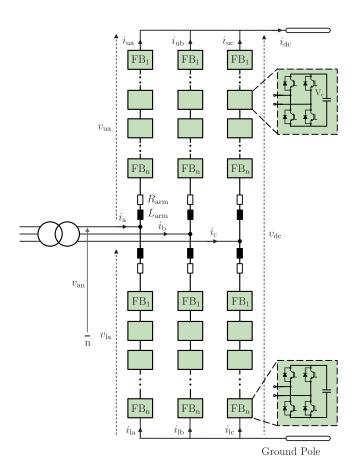

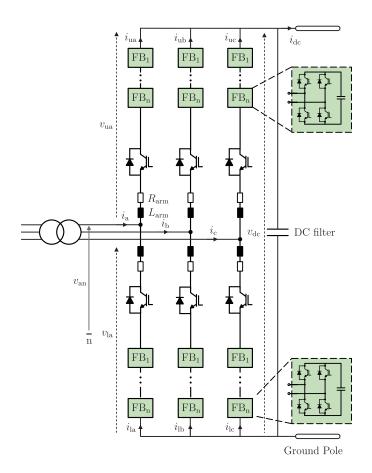

|    | 5.2. | MMC      | architectures with fault blocking capability                             | 171  |

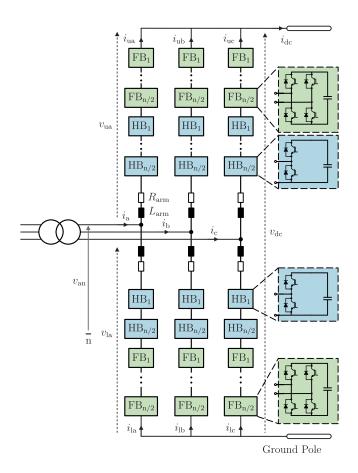

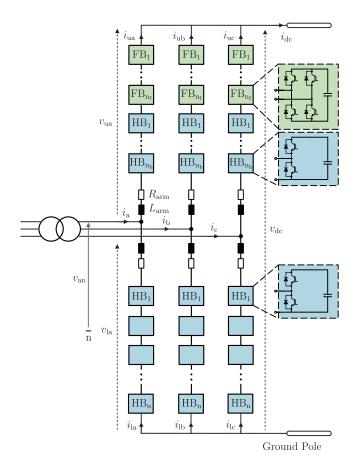

|    |      | 5.2.1.   | Hybrid modular multilevel converter                                      | 172  |

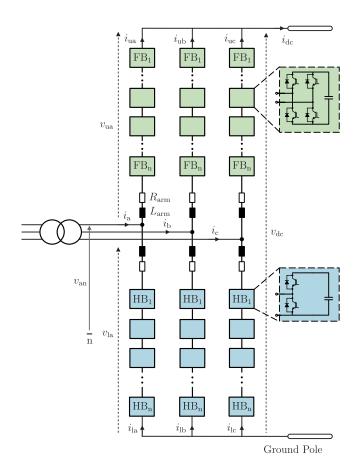

|    |      | 5.2.2.   | Hybrid arm modular multilevel converter                                  | 180  |

|    |      | 5.2.3.   | Alternate arm converter                                                  | 182  |

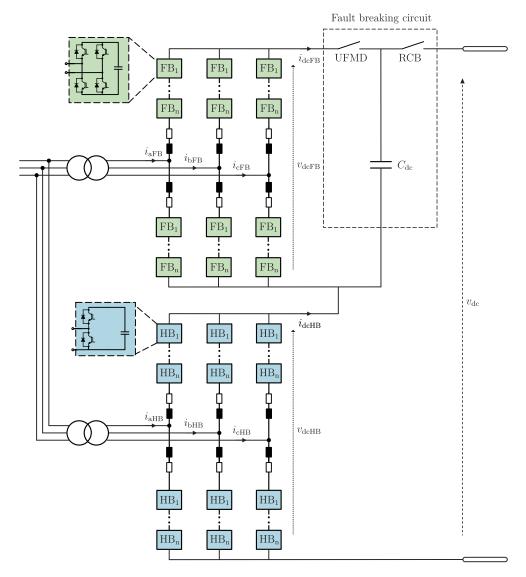

|    |      | 5.2.4.   | Hybrid cascaded multilevel converter                                     | 186  |

Contents

|      |       | 5.2.5.   | Research question                                               | 187 |

|------|-------|----------|-----------------------------------------------------------------|-----|

|      | 5.3.  | Hybrid   | d arm MMC with a reduced number of bipolar submodules and fault |     |

|      |       | blockii  | ng capability                                                   | 187 |

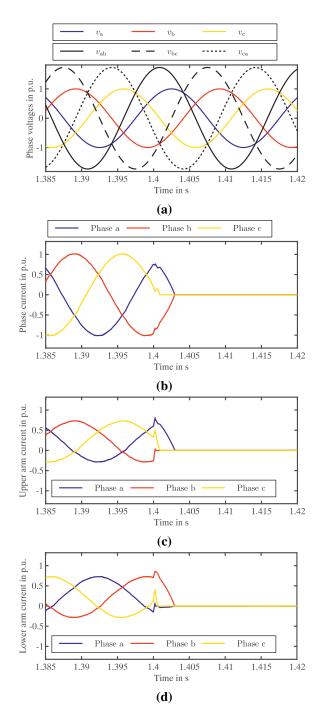

|      |       | 5.3.1.   | Topology of RHA-MMC                                             | 187 |

|      |       | 5.3.2.   | DC fault current blocking capability of RHA-MMC                 | 188 |

|      |       | 5.3.3.   | Submodule over-voltage determination of RHA-MMC in fault block- |     |

|      |       |          | ing state                                                       | 194 |

|      |       | 5.3.4.   | Simulation results of RHA-MMC                                   | 196 |

|      | 5.4.  | Summa    | ary and conclusions of the section                              | 201 |

| 6.   | Sum   | ımary, c | conclusions and future research                                 | 203 |

|      | 6.1.  | Summa    | ary and conclusions                                             | 203 |

|      | 6.2.  | Future   | research                                                        | 205 |

| Refe | erenc | es       |                                                                 | 208 |

| List | of Fi | gures .  |                                                                 | 224 |

| List | of Ta | ibles .  |                                                                 | 233 |

## **Deutsche Kurzfassung der Arbeit**

Das Stromnetz erfährt in Folge der Integration von Erneuerbaren Energien und der Elektrifizierung des Verkehrs- und Wärmesektors tiefgreifende Veränderungen. Diese neuen Ressourcen sind typischerweise nicht planbar und abhängig von externen Faktoren (z. B. Wetter, Nutzerverhalten). Beide Aspekte führen zu schwerer vorhersehbarer Energieerzeugung und -bedarf und begünstigen so eine erhöhte Leistungsvariabilität. Folglich werden Störungen und das Aufrechterhalten der Versorgungsqualität herausfordernder, da schon geringe Leistungsungleichgewichte zu großen Frequenzschwankungen mit schnellen Transienten führen. Um diese Probleme zu bewältigen, benötigt das Energiesystem ein Infrastrukturupgrade sowie ein verbessertes Regelungssystem. In dieser Hinsicht können Hochspannungsgleichstromübertragungssysteme (HGÜ) die Regelbarkeit des Stromnetzes erhöhen und so die Integration zuvorgenannter Technologien fördern.

Diese Arbeit erweitert den Stand der Technik für HGÜ, indem die Modellierung, Regelung und der Schutz von HGÜ basierend auf modularen Multilevelumrichtern mit Fokus auf die Erbringung von Netzdienstleistungen für das Übertragungsnetz adressiert werden.

Studien zu HGÜ-Regelungs- und Schutzkonzepten erfordern eine akkurate Modellierung in stark voneinander abweichenden Zeitbereichen. Diese Arbeit stellt daher als ersten Schritt eine Richtlinie zur Bestimmung des notwendigen Modellierungsdetailgrads leistungselektronischer Komponenten in Abhängigkeit des betrachten Stromnetzphänomens vor.

Ausgehend von der geeigneten Modellierung für Stromnetzstudien, präsentiert diese Arbeit einen Ansatz zur HGÜ-basierten Primärfrequenzregelung, welcher den Lastbedarf flexibler, spannungsabhängiger Lasten mittels kontrollierter Blindleistungseinspeisung und entsprechender Netzspannungsregelung anpasst. Diese Lösung ermöglicht eine schnelle und akkurate Leistungsbalancierung und minimiert so die Frequenzschwankungen im Übertragungsnetz sowohl in der asynchronen als auch in der netzintegrierten HGÜ-Anwendung.

Eine zentrale Herausforderung für HGÜ ist eine geeignete Auslegung des Schutzsystems und insbesondere der Gleichstromschutzschalter, welche eine Analyse der Fehlerströme für eine Vielzahl an Netzzuständen und Parametern erfordern. Diese Arbeit nutzt das erworbene Wissen zu Modellierung und Regelung der HGÜ, um eine schnelle und akkurate Methodik zur Fehlerstromschätzung für modulare Multilevelumrichter-basierte HGÜ zu entwickeln. Unter Einbeziehung der HGÜ-Regelung ermöglicht der Algorithmus akkurate Prognosen des Maximalwerts sowie der Steilheit der Stromtransiente mit im Vergleich zu simulationsbasierten Verfahren stark verkürzter Rechenzeit.

Zuletzt wird in dieser Arbeit ein weiteres HGÜ-Schutzkonzept basierend auf einer hybriden Mischzellenumrichtertopologie ohne zusätzliche Schutzschalter untersucht, welches mit der minimal notwendigen Anzahl bipolarer Zellen eine mit Schutzschaltern vergleichbare Fehlerklärung und tolerierbare Zellüberspannungen erzielt.

## **English Summary**

The electrical grid is undergoing large changes due to the massive integration of renewable energy systems and the electrification of transport and heating sectors. These new resources are typically non-dispatchable and dependent on external factors (e.g., weather, user patterns). These two aspects make the generation and demand less predictable, facilitating a larger power variability. As a consequence, rejecting disturbances and respecting power quality constraints gets more challenging, as small power imbalances can create large frequency deviations with faster transients.

In order to deal with these challenges, the energy system needs an upgraded infrastructure and improved control system. In this regard, high-voltage direct current (HVdc) systems can increase the controllability of the power system, facilitating the integration of large renewable energy systems.

This thesis contributes to the advancement of the state of the art in HVdc systems, addressing the modeling, control and protection of HVdc systems, adopting modular multilevel converter (MMC) technology, with focus in providing services to ac systems.

HVdc system control and protection studies need for an accurate HVdc terminal modeling in largely different time frames. Thus, as a first step, this thesis presents a guideline for the necessary level of deepness of the power electronics modeling with respect to the power system problem under study.

Starting from a proper modeling for power system studies, this thesis proposes an HVdc frequency regulation approach, which adapts the power consumption of voltage-dependent loads by means of controlled reactive power injections, that control the voltage in the grid. This solution enables a fast and accurate load power control, able to minimize the frequency swing in asynchronous or embedded HVdc applications.

One key challenge of HVdc systems is a proper protection system and particularly dc circuit breaker (CB) design, which necessitates fault current analysis for a large number of grid scenarios and parameters. This thesis applies the knowledge developed in the modeling and control of HVdc systems, to develop a fast and accurate fault current estimation method for MMC-based HVdc system. This method, including the HVdc control, achieved to accurately estimate the fault current peak value and slope with very small computational effort compared to the conventional approach using EMT-simulations.

This work is concluded introducing a new protection methodology, that involves the fault blocking capability of MMCs with mixed submodule (SM) structure, without the need for an additional CB. The main focus is the adaption of the MMC topology with reduced number of bipolar SM to achieve similar fault clearing performance as with dc CB and tolerable SM over-voltage.

## Used symbols and abbreviations

## **General symbols**

### **General symbols**

| ( . )      | TT.          |               |

|------------|--------------|---------------|

| 11( f \ 11 | Time_war     | iant variable |

| u(t), u    | 1 IIIIC- vai | rant variable |

*û* Peak value

U Constant value, average value

$ilde{u}$  Phasor  $ilde{U}$  Matrix  $ilde{\Delta}$  Variation

(s) Laplace domain operator(t) Time domain operator

### **Superscripts**

\* Reference

i i-th component

### **Subscripts**

0 Initial value a, b, c Phase a, b, c

ac Alternating current

b Base value for power, voltage, and current

dc Direct current

d,q Rotating dq-reference frame components

Lower arm componentLine-to-line component

maxMaximum valueminMinimum valuenomNominal value

n Negative pole componentp Positive pole componentph Phase-to-neutral component

SM Submodule

u Upper arm component

## **Special symbols**

$lpha_{c,ac}$  MMC output current controller closed-loop bandwidth  $lpha_{i,ac}$  MMC output current controller integral part bandwidth  $lpha_{Wdc}$  MMC dc bus energy controller proportional part bandwidth  $lpha_{i,Wdc}$  MMC dc bus energy controller integral part bandwidth

$\beta$  Phase constant

$\chi$  Load active power to voltage sensitivity

$\delta$  Angle between sending and receiving end voltages

$\delta\theta$  PWM carrier phase shift between the upper and the lower arm in the MMC

$\phi_{m,ac}$  MMC output current controller phase margin  $\theta_x$  Generators rotational angle of the x-th area PWM carrier phase shift of i-th submodule

$\rho_{\rm f}$  Frequency droop per unit decrement of the active power

$\Sigma R_{\rm on}$  Sum of submodule IGBT on-state resistances

$\tau_{\text{line}}$  Time constant of transmission line pi-section representation

$\tau_{\rm x}$  Internal dynamic state of the turbine transfer function of the x-th area

$\omega$  Angular grid frequency, nominal angular speed of rotation

$\omega_1$  Angular grid frequency in area 1  $\omega_2$  Angular grid frequency in area 2

$\omega_{g1}$  MMC angular grid frequency fundamental component

$\omega_{r}$  Rotor speed of synchronous generators  $\omega_{s}$  MMC angular sampling frequency  $\xi$  Traveling wave reflection coefficient  $\zeta$  Traveling wave refraction coefficient

a Symmetrical optimum dynamic coefficient

A Updated network incidence matrix without virtual nodes

**A**<sub>t</sub> Network incidence matrix

A<sub>t1</sub> Real node columns of network incidence matrix

A<sub>t2</sub> Virtual node columns of network incidence matrix

**A**<sub>z</sub> Bipolar network incidence matrix

$A_{z1}$  Real node columns of bipolar network incidence matrix

$c_{\text{line}}$  Equivalent line capacitance per unit length

C<sub>arm</sub> Equivalent MMC arm capacitance of series connected FBSM

$C_{\rm c}$  MMC dc side equivalent capacitance

$C_{\rm dc}$  HVdc bus capacitor

$C_{\text{eq}}$  Equivalent MMC capacitor (of simplified MMC average value model)

$C_{\text{line}}$  Lumped equivalent line capacitance

$C_{\text{par}}$  Parasitic cable capacitance  $C_{\text{SM}}$  MMC submodule capacitance

$d_{\Delta dc}$  Differential power controller proportional gain

$d_{\omega}$  Virtual friction constant

$d_{\omega 1}$  Area 1 power oscillation damping controller proportional gain  $d_{\omega 2}$  Area 2 power oscillation damping controller proportional gain

$d_{

m dc}$   $V_{

m dc}$ -P-droop control proportional gain  $d_{

m f}$   $V_{

m dc}$ -f-droop control proportional gain  $d_{

m idc}$   $V_{

m dc}$ - $I_{

m dc}$ -droop control proportional gain

$d_{\rm IE}$  Emulated inertia controller proportional gain

$d_{\rm p}$  P-f-droop control proportional gain

D Load damping constant  $E_{\rm r}$  Receiving end grid voltage  $E_{\rm s}$  Sending end grid voltage

f Grid frequency

$F_{\text{HP}}$  Turbine power fraction of high pressure section  $F_{\text{LP}}$  Turbine power fraction of low pressure section

$g_x$  Internal dynamic state of the governor transfer function of the x-th area

G Isochronous governor proportional gain

$G_{\rm ac}$  MMC output current controller electrical plant transfer function  $G_{\rm c,ac}$  MMC output current controller closed-loop transfer function

$G_{cir}$  MMC circulating current controller electrical plant transfer function

$G_{\text{delay}}$  Modulation and computation delay transfer function  $G_{\text{PI.ac}}$  MMC output current PI-controller transfer function

$G_{\text{o,ac}}$  MMC output current controller open-loop transfer function  $G_{\text{Wdc}}$  MMC dc bus energy controller electrical plant transfer function

$G_{\rm x}$  Governor transfer function of the x-th area

H System inertia constant

$H_{\text{IE}}$  Emulated system inertia constant  $i_{\text{bij}}$  Branch current from node i to node j

in negative pole of multi-terminal HVdc model

*i*<sub>c</sub> Circulating current MMC

*i*<sub>ci</sub> Injected current from i-th MMC in multi-terminal HVdc model

*i*<sub>d</sub> MMC output current d-component

$i_{\rm dc}$  DC current

$i_{dc,bus}$  DC bus input current

$i_{ij}$  Branch current from node i to node j

in positive pole multi-terminal HVdc model

*i*<sub>1</sub> Lower arm current MMC

$i_{par}$  Current through parasitic cable capacitors

$i_{\rm q}$  MMC output current q-component  $i_{\rm trip}$  Converter fault current trip threshold

*i*<sub>s</sub> Phase (output) current MMC

*i*<sub>SM</sub> MMC submodule current

$i_{\text{sMMC.i}}$  Source current from i-th MMC in multi-terminal HVdc model

*i*<sub>u</sub> Upper arm current MMC

$i_{\rm X}$  Internal dynamic state of the rotor inertia and load damping transfer

function of the x-th area

$I_{\rm r}$  Receiving end current  $I_{\rm S}$  Sending end current

$I_{\rm x}$  Rotor inertia and load damping transfer function of the x-th area

J Moment of inertia of rotating masses

*k*<sub>bal</sub> Decentralized MMC submodule balancing controller proportional gain

$\begin{array}{lll} k_{\rm i,ac} & {\rm MMC~output~current~controller~integral~gain} \\ k_{\rm i,cir} & {\rm MMC~circulating~current~controller~integral~gain} \\ k_{\rm i,Wdc} & {\rm MMC~dc~bus~energy~controller~integral~gain} \\ k_{\rm p,ac} & {\rm MMC~output~current~controller~proportional~gain} \\ k_{\rm p,cir} & {\rm MMC~circulating~current~controller~proportional~gain} \\ k_{\rm p,Wdc} & {\rm MMC~dc~bus~energy~controller~proportional~gain} \\ \end{array}$

$k_{\text{Vdc}}$  Droop-constant of the  $P_{\text{dc}}$ - $V_{\text{dc}}$ -droop control  $k_{\text{Vdc}i}$  Droop-constant of the  $I_{\text{dc}}$ - $V_{\text{dc}}$ -droop control

K Network capacitance matrix

$K_{\text{fp}}$  Load active power to frequency dependency  $K_{\text{p}}$  Load active power to voltage dependency

$l_{\text{fault}}$  Fault distance to terminal

$l_{line}$  Equivalent line inductance per unit length

L Updated network inductance matrix without virtual nodes

$L_{\text{arm}}$  Arm inductance MMC

$L_{\rm c}$  MMC dc side equivalent inductance  $L_{\rm dc}$  DC current limiting inductance

$L_{\rm eq}$  Equivalent inductance of simplified MMC average value model

$L_{\rm f}$  MMC ac-side filter inductance  $L_{\rm line}$  Lumped equivalent line inductance

$L_{t}$  Network inductance matrix  $L_{sc}$  Short circuit path inductance

*m* Modulation index

$m_{\rm dc}$  MMC dc modulation index

$m_{\rm MOV}$  Number of bypassed dc CB main breaker modules

*m*<sub>o</sub> MMC over-modulation index*M* Equivalent system inertia

$n_{\rm cd}$  Number of CDSM in one MMC arm  $n_{\rm cs}$  Number of CSSM in one MMC arm

$n_{\rm f}$  Number of FBSM in one MMC arm

$n_{\rm f,n}$  Number of negative state FBSM in one MMC arm

$n_h$  Number of HBSM in one MMC arm  $n_i$  i-th node in multi-terminal HVdc model

$n_1$  MMC lower arm insertion index

$n_1^i$  MMC insertion index of i-th submodule in lower arm

$n_{\text{MOV}}$  Number of dc CB main breaker modules

$n_{\rm mt}$  Number of converter terminals in multi-terminal HVdc system

$n_{\rm SM}$  Total number of MMC submodules per arm

$n_{\rm u}$  MMC upper arm insertion index

$n_{ij}^{i}$  MMC insertion index of i-th submodule in upper arm

$p_{\rm i}$  Per unit share of constant current load  $p_{\rm p}$  Per unit share of constant power load

$p_{\rm x}$  Proportional share of frequency support in the x-th area

$p_z$  Per unit share of constant impedance load

P Active power

$P_{39\text{bus}}$  HVdc active power set-point in IEEE 39-bus system  $P_{\Delta}$  Differential power in multi-terminal HVdc systems  $P_{\text{cm}}$  Common power in multi-terminal HVdc systems

$P_{\text{dc,bus}}$  DC bus input power

P<sub>e</sub> Synchronous generators' electrical power

$P_{\text{kundur}}$  HVdc active power set-point in Kundur benchmark system

P<sub>L</sub> Load active power consumption

$P_{\rm m}$  Synchronous generators' mechanical power

P<sub>o</sub> Terminal output power in multi-terminal HVdc systems

$P_{\rm r}$  Receiving end active power

Q Reactive power

$Q_{\rm r}$  Receiving end reactive power

$r_{\text{line}}$  Equivalent line resistance per unit length

R Governor frequency droop constant

**R** Updated network resistance matrix without virtual nodes

$R_{\rm arm}$  Arm resistance MMC

$R_{\rm c}$  MMC dc side equivalent resistance

$R_{\text{eq}}$  Equivalent resistance of simplified MMC average value model

$R_{\rm f}$  MMC ac-side filter resistance  $R_{\rm line}$  Lumped equivalent line resistance

$\mathbf{R}_{\mathrm{t}}$  Network resistance matrix  $R_{\mathrm{sc}}$  Short circuit path resistance

S Apparent power

S<sub>i</sub> i-th switch of MMC submodule

$S_{\text{rated}}$  Nominal power rating of synchronous generators

*t* Time

t<sub>d</sub> Communication delay of primary frequency regulation

$t_{\text{op}}$  DC CB operating time T Fundamental period

T<sub>ac</sub> MMC output current controller electrical plant time constant

$T_{\rm CH}$  Turbine main inlet volume time constant

$T_{\rm delay}$  Modulation and computation delay time constant in MMC

T<sub>e</sub> Synchronous generators' electrical torque

$T_{\rm G}$  Governor time constant

$T_{i,ac}$  MMC output current controller time constant  $T_{i,cir}$  MMC circulating current controller time constant  $T_{i,Wdc}$  MMC dc bus energy controller time constant

$T_{\rm m}$  Synchronous generators' mechanical torque

$T_{\rm p}$  Load recovery time constant  $T_{\rm RH}$  Turbine reheater time constant

$T_{\rm s}$  MMC sampling period

$T_{\rm x}$  Turbine transfer function of the x-th area

$v_{\rm ac}$  AC voltage, grid voltage

$v_{\rm arm}$  MMC arm voltage

*v*<sub>arm,dc</sub> MMC dc-side arm voltage

v<sub>c</sub> Inner voltage MMC

$v_{ci}$  Voltage across equivalent capacitor

of i-th MMC in multi-terminal HVdc model

$v_{\rm dc}$  DC voltage

$v_{par}$  Voltage across parasitic cable capacitors

*v*<sub>1</sub> Lower arm voltage MMC

$v_{ll,ab}$  Line-to-line voltage between phase a and phase b

$v_{\rm ldc}$  Lower arm dc voltage

$v_{n0}$  Voltage between ac neutral point and dc side ground

$v_{\rm s}$  Output side emf MMC  $v_{\rm u}$  Upper arm voltage MMC  $v_{\rm udc}$  Upper arm dc voltage

$v_{xn}$  Phase-to-neutral voltage of phase x

V<sub>ac</sub> MMC output current controller electrical plant proportional gain

$V_{\rm SM}^{\Sigma}$  Sum capacitor voltage MMC

$V_{c,i}$  MMC submodule capacitor voltage of i-th capacitor

$V_{\rm L}$  Load voltage at point of connection  $V_{\rm PL}$  Arrester protection voltage level  $V_{\rm o}$  MMC submodule output voltage

V<sub>SM</sub> Nominal MMC submodule voltage

$W_{\rm ac}$  Effective AAC ac-side energy

$W_{\rm dc}$  Effective MMC/AAC dc bus energy

$W_{\rm MMC}$  MMC energy equilibrium

*x* Position at the line

$x_{\text{fault}}$  Fault position at the line

$X_{\rm ac}$  Lumped equivalent transmission line impedance

Y Turbine control valve position  $Y_{\text{line}}$  Lumped equivalent admittance of

transmission line pi-section representation

Z<sub>c</sub> Characteristic line impedance

Z<sub>1</sub> Equivalent wave impedance of transmission line

$Z_{\text{line}}$  Lumped equivalent impedance of

transmission line pi-section representation

$Z_x$  Equivalent wave impedance at point x

### **Abbreviations**

ac

AAC alternate arm converter

ADSM asymmetrical double submodule

AFCE analytical fault current estimation

ASB auxiliary semiconductor breaker

AVR automatic voltage regulation

BESS battery energy storage system

alternating current

CB circuit breaker

CCSM cross-connected submodule

CIGRE Conseil International des Grands Reseaux Electriques

CDSM clamp double submodule CSSM clamp single submodule

dc direct current

DBSM diagonal bridge submodule

DSO distribution system operator

EMT electro-magnetic transient

ENTSO-E European Network of Transmission System Operators for Electricity

ESS energy storage system

FACTS flexible ac transmission system

FB full-bridge

FC flying capacitor

FF feed forward

FRT fault ride through

HB half-bridge

HCMC hybrid cascaded multilevel converter

HMMC hybrid modular multilevel converter

HA-MMC hybrid arm modular multilevel converter

HV high-voltage

HVac high-voltage alternating current

HVdc high-voltage direct current

IE inertia emulation

IEEE Institute of Electrical and Electronics Engineers

IGBT insulated gate bipolar transistor

LCC line commutated converter

LV low-voltage

LVRT low-voltage ride through

MMC modular multilevel converter

MMCC modular multilevel cascade converter

MOSFET metal oxide semiconductor field-effect transistor

MOV metal oxide varistor

MSB main semiconductor breaker

MTdc multi-terminal high-voltage direct current

MV medium-voltage

NPC neutral point clamped

OHL overhead line

OLTC on-load tap changer

PCC point of common coupling

P2G pole-to-ground P2N pole-to-neutral P2P pole-to-pole

PE power electronics

PFR primary frequency regulation

PI proportional-integral PLL phase-locked loop

POD power oscillation damping PR proportional-resonant

PV photo-voltaic

RCB residual current breaker

RES renewable energy system

RoCoF rate of change of frequency

SCDSM series connected double submodule

SM submodule

ST Smart Transformer

STATCOM static synchronous compensator

TIV transient interruption voltage

TSO transmission system operator

U-FBSM unipolar full-bridge submodule

UFMS ultra-fast mechanical switch

VDE Verband der Elektrotechnik Elektronik Informationstechnik e. V.

VDL voltage-dependent loads VSC voltage source converter

## 1. Introduction

The European Network of Transmission System Operators for Electricity (ENTSO-E) state in 2019 [1]:

## High voltage direct current (HVdc) is an increasingly important technology for transferring electrical power in the European transmission grid.

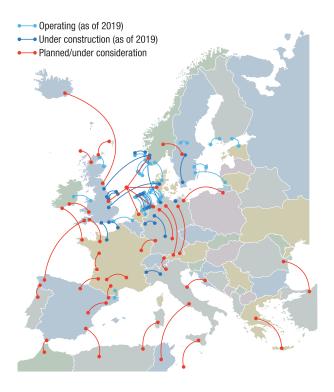

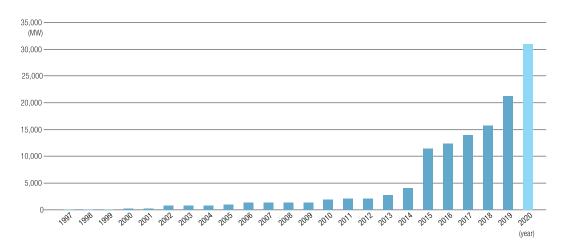

In this sense, HVdc systems play a key role in the future development of the European (see Fig. 1.1) and worldwide power system [2]. System operators all over the world see HVdc systems as a possibility to tackle the current and future challenges in the electrical grid (compare worldwide installed capacity in Fig. 1.2), which are introduced by the global trends towards decarbonization, large scale integration of renewable energy systems (RES) with fluctuating power generation, and electrification of transport and heating sectors [1]. The decommissioning of conventional rotating power plants, moreover, leads to low system inertia and the agglomeration of the RES power plants in remote grid areas requires bulk power transfer over large distances. In this scenario, the HVdc's advanced functionalities are considered essential for the secure and efficient grid operation in the future. In addition, from a non-technical perspective, HVdc can help to establish a transnational energy market, potentially also combining different synchronous areas [1].

To date, HVdc systems are mostly applied to connect two asynchronous, non-embedded ac systems or for bulk power transfer through overhead transmission lines and submarine ca-

Fig. 1.1: HVdc installations in Europe (Status 2019/2020) [2].

Fig. 1.2: Global trend of total MW capacity of HVdc installations 1997-2020 [2].

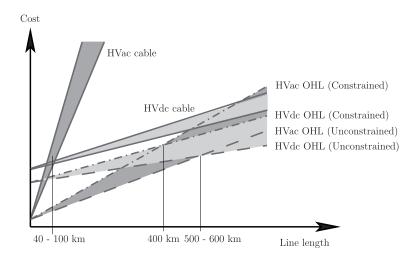

Fig. 1.3: Cost breakdown for HVac and HVdc systems (adapted from [4]).

bles [1]. In these applications, HVdc systems present a number of advantages over their high-voltage alternating current (HVac) counterpart. First, HVdc systems eliminate the reactive power requirement and reduce the operational losses, which enables long-distance power transmission through cables or overhead lines. Also, the power transfer capability of a single conductor is higher and the HVdc can be installed with reduced right of way, since only a maximum of two instead of the three ac conductors are required [2, 3]. Moreover, the HVdc systems enable asynchronous active power transfer and independent reactive power provision, which prevents cascading failures and can help to stabilize the grid. However, due to the much more complex system equipment, such as transformers, circuit breakers and protection components and especially the high costs of the power electronics parts, HVdc systems are only economically rational beyond a certain break-even distance [1]. The break-even distance varies with technical and non-technical constraints (e.g. easier permitting process, more open space to place transmission lines), so that the two technologies compete within a certain range as indicated in Fig. 1.3.

## 1.1. Motivation of advanced HVdc-based grid services

Especially the growing technology readiness of modular multilevel converter (MMC)-based HVdc systems, which to date reach voltage levels of up to  $\pm 500$  kV and power transmission capacity of up to 3000 MW per terminal, facilitates the provision of grid services to guarantee power supply continuity and grid stability under the future grid scenario. Depending on the application of the HVdc system, it is more suited for active power related services, which is the case for long HVdc corridors or interconnectors, or the provision of reactive power related services, valid for embedded HVdc systems in highly meshed ac grids [5]. Many different services have been proposed in the last couple of years to address classical power system problems, such as power flow control and curative congestion management [5, 6], voltage and reactive power control both in steady-state [7] and dynamic condition [8, 9], and damping of power oscillations to increase the rotor angle stability [10, 11, 12]. Moreover, HVdc systems are also highly suitable to support the active power and frequency control [13, 14, 15] and emulate virtual inertia [16, 17, 18], especially under low inertia conditions, which result from the de-commissioning of conventional power plants [19], and can act as a black-start resource for grid restoration purposes [20, 21].

However, the provision of frequency services with HVdc systems, such as primary frequency regulation and inertia emulation, has one common drawback: If no additional source of energy by e.g. either wind farms or battery energy storage systems is provided, unwanted disturbances occur in the supporting grid areas [15]. Moreover, embedded HVdc systems, which by definition inhabit both terminals in the same synchronous area and thus the two terminal frequencies are strongly coupled [22], are to date not suitable to damp frequency oscillations by simple active power modulation, as the HVdc itself is not a source of energy [5].

Flexible, voltage-dependent loads have already been considered in the balancing of load demand and power generation as well as for the provision of services for a couple of years [23] and shaping their power consumption by controlled grid variation has seen several applications with static var compensators [24], synchronous condensers [25], and smart transformers [26]. Thus, it is a logical consequence to extend this concept to HVdc systems to fully exploit their potential in frequency service provision. What has to be noted, is that the necessary change in the grid voltage to shape the loads' power consumption by HVdc systems is restricted by the current grid codes of ENTSO-E [27] and technical requirements for HVdc connection of the German association Verband der Elektrotechnik Elektronik Information-stechnik e. V. (VDE) [28]. Thus, further potential is seen in multi-terminal HVdc systems, in which the power flow can be controlled flexibly [29, 30] and the frequency support can be provided from different loads in the different connected areas.

## 1.2. Motivation of analytical design methods for HVdc circuit breakers

One key challenge since the beginning of HVdc systems is their protection in the event of a short circuit fault. While in ac systems the current naturally crosses through zero, in dc systems an artificial zero crossing must be created to avoid large arc and to guarantee save fault current interruption. Moreover, the low line impedance of dc systems leads to high fault currents with fast transients, which poses additional challenges to the protection system [31].

Depending on the chosen protection philosophy, i.e. if it is allowed to shut down the whole HVdc system (non-selective), subparts of it (partially-selective) or just the faulted line (fullyselective), the primary protection scheme can be based on ac circuit breakers (CB), integrated in converters with fault blocking capability, or based on dc CB, which form the only fullyselective solution [32]. Several different types of dc CB have been proposed, which are passive resonant mechanical breakers [33], active current injection mechanical breakers [33], solid-state breakers [34] or the most-promising technology: hybrid dc CB [35]. While the mechanical breakers suffer from comparably long opening times of the mechanical switch, pure solid-state breakers are to date not commercially available and introduce high on-state losses. Thus, the current focus lays on the development of hybrid dc CB, which combine the high efficiency of mechanical switches with the fast switching properties of solid-state devices. To date only a few hybrid dc CB designs are commercially available [36, 37, 38]. The requirements on dc CB are manifold [31, 39, 40] and it is of utmost importance to evaluate the performance of newly introduced designs as well as the proven ones in a large number of different grid scenarios considering different parameters related to the breaker design itself, as well as the grid operating condition, and secondary technology such as communication infrastructure.

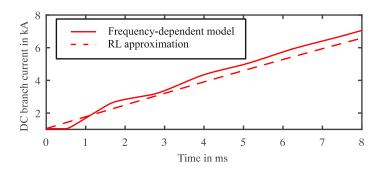

For such purpose, analytical fault current estimation methods are introduced, which can facilitate and speed up the design process of dc CB and hence already save costs in the initial stage of development of dc CB. The recent methods to estimate fault currents in multiterminal HVdc (MTdc) systems can be classified in three types, which are to simulate (e.g. using EMT-simulations) all the possible fault conditions and then evaluate the worst-case scenario [41], the classical analytical approach based on traveling wave analysis [31, 42], and lastly an analytical estimation based on circuit analysis through coupled linear differential equations [43, 44]. However, EMT-simulation based methods are very time consuming and rely on detailed models of converters and transmission systems, which require data not always available due to property restrictions. Indeed, traveling wave analysis is seen as the potential standard in fault current estimation. Nevertheless, it requires the solution of lengthy equations to obtain the exact time-domain solution, which are also valid only in the temporal and spatial proximity of the fault, and thus the approach might be impractical to analyze the individual parameter's impact on the protection design [42]. In contrast, using mesh

analysis based on linear differential equations is regarded as a simple yet accurate approach to determine the most relevant design parameters, fault current slope and maximum peak current, and gives the possibility to investigate multiple parameter variations in short time. However, a clear drawback of existing methods in this field is that they are either applicable only to conventional voltage source converter systems [43] or use oversimplified models of the MMC, which leads to inaccurate estimation results in multi-terminal systems [44].

Hence, it has been identified as an of yet open research field, an analytical fault current estimation method for modular multilevel converter-based MTdc systems, which facilitates parameter variation analysis with reasonable computational effort and is also applicable not only to a single fault scenario or HVdc system configuration, but can be extended to analyze different ones, such as pole-to-pole and pole-to-neutral faults in symmetrical monopole and bipolar HVdc configurations.

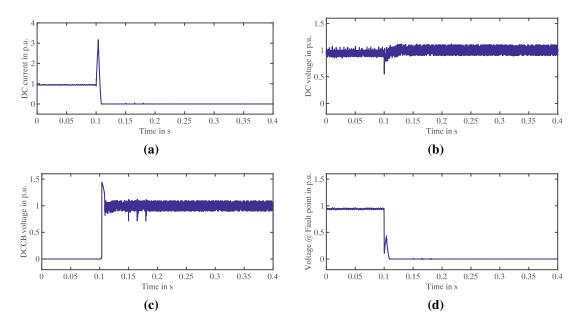

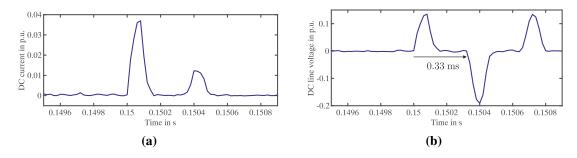

The HVdc CB - being a component of relatively high costs - can be not only applied for its conventional purpose, the fault clearing process, but can also be involved in the reclose and restart function after a temporary fault happened. In order to achieve a faster restoration and to avoid multiple reclosing attempts in the event of permanent faults, recently adaptive autoreclosing strategies have been proposed [45], which identify the fault type prior to initiating the reclosing operation using either the MMC [46] or a hybrid dc CB based on full-bridge architecture in the main breaker path [47]. Thus, it is interesting to investigate, if the same functionality can be also implemented in different dc CB designs, for example in the modular dc CB presented by ABB [36].

## 1.3. Motivation of modular multilevel converter-based HVdc protection

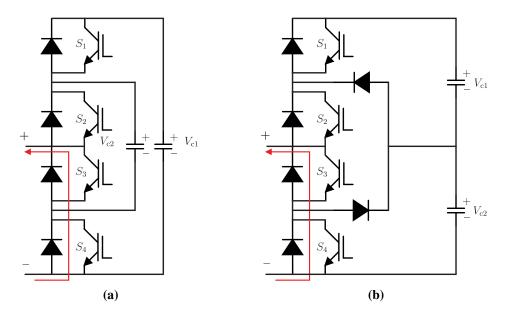

Despite using additional protection equipment such as dc CB, another possible protection method is to embed the dc fault blocking in the converter station [48]. The conventional MMC using half-bridge submodules (SM) is vulnerable to dc faults, because it behaves as an uncontrolled diode rectifier in the blocked state feeding the fault point [49].

Thus, MMCs, which inhabit the fault blocking feature, must provide reverse-biased voltage in the blocked state in order to prevent uncontrolled current flow from the ac to the dc side during the fault [50]. This requires special considerations in the SM, for which several designs, among others the full-bridge SM [50], clamped-double SM [50], or cross-connected SM [49] have been developed. However, these bipolar or asymmetric SM, due to their higher number of switches, increase the converter losses in normal operation and involve higher investment costs than the cost-efficient half-bridge SM.

Hence, new converter architectures have been proposed, which combine the SM with fault blocking ability with half-bridge SM. If both SM types are used in both converter arms, the

topology is known as hybrid MMC [49, 51] and if the SM types are only used in separate arms, e.g. the bipolar SM in the upper arm and the half-bridge SM in the lower arm next to the ground pole, it is defined as hybrid arm MMC [52]. The hybrid arm topology is beneficial compared to the hybrid MMC due to its superior performance under ac faults [53].

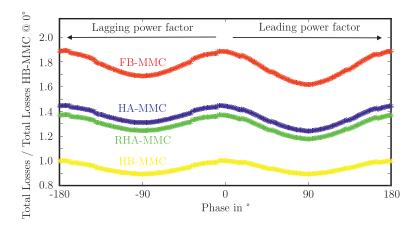

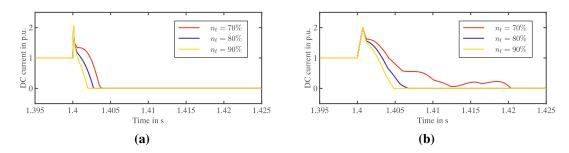

For the hybrid MMC, it has already been shown that the fault blocking function can be also enabled with a reduced number of bipolar SM in order to further reduce the costs of the system [51], which is vital, since the industry involved in the operation of HVdc systems is very cost-sensitive, so that even fractions of a percent in efficiency improvements are important [54]. It is left to be demonstrated, what is the minimum number of SM in a hybrid arm MMC - from an operational perspective - to obtain the fault blocking capability, while maintaining high efficiency.

## 1.4. Research proposal

The aim of the thesis is to investigate the services HVdc systems can provide to the ac grid and to analyze the protection concepts of MTdc systems. Control solutions to implement frequency regulation with minimum impact on the power system and the HVdc system itself are developed. Moreover, the fault currents in HVdc systems are analyzed in order to determine and evaluate criteria for the design of HVdc CB under different grid conditions. Lastly, an adapted design of the hybrid arm MMC is presented to achieve fault blocking capability with increased efficiency in normal operation.

Target I: Development of a control solution for HVdc-based primary frequency regulation and inertia emulation

The first objective is the development and design of an HVdc-based primary frequency regulation and virtual inertia emulation scheme, which has minimum impact on the supporting ac areas in terms of frequency and voltage disturbances. Moreover, the scheme should be effective in suppressing frequency oscillations in both asynchronous HVdc interconnectors and embedded HVdc systems forming parallel, hybrid connection with an existing HVac grid.

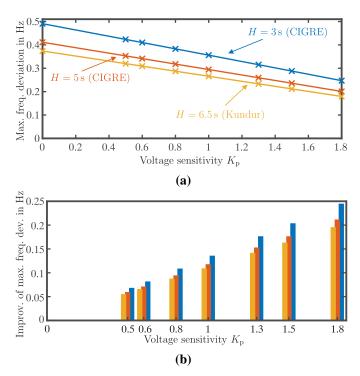

It is proposed to shape (upward and downward) the power consumption of voltage dependent loads in the proximity of the HVdc terminals by varying the grid voltage amplitude in order to raise additional source of energy for the frequency support, which is independent from the synchronous generators and thus does not affect the supporting area's frequency. The effectiveness of the proposed control scheme is analyzed for both asynchronous HVdc interconnectors and embedded HVdc systems considering also the limitations imposed by the current grid codes and power system condition. Furthermore, the control scheme is expanded to MTdc systems, in which the focus is laid on the optimal selection of the frequency

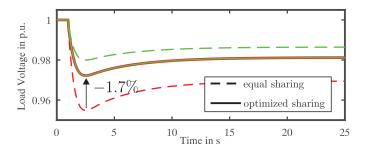

support share. Adjusting the droop coefficients relative to the estimated load voltage dependence (also known as sensitivity), allows the provision of the same frequency service with less impact on the grid voltage in the supporting areas and lower reactive power injection.

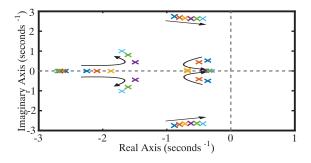

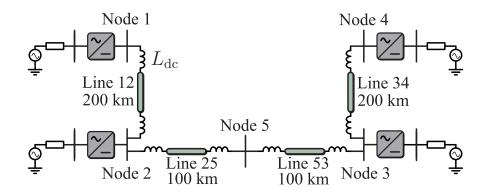

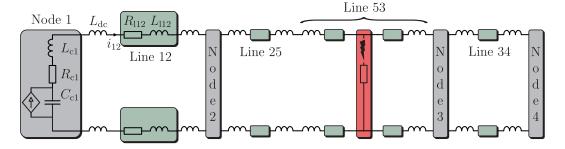

Target II: Analytical fault current estimation in multi-terminal HVdc systems for HVdc circuit breaker design

The second research objective is to investigate the fault current behavior in MMC-based MTdc systems and suitable dc CB designs to protect such systems. A generalized list of criteria is developed from the numerous existing studies to evaluate the suitability of hybrid HVdc CB designs for a given grid scenario. The assessment of these criteria requires the development of a fault current estimation method for dc CB design purposes, which allows complex parameter variation analysis with limited computational effort for various fault scenarios in an MMC-based MTdc system. Mesh analysis with linear differential equations and modified average value model of the MMC is targeted to estimate the fault currents. In order to overcome the limitations of existing methods, the power flow in the converter during the fault time is included by considering the outer control loops. Moreover, it is analyzed how the fault current estimation can be extended to bipolar HVdc configuration, in which both pole-to-pole and pole-to-neutral faults can be investigated. Detailed parameter analysis is presented, which allows the evaluation of the suitability of recent dc circuit breaker designs for given grid and fault conditions. Additionally, adaptive auto-reclosing schemes are analyzed and the modular hybrid dc CB shall be exploited to inject active dc voltage pulses in the grid, in order to analyze the fault type by means of traveling wave analysis. In case of permanent faults, the same approach can be used to locate the fault position and in case of temporary faults, a smooth dc voltage build-up is presented by sequentially switching the dc CB main breaker modules off.

Target III: Analysis of the fault blocking capability of hybrid arm modular multilevel converter with reduced number of bipolar submodules

As the third research contribution, the fault blocking capability of MMC will be analyzed and an adapted topology of the hybrid arm MMC is targeted, which includes the minimum required number of bipolar SM, here the established full-bridge SM are chosen, to achieve acceptable fault clearing performance in terms of clearing time and SM over-voltage and reduced on-state losses. The minimum number of SM as well as the worst-case SM over-voltage will be derived analytically based on the fault operation sequence of the hybrid arm MMC.

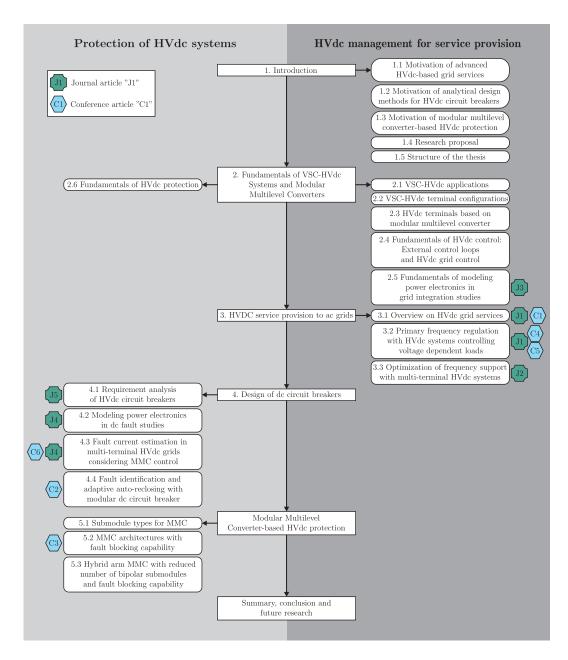

Fig. 1.4: Structure of the thesis and related publications.

### 1.5. Structure of this thesis

The topics investigated in this thesis are organized into six chapters as depicted in Fig. 1.4 along with their associated publications.

Section 2 provides the necessary theoretical basis for the presented work. HVdc system applications and configurations are explained, as well as the different possibilities to control and protect (multi-terminal) HVdc systems. Additionally, the fundamental operation of the MMC in HVdc terminals and its basic controller design is presented, which is used in the simulation models throughout this thesis. Moreover, a guideline to model power electronics in power system studies is presented, which deals with power system stability problems and is used to define the necessary deepness of modeling for the primary frequency regulation

method presented in **Section 3**.

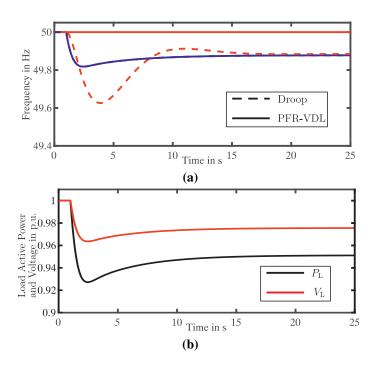

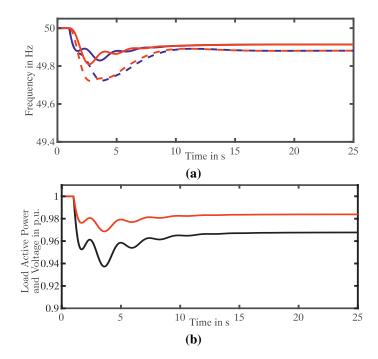

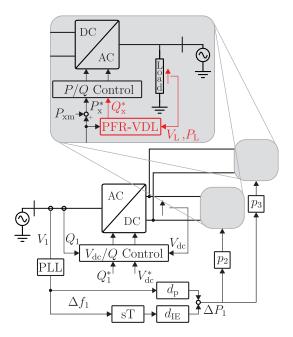

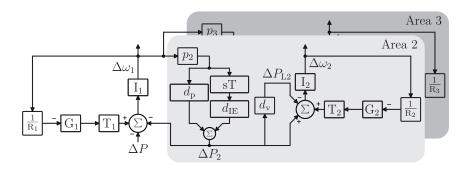

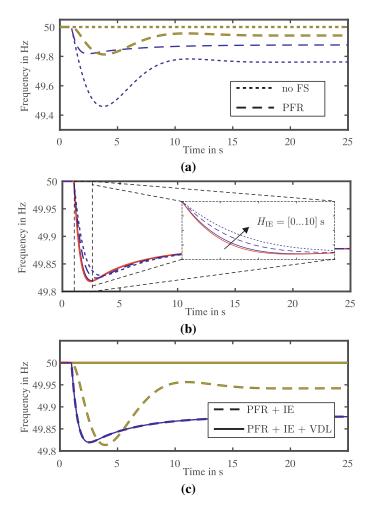

In Section 3, at first, an overview on HVdc grid services is given, which focuses on the control implementation and highlights the shortcomings of existing methodologies, especially referring to frequency regulation aspects. In the following, a HVdc-based primary frequency regulation method is presented, which is based on the control of voltage dependent loads and thus overcomes the limitation of undesired frequency disturbances in supporting areas, which are present in the state of the art methodologies, and is applicable not only to asynchronous but also to embedded HVdc systems, which is demonstrated analytically and proven with PSCAD/EMTDC simulations. Necessary fundamentals on load modeling and control as well as the power system representation for frequency control studies are given. Finally, a combination of primary frequency regulation and inertia emulation (referred to as enhanced frequency support) is proposed for MTdc systems, considering optimized share of the frequency support respecting the estimated load power to voltage sensitivity.

**Section 4** deals with design requirements of HVdc CB and analytical fault current estimation methods to evaluate those. It is proposed an analytical fault current estimation method based on coupled differential equations and mesh analysis, which accurately determines the current slope and maximum fault currents for pole-to-pole and pole-to-neutral faults in symmetrical monopole and bipolar HVdc configurations. The section is concluded by proposing an adaptive auto-reclosing strategy and fault type identification using the modular hybrid dc CB.

HVdc systems can be protected either by using dc CB as presented in **Section 4** or by employing fault blocking capability of the MMC in the HVdc terminals. A new perspective is put on the design of hybrid arm MMC, for which the minimum number of bipolar SM to achieve fault blocking capability with increased on-state efficiency is evaluated analytically from the converter's fault operation sequence in **Section 5**.

Finally, **Section 6** is dedicated to the summary of this thesis, followed by the conclusion and future research.

## 1.6. List of publications

The list of scientific papers associated with this thesis are given as follows:

### **Journal publications**

J1 M. Langwasser, G. De Carne, M. Liserre and M. Biskoping, "Primary Frequency Regulation Using HVDC Terminals Controlling Voltage Dependent Loads," in *IEEE*

- *Transactions on Power Delivery*, vol. 36, no. 2, pp. 710-720, April 2021, doi: 10.1109/TPWRD.2020.2990565.

- J2 M. Langwasser, G. De Carne, M. Liserre, and M. Biskoping, "Enhanced grid frequency support by means of hvdc-based load control," in *Electric Power Systems Research*, vol. 189, p. 106552, December 2020, doi: 10.1016/j.epsr.2020.106552.

- J3 G. De Carne, M. Langwasser, M. Ndreko, R. Bachmann, R.W. De Doncker, R. Dimitrovski, B.J. Mortimer, A. Neufeld, F. Rojas and M. Liserre, "Which Deepness Class Is Suited for Modeling Power Electronics?: A Guide for Choosing the Right Model for Grid-Integration Studies," in *IEEE Industrial Electronics Magazine*, vol. 13, no. 2, pp. 41-55, June 2019, doi: 10.1109/MIE.2019.2909799.

- J4 **M. Langwasser**, G. De Carne, M. Liserre and M. Biskoping, "Fault Current Estimation in Multi-Terminal HVdc Grids Considering MMC Control," in *IEEE Transactions on Power Systems*, vol. 34, no. 3, pp. 2179-2189, May 2019, doi: 10.1109/TP-WRS.2018.2887166.

- J5 M. Langwasser, G. D. Carne, M. Liserre, and M. Biskoping, "Requirement analysis of hybrid direct current breaker in multi-terminal high-voltage direct current grids," *Journal of Engineering*, vol. 2018, no. 15, pp. 1066-1071, October 2018, 10.1049/joe.2018.0267.

### **Conference publications**

- C1 **M. Langwasser**, K. Schoenleber, A. Wasserrab, M. Thiele, and M. Liserre, "Online estimation of dynamic capacity of vsc-hvdc systems: Power system use cases," *Internationaler ETG-Kongress* 2021, 2021.

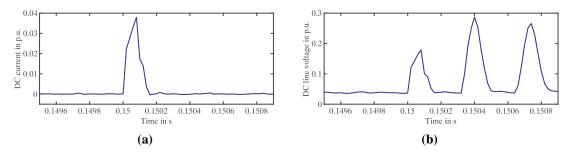

- C2 H. Iman-Eini, **M. Langwasser**, L. Camurca and M. Liserre, "Modular Hybrid DC Breaker-based Adaptive Auto-Reclosing Method for MMC-HVDC Systems," 2020 22nd European Conference on Power Electronics and Applications (EPE'20 ECCE Europe), 2020, pp. P.1-P.9, doi: 10.23919/EPE20ECCEEurope43536.2020.9215743.

- C3 **M. Langwasser**, H. Imaneini, G. De Carne and M. Liserre, "Estimation and Interruption of Short Circuit Currents in HVDC Systems," *2019 IEEE Power & Energy Society General Meeting (PESGM)*, 2019, pp. 1-5, doi: 10.1109/PESGM40551.2019.8973517.

- C4 **M. Langwasser**, M. Biskoping, G. D. Carne and M. Liserre, "Frequency support provision by parallel, hybrid HVDC-HVAC system with Voltage-based Load Control," *2019 IEEE Milan PowerTech*, 2019, pp. 1-6, doi: 10.1109/PTC.2019.8810519.

- C5 **M. Langwasser**, G. De Carne, M. Liserre and M. Biskoping, "Voltage-Based Load Control for Frequency Support Provision by HVDC Systems," *IECON 2018 44th Annual Conference of the IEEE Industrial Electronics Society*, 2018, pp. 311-316, doi: 10.1109/IECON.2018.8592709.

- C6 **M. Langwasser**, G. De Carne, M. Liserre and M. Biskoping, "Improved Fault Current Calculation Method for Pole-to-Pole Faults in MMC Multi-Terminal HVDC Grids Considering Control Dynamics," *2018 IEEE Energy Conversion Congress and Exposition (ECCE)*, 2018, pp. 5529-5535, doi: 10.1109/ECCE.2018.8557979.

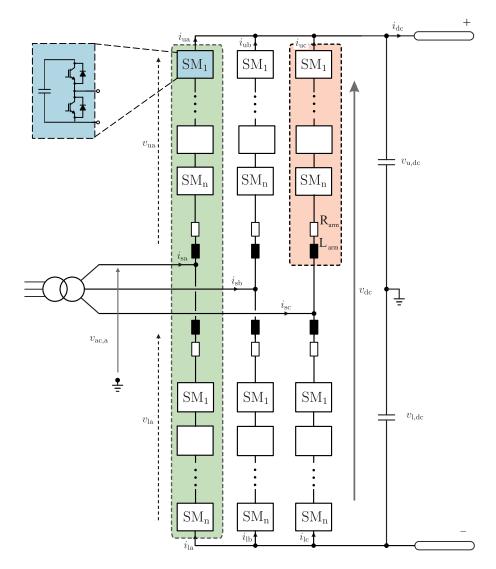

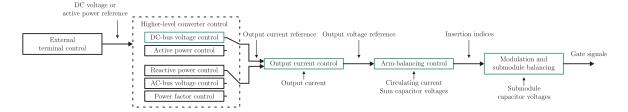

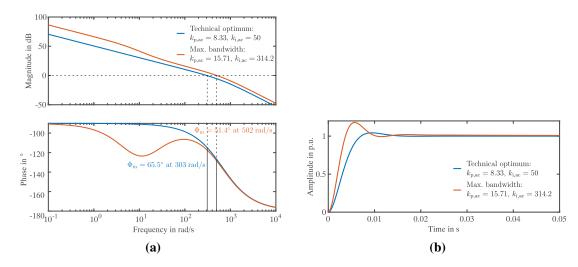

# 2. Fundamentals of VSC-HVdc systems and modular multilevel converters

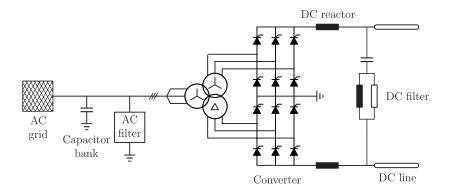

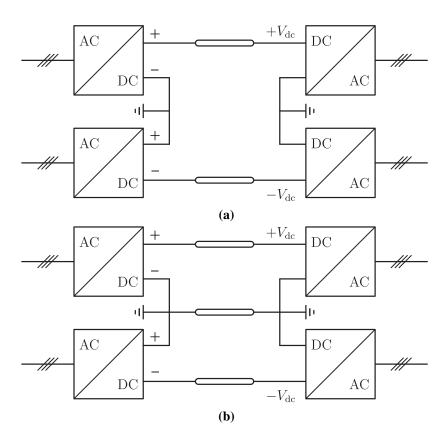

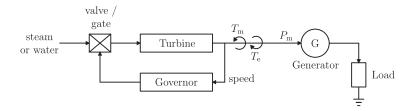

Modern HVdc systems can be classified in line-commutated converter HVdc (LCC-HVdc) using thyristor bridges in current source converter topology and voltage-source converter HVdc (VSC-HVdc) using forced-commutated power electronic switches such as high-voltage IGBTs [1]. A typical arrangement of a LCC-HVdc converter terminal using the 12-pulse thyristor bridge is shown in Fig. 2.1.

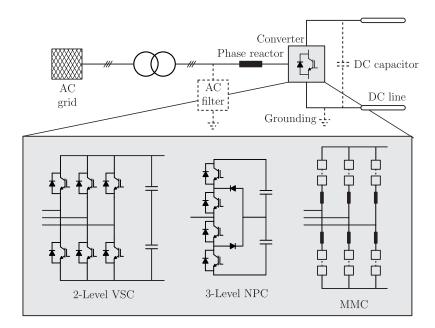

VSC-HVdc systems exist with three-different converter topologies (see terminal arrangement in Fig. 2.2). While the first commercial VSC-HVdc applications were built adopting two-level converters (like the Gotland HVdc project installed by ABB in 1997 [55]), also three-level neutral point clamped (NPC) converters are in use (MurrayLink Australia [4]). To date, most new VSC-HVdc installations are based on variants of the MMC. What differs among the manufacturers is the basic SM configuration. The technology of ABB, also known under the brand name HVdc Light, is based on series-connected insulated gate bipolar transistors (IGBT) in a double SM configuration, while Siemens and General Electric (formerly Alstom) use the MMC in its conventional structure without serialization in half-bridge (Siemens, known as HVdc Plus) and full-bridge (GE/Alstom, known as HVdc MaxSine) SM configuration [56, 4].

Table 2.1 summarizes the comparison between LCC- and VSC-HVdc systems.

As can be seen, VSC-HVdc systems present a number of advantages in comparison to their LCC counterpart [57], which are

- Independent active and reactive power control (no reactive power compensation is required)

- AC voltage support either in STATCOM mode or also while transmitting active power

**Fig. 2.1:** Typical arrangement of 12-pulse LCC-HVdc terminal (modified from [1]).

**Fig. 2.2:** Typical arrangement of VSC-HVdc terminal with 2-Level VSC, 3-Level NPC (single phase representation), and MMC.

- Fast active power reversal by reversing the current direction (dc voltage polarity is kept the same)

- Reduced filtering requirement and thus smaller footprint

- Service provision to the ac grid, such as black-start capability, low-voltage ride through (LVRT), fast frequency and damping support through power modulation

- Possibility to operate in grid-forming mode and thus enabling the transition from gridconnected to islanded operation

- Construction of multi-terminal grids because of constant voltage polarity and enhanced control functions

Nevertheless, both technologies will co-exist in the future, each with its specific application. The classic LCC-HVdc systems, due to their technological readiness, higher efficiency and lower operational costs will be applied at very higher power and voltage ratings, whereas the VSC-HVdc will be used in applications, in which the higher controllability and flexibility to provide services to the ac grid is of greater value [54].

The focus of this thesis, on one hand lies on the services HVdc systems can provide to the ac grid (which are only realizable with VSC-HVdc) and on the other hand on the protection using dc CB and MMC. That is why in the remainder of this section only the fundamentals of VSC-HVdc systems, their terminal configuration based on MMC, their control schemes, and protection are explained.

|                                | LCC-HVdc                                                                       | VSC-HVdc                                                          |

|--------------------------------|--------------------------------------------------------------------------------|-------------------------------------------------------------------|

| Power electronic               | Thyristor,                                                                     | IGBT,                                                             |

| technology                     | turn on capability only                                                        | turn on/turn off                                                  |

| Commercially established since | 1954                                                                           | 1997                                                              |

| Power rating                   | $\leq 10,000 \text{ MW}$                                                       | $\leq$ 4,500 MW                                                   |

| Voltage rating                 | $\pm 1,100~\mathrm{kV}$                                                        | $\pm 500~\mathrm{kV}$                                             |

| Filtering requirement          | High, due to low-order harmonics (e.g. 11 <sup>th</sup> and 13 <sup>th</sup> ) | Low (kHz-range)                                                   |

| Footprint                      | Very high (dominated by harmonic filters)                                      | Lower                                                             |

| Control                        | 2-quadrant operation (always consumes reactive power)                          | 4-quadrant operation (independent P/Q control)                    |

| AC network                     | strong ac network                                                              | Possibility to operate                                            |

| requirements                   | (SCR>3)                                                                        | with weak or islanded network                                     |

| AC faults                      | Commutation failure,<br>Loss of power transmission for<br>several hundred ms   | Fault ride through capability and maintains active power transfer |

| DC faults                      | Can extinguish dc faults by control action                                     | Depends on converter topology (fault blocking or feeding)         |

| Losses                         | 0.7%                                                                           | 2-Level: 1.5%, MMC: <1%                                           |

| Dynamic overload capability    | High                                                                           | Low                                                               |

| -                              | Difficult                                                                      | Easier                                                            |

| MTdc operation                 | (power flow reversal requires voltage polarity change)                         | (power flow reversal involves current polarity change)            |

**Table 2.1:** Comparison between LCC- and VSC-HVdc systems [56, 1].

## 2.1. VSC-HVdc applications

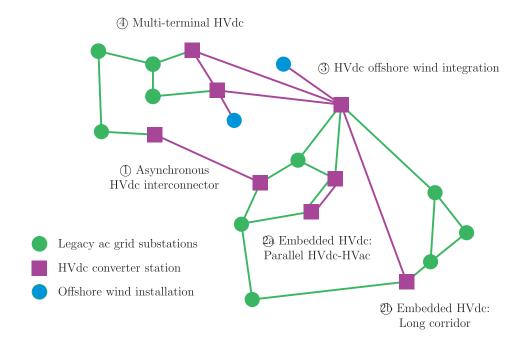

In the following section, the different existing VSC-HVdc applications are introduced to give a basis for the later study cases regarding HVdc protection and service provision to the ac grid. In the European network development plan [58], a threefold of HVdc systems, namely

- Asynchronous HVdc interconnector

- Embedded HVdc

- HVdc offshore wind integration

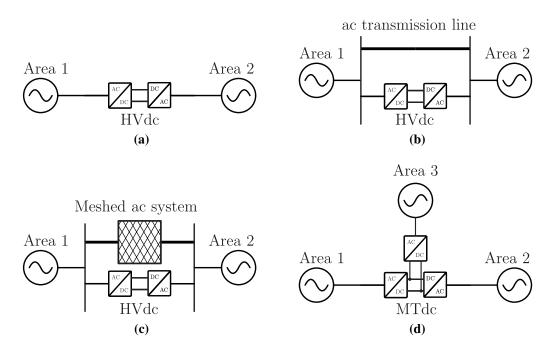

has been considered as possible solution towards a more controllable and reliable grid (see Fig. 2.3). MTdc grids, with respect to several point-to-point-connections, can dispatch the power flexibly among the terminals without limitations imposed by the ac power flow and thus are foreseen to become inevitable for the control and operation of the future power transmission system. Fig. 2.4 summarizes the schematic illustration of the different HVdc applications, while in the first case the ac areas can be either a meshed ac system or an

Fig. 2.3: HVdc applications in power system (modified from [5]).

isolated ac system (e.g. for offshore wind), the other cases always represent a meshed ac grid.

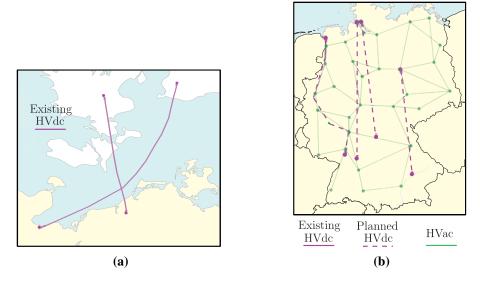

Asynchronous HVdc interconnector The most prominent application of HVdc to date are asynchronous HVdc interconnectors, which are used to transmit bulk power between two (strong) asynchronous ac grids. A practical example is given by the asynchronous HVdc interconnector between Germany and Denmark in Fig. 2.5(a). The flexibility, compactness and dynamic performance of VSC-HVdc makes it a favorable solution of transmission system operators worldwide to meet the growing challenges of network development [5]. Typical future applications are seen in megacities power infeed and the connection of remote islands [5].

**Embedded HVdc** The Joined CIGRE Working Group C4/B4/C1.604 [22] gives the following definition of an embedded HVdc system:

An embedded HVdc system is defined as a dc link with at least two ends being physically connected within a single synchronous ac network. With such a connection, it can perform not only the basic function of bulk power transmission, but also, importantly, some additional control functions within the ac network such as power flow control, voltage control, system stability improvement and the mitigation of system cascading failure.

#### In [5], three applications of embedded HVdc systems are defined:

The first case, embedded HVdc forming a hybrid parallel HVdc-HVac interconnection (schematic shown in Fig. 2.4(b)) is used to increase the transmission capacity of the combined corridor and to enhance the grid controllability with limited right of way for new infrastructure.

**Fig. 2.4:** Schematic illustration of HVdc applications: (a) Asynchronous HVdc interconnector (or HVdc offshore wind integration), (b) Embedded HVdc: Parallel, hybrid HVdc-HVac, (c) Embedded HVdc: Long HVdc corridor, (d) Multi-terminal HVdc.

An additional power transfer increase is achieved, since the HVdc can control the reactive power and ac voltage at both ends and thus allows the operation of the HVac line closer to its limits. Shorter HVdc lines in grids with higher degree of meshing and parallelism are better suited for reactive power based grid services, while active power-based support has only marginal influence due to the strong synchronous coupling between the two terminals [5].

The second case, schematically illustrated in Fig. 2.4(c), are long distance corridors to connect remote renewable energy generation or remote load centers within the same synchronous area. This scheme is best suited for bulk power transmission and active power related grid services, because it effectively reduces the power flow in any ac line, which residues between the two HVdc terminals [5]. A practical example of embedded HVdc is given by the planned HVdc corridors in Germany in Fig. 2.5(b).

The third case shows that embedded HVdc can be applied as back-to-back HVdc schemes to mesh grids and provide high power flow controllability. Thus, embedded back-to-back HVdc schemes can be seen as an alternative to phase shifting transformers or FACTS devices in an overall power flow management of an interconnected grid, particularly because of their independent active and reactive power controllability [22].

**HVdc offshore wind integration** In offshore wind application, a large amount of electric power aggregated from the wind turbines must be fed to the on-shore power system. The

**Fig. 2.5:** Examples of HVdc applications: (a) Asynchronous HVdc interconnector (Germany - Denmark), (b) Embedded HVdc links in Germany.

focus of this connection are cable systems (for submarine transmission and limited right of way on-shore), for which HVac suffers from the excessive reactive power drawn by the cable capacitances. Thus, the maximum length of HVac cables is restricted (usually to about 200 km for the typical 150 kV [59]). HVdc instead is suitable for bulk power transmission over long distances. Moreover, the HVdc decouples the offshore from the onshore grid, preventing cascading failures, and offers independent control of active and reactive power, which enables a variety of control objectives in both the offshore and onshore grid and allows a flexible configuration of the offshore wind farm grid irrespective of the wind turbine type [59]. In [60], a technical and economical analysis has proven the benefits of HVdc offshore wind integration with respect to its HVac counterpart.

Multi-terminal HVdc The development and construction of MTdc grids is mainly driven by the large-scale integration of renewable energy into the existing ac power system and the potential of international energy markets in the context of so-called supergrids [61]. Supergrids based on HVdc technology can form a new additional backbone for the power system [62]. One can distinguish two main types of MTdc: MTdc systems, which comprise of more than two terminals without dc meshes and real MTdc grids, which denote a dc transmission system based on more than two converters with at least one meshed dc path and hence providing multiple power-flow paths between two grid terminals [61]. MTdc systems will likely grow organically from existing HVdc links and offshore wind integration [61, 63].

A recent realization of MTdc is the Zhangbei HVdc power transmission project in China, which utilizes MMC at a rated voltage of  $\pm 500$  kV to form a ring network of four interconnected converter stations. The system is designed for a total transmitted power of 4.5 GW [64].

**Fig. 2.6:** Asymmetrical monopolar HVdc configurations: (a) with ground electrode return, (b) with metallic return conductor.

## 2.2. VSC-HVdc terminal configurations

To date, three main terminal configurations of VSC-HVdc systems are installed, which are asymmetrical monopole, symmetrical monopole and bipolar configurations [4].

#### 2.2.1. Asymmetrical monopole configuration

The asymmetrical monopole configuration for a point-to-point HVdc link is shown in Fig. 2.6. This scheme consists of one high voltage conductor (cable or overhead line) and eventually one neutral conductor. In normal operation, the current flows through the high voltage conductor. The return path is formed by either the ground or sea electrodes (Fig. 2.6(a)) if substantial ground currents are allowed and the HVdc link is grounded at both terminals or the metallic ground conductor (Fig. 2.6(a)), which is usually grounded at a single end [4].

In most cases, the ground return currents are not allowed due to environmental concerns. The neutral conductor avoids the ground currents, however, involves higher losses compared to the ground return configuration. The neutral conductor must be rated for the full current, but can have - especially for submarine installations - lighter insulation, since it does not require to withstand the full dc voltage, but only the voltage drop along the conductor and the temporary over-voltage in case of failure. Thus, the costs and also the probability of dielectric failures are lower as compared to the high voltage conductor. In overhead transmission line systems, a possibility to reduce the corona-effects, is to choose the high voltage conductor with negative polarity [4].

Two major drawbacks are present in asymmetrical monopole HVdc configuration. On one hand, the dc side of the HVdc link is grounded (dc voltage is asymmetric) and therefore the ac side transformer must withstand continuous dc stress of half the rated dc voltage and special transformer designs have to be applied. On the other hand, in case of failure (e.g.

Fig. 2.7: Symmetrical monopole HVdc configuration

short circuit or component outage) or maintenance, the whole HVdc system must be shut down and the power transfer is completely disrupted [4].

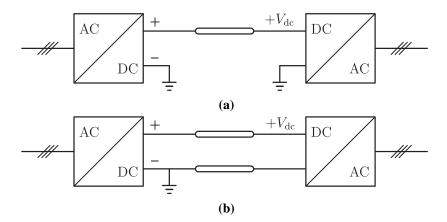

#### 2.2.2. Symmetrical monopole configuration

Fig. 2.7 shows the symmetrical monopole configuration of a point-to-point HVdc system, which is the commonly used configuration for VSC-HVdc systems nowadays. The two dc terminals of the converters are connected to the positive and negative pole. The dc voltage potential of both poles is equal, i.e.  $\frac{V_{\rm dc}}{2}$ , but with opposite polarity. So, in contrast to the asymmetrical monopole configuration, the dc voltage is symmetrical in this case and no steady-state dc voltage stress is applied on the ac transformers and standard transformer design can be used. Various grounding options (e.g. high impedance grounding) can be used to ground the system on the dc side at the midpoint of the shunt capacitors. The grounding configuration has large impact on the fault currents in case of pole-to-ground faults [4].

Even though the two high voltage conductors are rated at full current and isolated to the full dc voltage, in case of failure, similar to the asymmetrical monopole, the system cannot remain in operation by using the earth as return path. The critical drawback, is that in case of pole-to-ground faults, the healthy pole voltage can - in theory - raise to a maximum voltage of 2 times the pre-fault voltage. To be noted that the pole-to-pole voltage will stay constant at  $V_{\rm dc}$  but with a displacement between the poles. To avoid the heavy over-voltage and potential insulation breakdown in the healthy pole, the whole system must be shut down in case of fault, resulting in complete loss of power transfer [4].

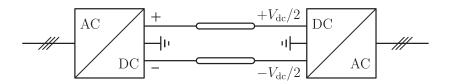

#### 2.2.3. Bipolar configuration

In Fig. 2.8, the two possibilities of bipolar HVdc point-to-point configuration are depicted, with ground electrode return (Fig. 2.8(a)) or with metallic return conductor (Fig. 2.8(b)). In general, the bipolar structure is the connection of two asymmetrical monopoles sharing the same ground pole, which is the midpoint of the two converters. On the ac side, each converter is connected to a separate transformer and thus the two converters are operated in parallel from the ac grid perspective. Similar to the asymmetrical monopole configuration, the two transformers will experience steady-state dc stress and hence special transformer designs are required [4].

**Fig. 2.8:** Bipolar HVdc configurations: (a) with ground electrode return, (b) with metallic return conductor.

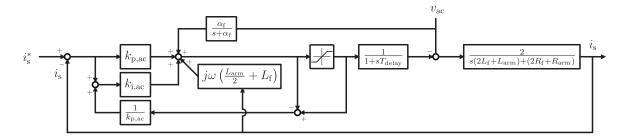

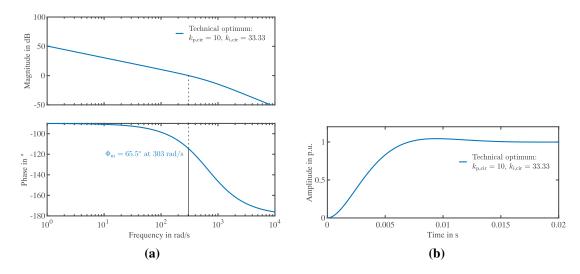

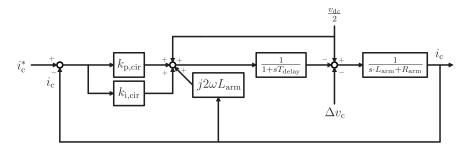

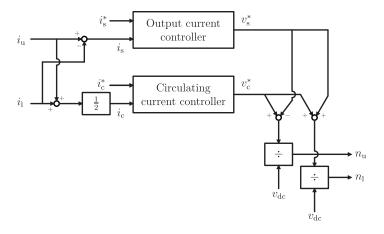

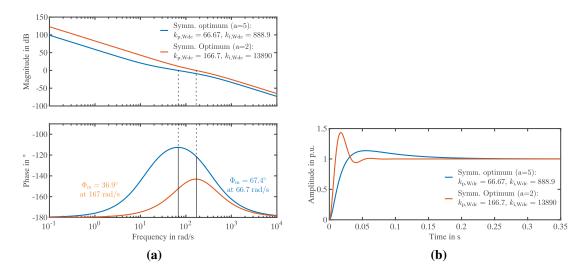

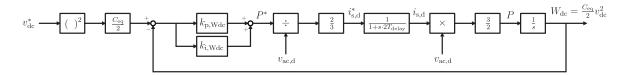

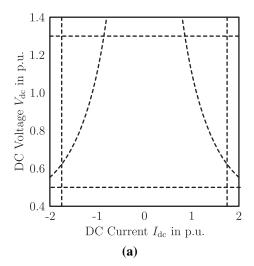

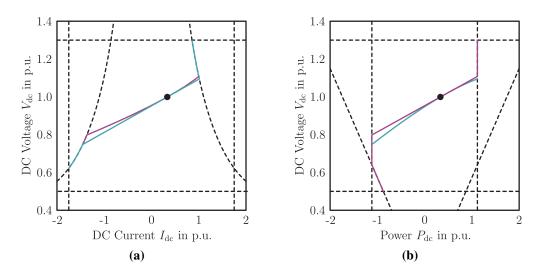

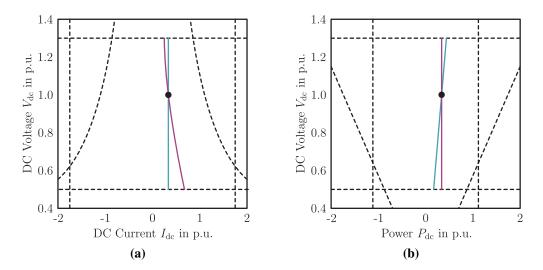

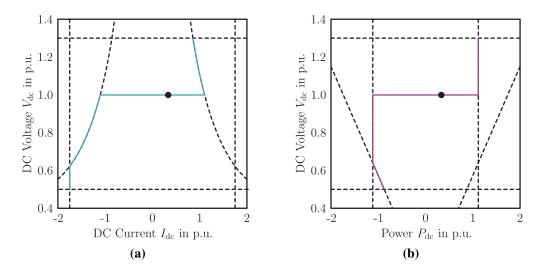

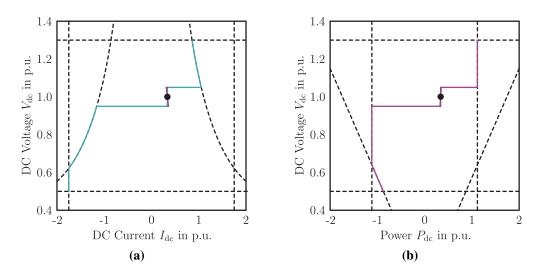

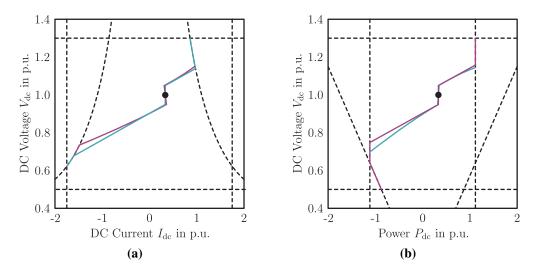

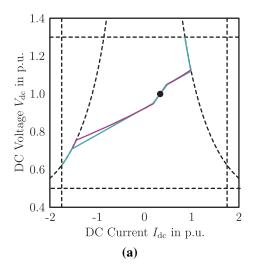

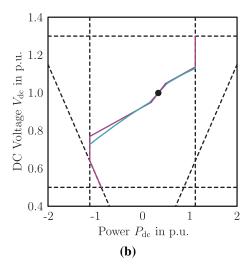

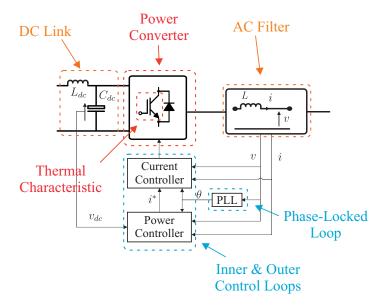

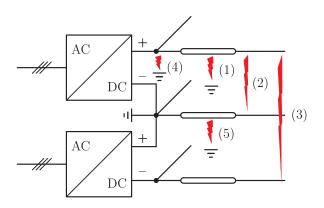

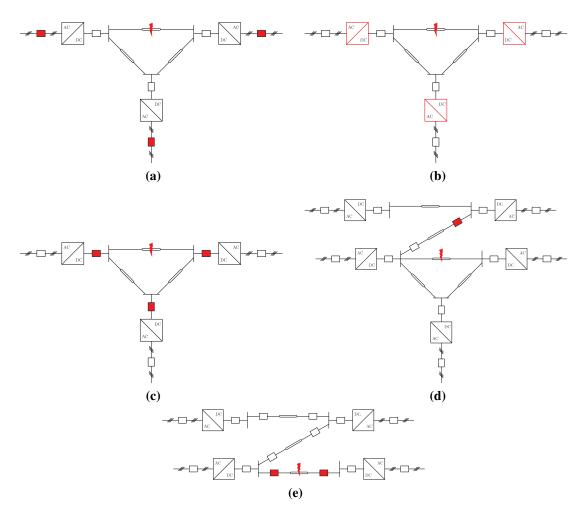

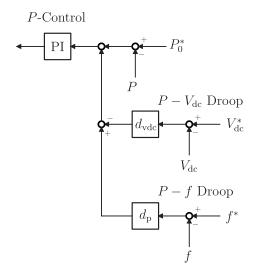

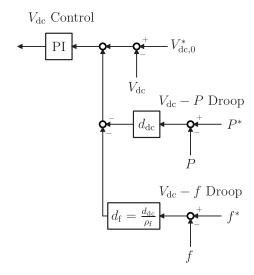

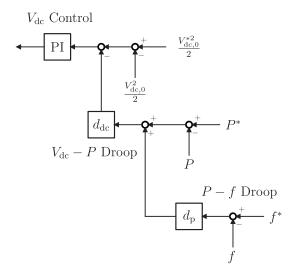

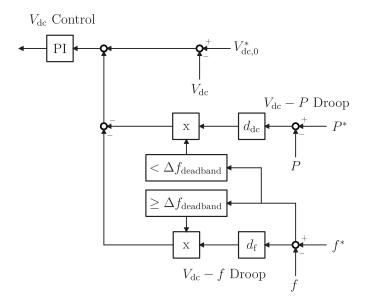

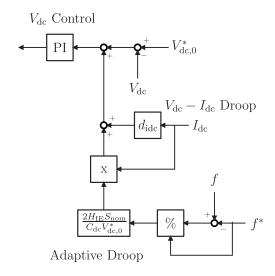

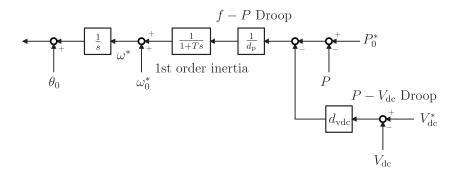

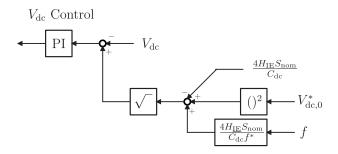

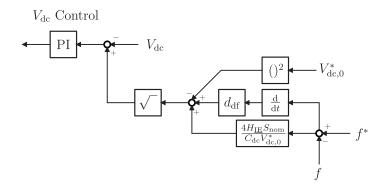

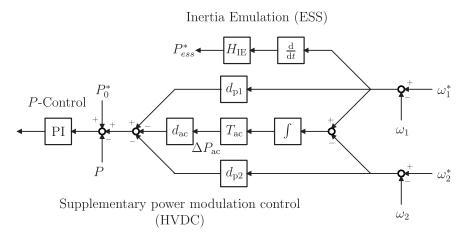

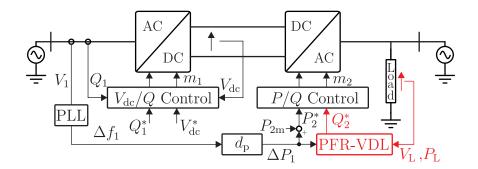

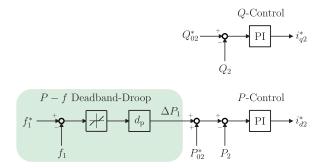

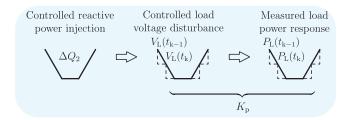

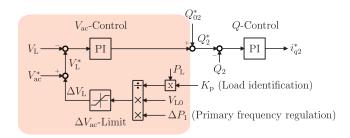

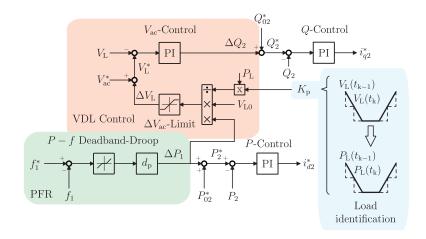

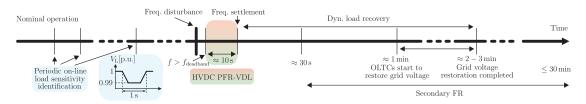

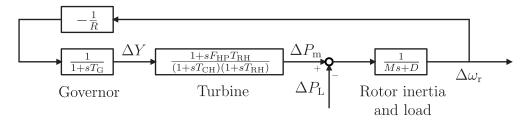

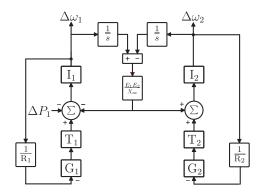

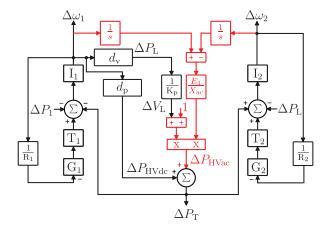

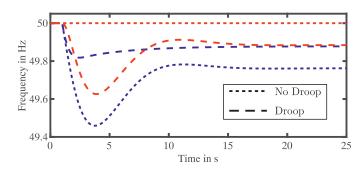

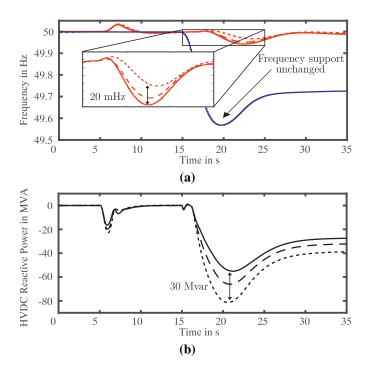

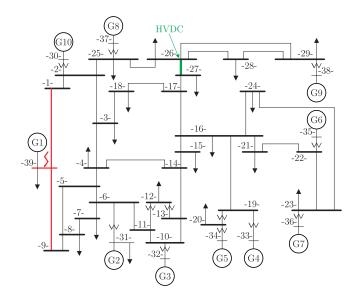

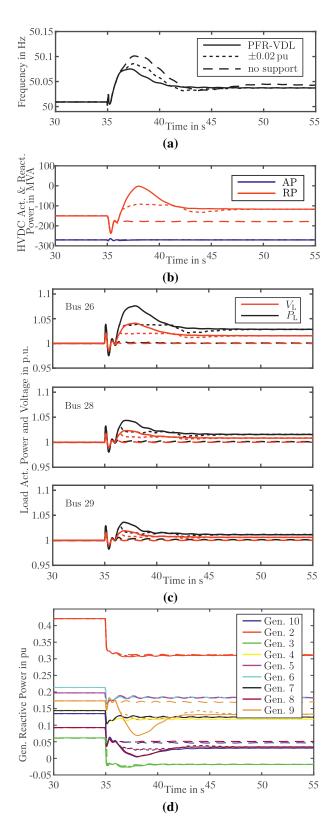

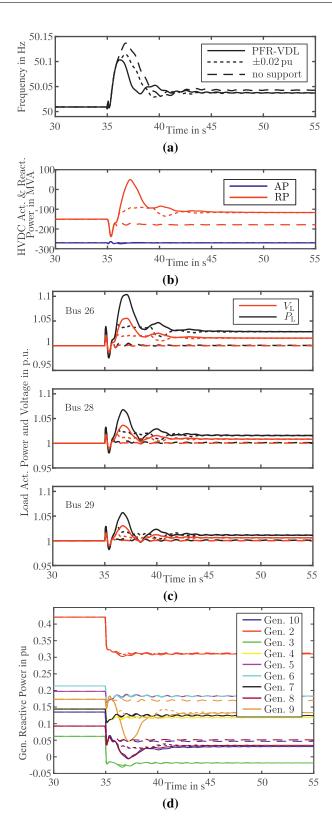

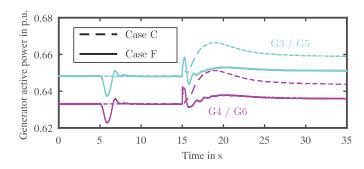

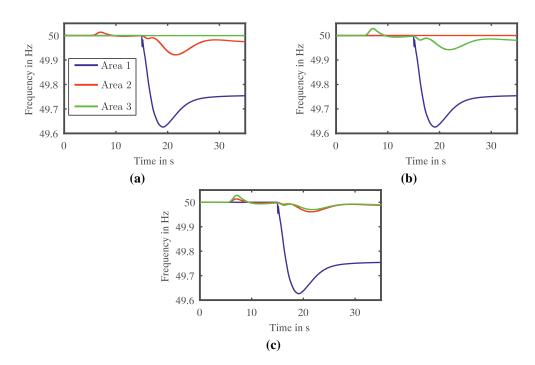

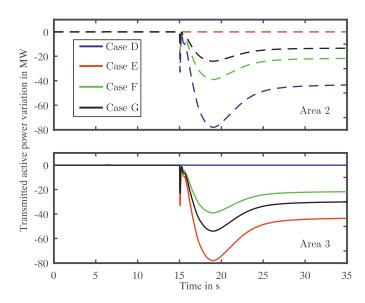

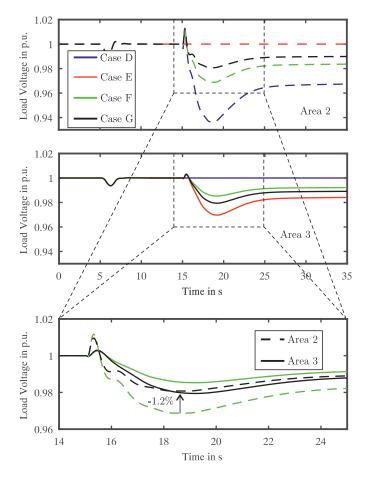

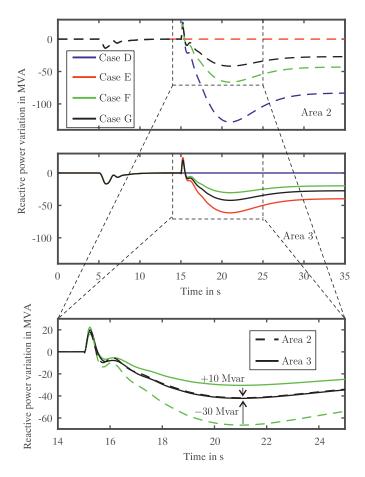

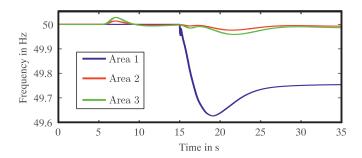

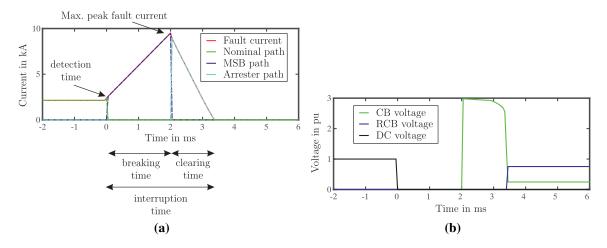

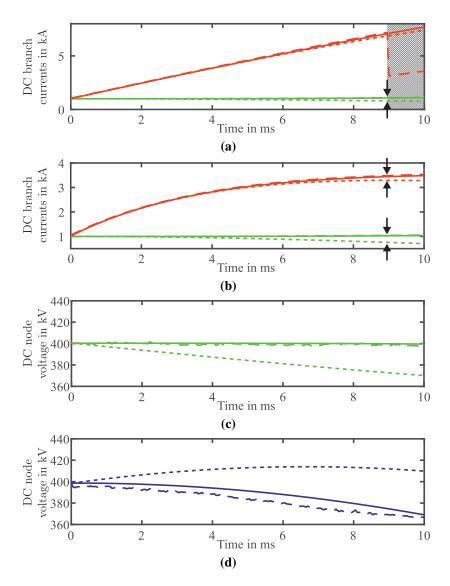

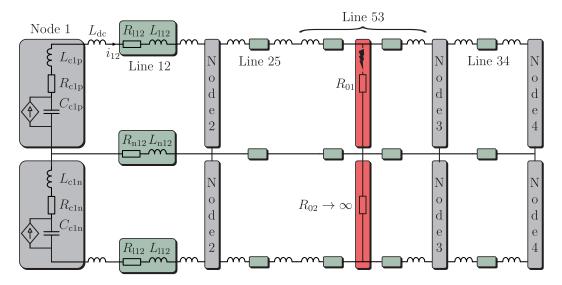

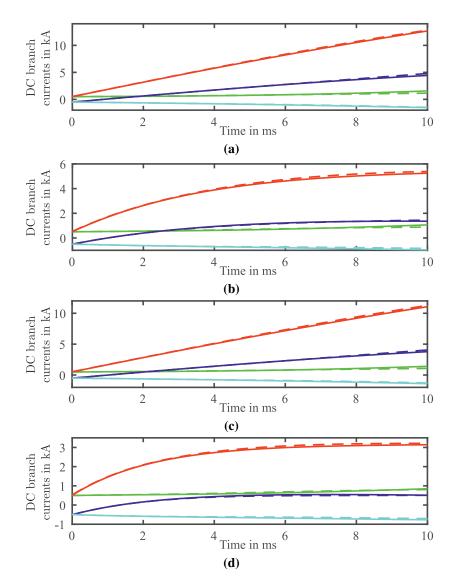

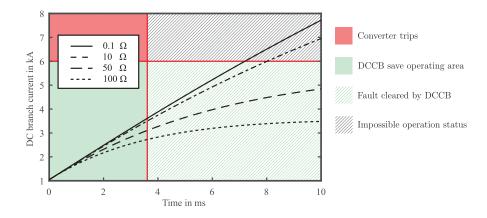

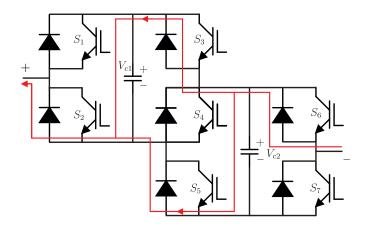

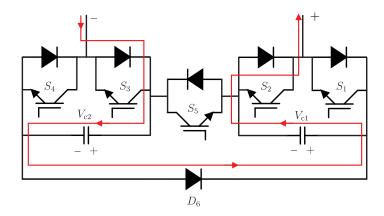

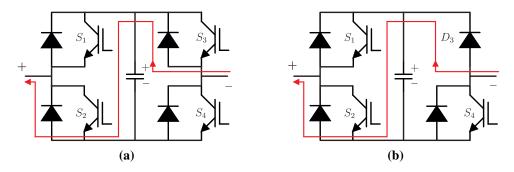

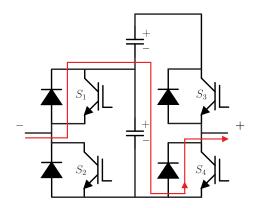

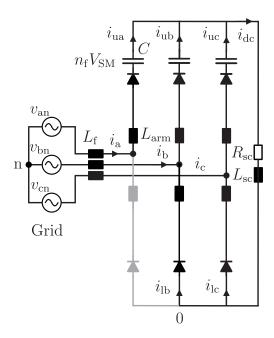

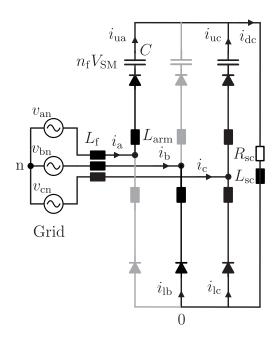

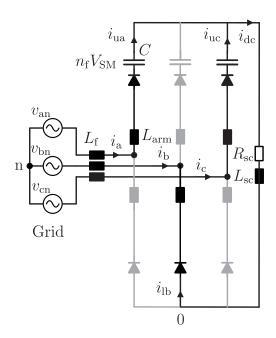

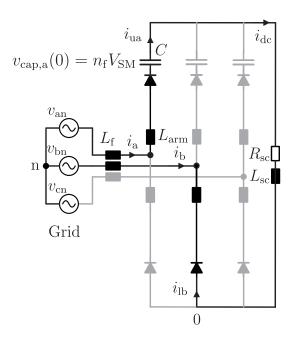

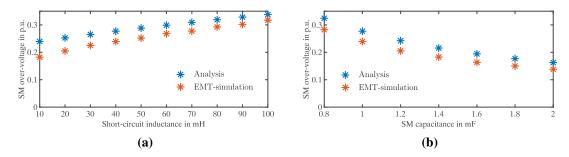

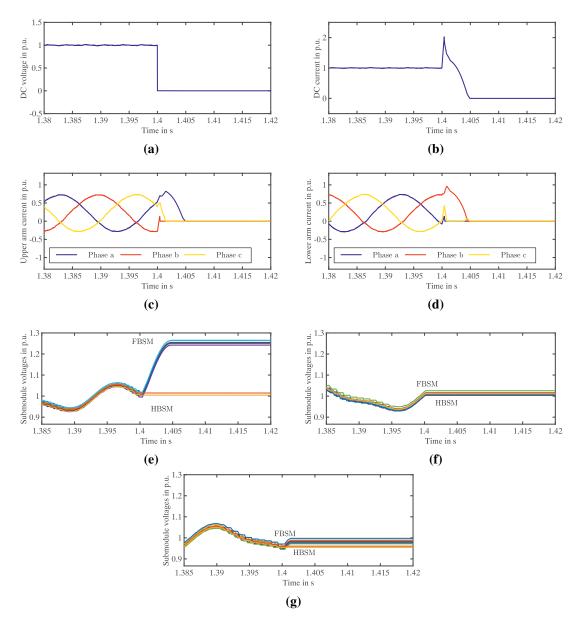

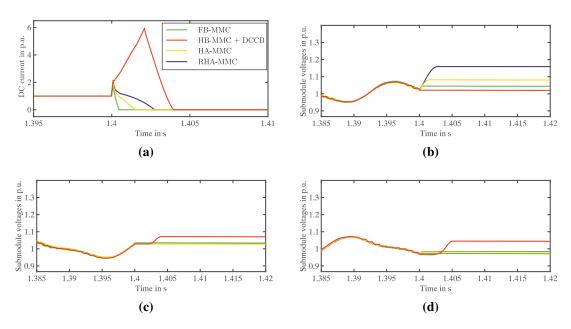

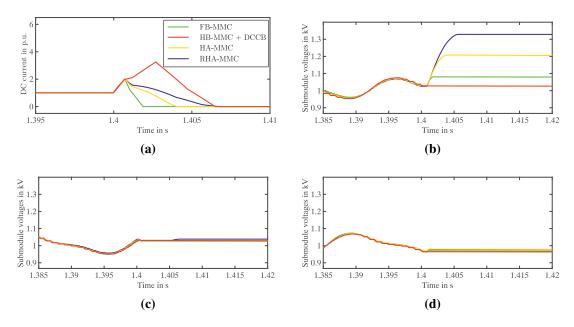

The bipolar HVdc configuration uses two high voltage conductors with equal dc voltage rating of  $V_{\rm dc}$  of opposite polarity. One converter is connected to the positive pole, while the other is connected to the negative pole. In normal operation, the two poles are balanced and the current is circulating among them. The pole currents have equal amplitude, but opposite flow direction, e.g. by convention forward in the positive pole and backward in the negative pole (return path). Hence, in normal operation, no current is flowing through the neutral conductor or the ground electrodes. This configuration is also referred as rigid bipolar. As shown in (Fig. 2.8(b)), a metallic neutral conductor can be used to connect the two ground poles (of rectifier and inverter end of the HVdc link) in order to avoid substantial ground currents. This can be either necessary due to environmental reasons or also to avoid degradation of the ground electrodes, which occurs for long term use of the ground path in conduction state [4].