# INSTITUT FÜR INFORMATIK UND PRAKTISCHE MATHEMATIK

# **KEP2 (Kiel Esterel Processor 2) THE ESTEREL PROCESSOR**

Xin Li, Reinhard von Hanxleden

Bericht Nr. 0506 June 2005, Revised August 17, 2005

# CHRISTIAN-ALBRECHTS-UNIVERSITÄT KIEL

# Institut für Informatik und Praktische Mathematik der Christian-Albrechts-Universität zu Kiel Olshausenstr. 40 D – 24098 Kiel

# **KEP2 (Kiel Esterel Processor 2) THE ESTEREL PROCESSOR**

Xin Li, Reinhard von Hanxleden

Bericht Nr. 0506 June 2005, Revised August 17, 2005

e-mail: xli@informatik.uni-kiel.de, rvh@informatik.uni-kiel.de

#### Abstract

The concurrent synchronous language Esterel allows to program reactive systems in an abstract, concise manner. Several preemption operators, such as suspension or weak and strong abortion, are provided to directly express reactive behavior with a deterministic, mathematically precise semantics, without the inherent need for the support of a resource-consuming, typically non-deterministic operating system.

An Esterel program is typically first translated into other, non-synchronous high-level languages, such as VHDL or C, and then compiled further into hardware or software. Another approach that has been proposed recently is the *direct execution* of Esterel-like instructions with a customized processor, which promises the flexibility of a software solution with an efficiency close to a hardware implementation. However, the instruction sets and implementations of the processor architectures proposed so far still have some limitations regarding their completeness, efficiency, and adherence to the original Esterel semantics. This paper presents a novel processor architecture, the Kiel Esterel Processor, which addresses these shortcomings. In particular, it provides a complete, semantically accurate implementation of the Esterel preemption primitives, most of which can be expressed directly with a single machine instruction.

# Contents

| 1            | Intr                                    | roduction                             | 6               |  |  |  |  |  |  |  |  |  |  |

|--------------|-----------------------------------------|---------------------------------------|-----------------|--|--|--|--|--|--|--|--|--|--|

| 2            | Rela                                    | ated Work                             | 8               |  |  |  |  |  |  |  |  |  |  |

| 3            | The Kiel Esterel Processor Architecture |                                       |                 |  |  |  |  |  |  |  |  |  |  |

|              | 3.1                                     | The KEP2 Input/Output Interface       | 9               |  |  |  |  |  |  |  |  |  |  |

|              | 3.2                                     | The KEP Tick Manage                   | 14              |  |  |  |  |  |  |  |  |  |  |

|              | 3.3                                     | The Reactive Core                     | 14              |  |  |  |  |  |  |  |  |  |  |

|              | 0.0                                     | 3.3.1 The Preemption Element          | 15              |  |  |  |  |  |  |  |  |  |  |

|              |                                         | 3.3.2 The AWAIT Element               | 18              |  |  |  |  |  |  |  |  |  |  |

|              |                                         | 3.3.3 The CAWAIT Element              | 18              |  |  |  |  |  |  |  |  |  |  |

|              |                                         | 3.3.4 The PRESENT Element             | 18              |  |  |  |  |  |  |  |  |  |  |

|              | 9.4                                     |                                       |                 |  |  |  |  |  |  |  |  |  |  |

|              | 3.4                                     | The Interface Block                   | 20              |  |  |  |  |  |  |  |  |  |  |

|              | 3.5                                     | Local Signals                         | 23              |  |  |  |  |  |  |  |  |  |  |

| 4            | Exp                                     | perimental Results                    | <b>24</b>       |  |  |  |  |  |  |  |  |  |  |

| 5            | Han                                     | adling Concurrency                    | <b>26</b>       |  |  |  |  |  |  |  |  |  |  |

| 6            | Con                                     | clusion and Outlook                   | 26              |  |  |  |  |  |  |  |  |  |  |

| $\mathbf{A}$ | The                                     | Instruction Set Architecture          | 28              |  |  |  |  |  |  |  |  |  |  |

|              | A.1                                     | Preemption (abort/weak abort/suspend) | 28              |  |  |  |  |  |  |  |  |  |  |

|              |                                         | A.1.1 ABORT                           | 28              |  |  |  |  |  |  |  |  |  |  |

|              |                                         | A.1.2 WABORT                          | 28              |  |  |  |  |  |  |  |  |  |  |

|              |                                         | A.1.3 SUSPEND                         | 29              |  |  |  |  |  |  |  |  |  |  |

|              | A.2                                     | Signal awaiting (await, pause)        | 30              |  |  |  |  |  |  |  |  |  |  |

|              |                                         | A.2.1 AWAIT                           | 30              |  |  |  |  |  |  |  |  |  |  |

|              |                                         | A.2.2 PAUSE                           | 30              |  |  |  |  |  |  |  |  |  |  |

|              | A 3                                     | Multiple signal awaiting (await case) | 31              |  |  |  |  |  |  |  |  |  |  |

|              | 11.0                                    | A.3.1 CAWAIT                          | 31              |  |  |  |  |  |  |  |  |  |  |

|              |                                         | A.3.2 CAWAITE                         | 31              |  |  |  |  |  |  |  |  |  |  |

|              | A.4                                     | Signal emission (emit)                | 32              |  |  |  |  |  |  |  |  |  |  |

|              | 11.1                                    | A.4.1 EMIT                            | $\frac{32}{32}$ |  |  |  |  |  |  |  |  |  |  |

|              |                                         | A.4.2 EMITR                           | $\frac{32}{32}$ |  |  |  |  |  |  |  |  |  |  |

|              | A.5                                     | Sustaining signals (sustain)          | $\frac{32}{33}$ |  |  |  |  |  |  |  |  |  |  |

|              | А.5                                     | A.5.1 SUSTAIN                         | 33              |  |  |  |  |  |  |  |  |  |  |

|              |                                         | A.5.2 SUSTAINR                        | აა<br>33        |  |  |  |  |  |  |  |  |  |  |

|              | 1 C                                     |                                       |                 |  |  |  |  |  |  |  |  |  |  |

|              | A.6                                     | The halt statement                    | 34              |  |  |  |  |  |  |  |  |  |  |

|              | A 77                                    | A.6.1 HALT                            | 34              |  |  |  |  |  |  |  |  |  |  |

|              | A.7                                     | The nothing statement                 | 34              |  |  |  |  |  |  |  |  |  |  |

|              | 4 0                                     | A.7.1 NOTHING                         | 34              |  |  |  |  |  |  |  |  |  |  |

|              | A.8                                     | Testing signal presence (present)     | $\frac{34}{34}$ |  |  |  |  |  |  |  |  |  |  |

|              | A.9                                     | Signal scoping (signal)               | 35              |  |  |  |  |  |  |  |  |  |  |

|              | 11.0                                    | A.9.1 SIGNAL                          | 35              |  |  |  |  |  |  |  |  |  |  |

|              | Δ 10                                    | Arithmetic and logical operations     | 35              |  |  |  |  |  |  |  |  |  |  |

|              | A.10                                    | A.10.1 CLRC                           | 35              |  |  |  |  |  |  |  |  |  |  |

|              |                                         | A.10.1 CERC                           | - 36            |  |  |  |  |  |  |  |  |  |  |

|              |                                         |                                       |                 |  |  |  |  |  |  |  |  |  |  |

|              |                                         | A.10.3 SR                             | 36              |  |  |  |  |  |  |  |  |  |  |

|              | A.10.4 SRC                            | 37        |

|--------------|---------------------------------------|-----------|

|              | A.10.5 NOTR                           | 37        |

|              | A.10.6 LOAD                           | 37        |

|              | A.10.7 ADD                            | 39        |

|              | A.10.8 ADDC                           | 40        |

|              | A.10.9 SUB                            | 41        |

|              | A.10.10SUBC                           | 43        |

|              | A.10.11MUL                            | 44        |

|              | A.10.12ANDR                           | 46        |

|              | A.10.13ORR                            | 47        |

|              | A.10.14XORR                           | 49        |

|              | A.10.15CMP                            | 50        |

|              | A.11 The conditional branch statement | 52        |

|              | A.11.1 JW                             | 52        |

|              | A.12 Others                           | 54        |

|              | A.12.1 GOTO                           | 54        |

|              | A.12.2 CALL                           | 55        |

|              | A.12.3 RET                            | 55        |

| В            | Synthesizing a KEP Configuration      | 56        |

|              | B.1 Reactive Block Generator          | 56        |

|              | B.2 Interface Block Generator         | 56        |

|              | B.3 Datapath Block Generator          | 57        |

|              | B.4 Innerconnection Generator         | 57        |

| $\mathbf{C}$ | KEP2 Assembler Compiler               | <b>58</b> |

# List of Figures

| 1   | An Esterel code fragment involving a weak abort statement (a), and the corresponding assembler code for RePIC (b) and KEP (c) |

|-----|-------------------------------------------------------------------------------------------------------------------------------|

| 2   | SPEED: an example module including valued signals and variables                                                               |

| 3   | Translation rules of every and loop statements                                                                                |

| 4   | The interface connections (a), and the waveform of the Tick signal (b)                                                        |

| 5   | The architecture overview                                                                                                     |

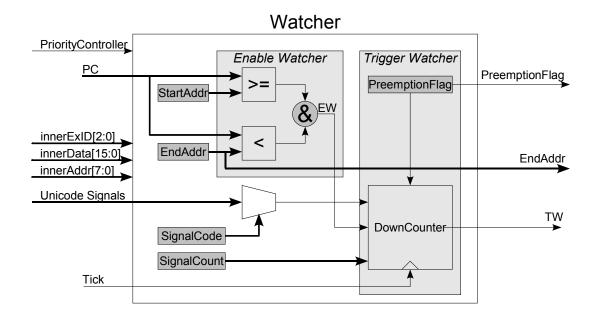

| 6   | The structure of the Watcher                                                                                                  |

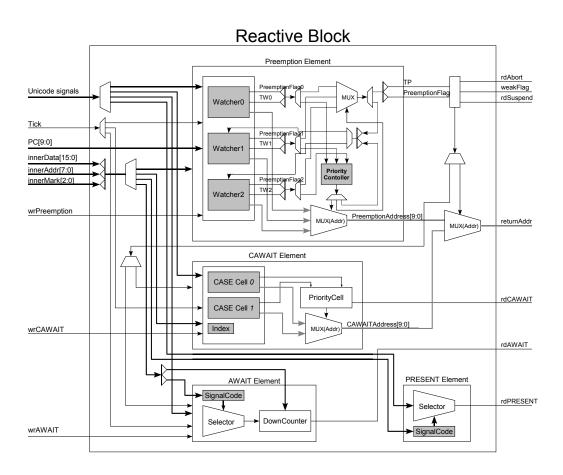

| 7   | Architecture of a Reactive Block with three Watchers                                                                          |

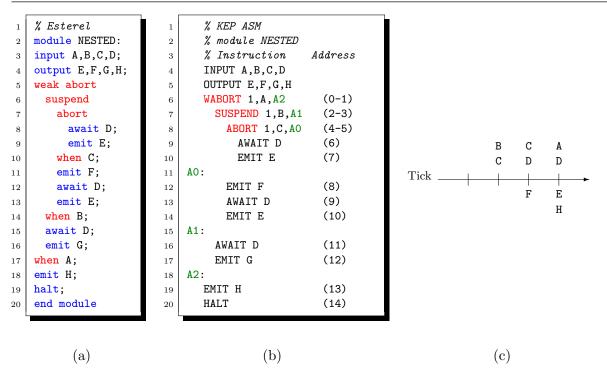

| 8   | NESTED: the Esterel module illustrating the preemption statements (a), the KEP                                                |

| O   | assembler program (b), and an execution trace (c)                                                                             |

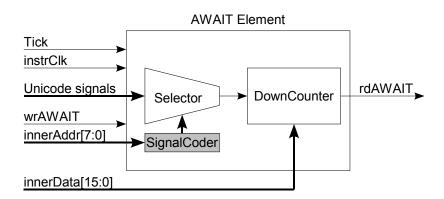

| 0   | Architecture of the AWAIT Element.                                                                                            |

| 9   |                                                                                                                               |

| 10  | Architecture of a CAWAIT Element, with 3 CASE Cells                                                                           |

| 11  | Architecture of the PRESENT Element                                                                                           |

| 12  | The architecture of an Interface Block                                                                                        |

| 13  | INOUT: an Esterel module illustrating the processes of I/O statements (a), and                                                |

| 1.4 | the compiled KEP assembler program                                                                                            |

| 14  | REINC: Translation of the Esterel signal declaration (a) into to the KEP SIGNAL                                               |

|     | instruction (b)                                                                                                               |

| 15  | Translating the Esterel abort/weak abort/suspend statements to the KEP2 in-                                                   |

|     | structions                                                                                                                    |

| 16  | Translating the Esterel await/pause statements to the KEP2 AWAIT/PAUSE in-                                                    |

|     | structions                                                                                                                    |

| 17  | Translating the Esterel await case statements to the KEP2 CAWAIT/CAWAITE                                                      |

|     | instructions                                                                                                                  |

| 18  | Translating the Esterel emit statements to the KEP2 EMIT/EMITR instructions 33                                                |

| 19  | Translating the Esterel sustain statements to the KEP2 SUSTAIN/SUSTAINR in-                                                   |

|     | structions                                                                                                                    |

| 20  | Translating the Esterel present statement to the KEP2 PRESENT instruction 35                                                  |

| 21  | Translating the Esterel signal statements to the KEP2 SIGNAL instructions 36                                                  |

| 22  | Translating the Esterel arithmetic statements to the KEP2 instructions 52                                                     |

| 23  | Translating the Esterel branch statements to the KEP2 branch instructions 54                                                  |

| 24  | The program of the example RUNNER in Esterel (a) and KEP assembler (b) 59                                                     |

| 25  | The speed optimization of the example RUNNER                                                                                  |

| 26  | The tradeoff optimization of the example RUNNER 61                                                                            |

# List of Tables

| 1 | Comparison of implementation alternatives                                       | 7  |

|---|---------------------------------------------------------------------------------|----|

| 2 | Overview of the instruction set architecture (part $1/2$ )                      | 10 |

| 3 | Overview of the instruction set architecture (part $2/2$ )                      | 11 |

| 4 | KEP2 Interface Signals Descriptions                                             | 13 |

| 5 | The signal codes of the INOUT module (a), and the break down of the instruction |    |

|   | encoding of the EMIT G,#25 instruction (hexadecimal 0x38200019) with indica-    |    |

|   | tions for the half bytes (b)                                                    | 20 |

| 6 | The codes size and RAM usage (in word) comparison of CURVE implementation       |    |

|   | between KEP2, MCS51, and Microblaze                                             | 24 |

| 7 | Comparison of the codes sizes, in words                                         | 25 |

| 8 | The RAM usage (in words/bytes) comparison of module implementations. One        |    |

|   | KEP word equals two bytes, and one Microblaze word equals four bytes            | 25 |

| 9 | Performance comparison between the KEP2 series and RePIC                        | 25 |

# 1 Introduction

The synchronous language Esterel has been developed for modeling reactive systems [4]. As a system-level language, it gives an abstract, well-defined and executable description of the application, and can be synthesized into other high-level languages for further compilation.

A fundamental concept of Esterel is the *signal*; signals are used to communicate internally and with the environment. The execution of an Esterel program is divided into logical *instants*, or *ticks*, which also determine the sampling of input signals and the generation of output signals. The synchrony of Esterel implies that the outputs generated from given inputs occur at the same logical instant; that is, the generation of outputs is (conceptually) simultaneous with the inputs, and computations are (conceptually) instantaneous. Signals are *present* or *absent* throughout an instant, indicating the occurrence of certain events, and they may also carry a value.

As a system level language for programming control-dominated reactive systems, Esterel's control flow primitives are much richer than that of traditional, sequential programming languages. In particular, Esterel allows to express various types of preemption, including abortion and suspension [3]. An abortion statement kills its *abort body* upon a specific trigger signal. In strong abortion, expressed by abort, the body does not receive control at the instant when the trigger occurs. For weak abortion, performed by weak abort, the body receives the control for a last time at the abortion time. A suspension, performed by suspend, freezes the state of a body for the instant when the trigger event occurs.

There are several methods to implement an Esterel program:

- A hardware implementation [2] has small memory requirements and low unit production costs. However, it is not flexible, and its resource usage increases rapidly when data path handling is needed.

- A software implementation [4, 8] on the other hand is a very flexible solution, and has low costs for the data path and arithmetic operations. However, common (COTS) processor architectures cannot handle reactive control constructs directly; therefore, handling these control constructs correctly turns out to be fairly expensive on classical software implementations. Moreover, the instruction and data memory requirements can be prohibitive for small, low-cost micro controllers.

- The co-design approach [1] partitions a model into hardware and software parts, trying to achieve a good balance of flexibility, performance and cost; for the software part, again a traditional μC is used.

Another approach to combine the advantages of custom hardware and traditional software is to implement an Esterel program on a *reactive processor* whose instruction set has been tailored to Esterel. We distinguish two variants of this approach.

- The patched reactive processor implementation combines a COTS processor core with an external hardware block, which implements additional Esterel-style instructions.

- A custom reactive processor implementation consists of a full-custom reactive core, whose instruction set and data path have been tailored exclusively for the processing of Esterel code.

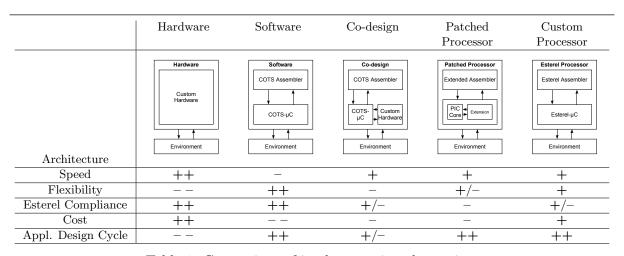

Table 1 provides a high-level comparison of these implementation alternatives.

So far, there have been only limited and fairly recent investigations of the reactive processor approach. To our knowledge, the ReFLIX and RePIC architectures proposed by Dayaratne, Roop, Salcic *et al.* [11, 12, 7] are the only ones that fall into this category, and they both follow the patched processor strategy. Their results are fairly promising, illustrating the potential of

Table 1: Comparison of implementation alternatives ++ represents best; -- means worst, e. g., Cost ++ means very low production costs.

this approach. However, there are also certain limitations of the architectures proposed so far, for example regarding their support of the Esterel preemption primitives, as discussed further in the following section.

In this paper, we present an alternative architecture, the *Kiel Esterel Processor* (*KEP*), which is a custom reactive processor, to our knowledge the first of this kind. The architecture presented in this paper is version 2.0 of the Kiel Esterel Processor, hence we also refer to it as KEP2. Notable features of the KEP2 include the following:

- 1. It gives a complete, semantically accurate implementation of the Esterel preemption primitives, including weak and strong abortion and suspension.

- 2. As the instruction set and data path have been developed specifically for Esterel execution, the individual machine instructions can be executed fairly fast. Furthermore, most typical Esterel commands can be expressed directly with just a single KEP command, improving speed further and leading to minimal instruction and data memory usage.

- 3. The KEP also includes an interface block for handling input and output signals, which directly supports testing presence and values of signals across logical instants (corresponding to Esterel's pre operator).

- 4. Throughout the development of the KEP, scalability has been a consideration, hence the allowed number of signals, the nesting depth of preemption primitives, and other design parameters are fully configurable.

The rest of this paper is organized as follows. The next section discusses related work. Section 3 presents the architecture of the KEP2, followed by a description of the KEP assembler. The experimental results are summarized in Section 4. The KEP2 is a single, sequential processor, and hence does not support Esterel's concurrency operator directly, which is probably its most significant limitation so far; this is addressed further in Section 5. Finally, Section 6 gives some concluding remarks and outlines future work. Appendix A elaborates on the instruction set in detail, Appendix B describes the synthesis of a specific KEP configuration, and Appendix C describes the translation of KEP2 assembler into executable codes.

```

% RePIC

ldaaddr 19

% Esterel

abort 0 A

% KEP ASM

emit Z

weak abort

WABORT 1,A,AO

chkabort 0

emit Z;

await

EMIT Z

await B;

11 present B

AWAIT B

12 goto 10

emit X:

EMIT X

await C;

13 emit X

AWAIT C

emit W;

chkabort 0

EMIT W

when A;

await

AO: EMIT Y

emit Y;

present C

goto 15

18 emit W

19 emit Y

. . .

(a)

(b)

(c)

```

Figure 1: An Esterel code fragment involving a weak abort statement (a), and the corresponding assembler code for RePIC (b) and KEP (c).

#### 2 Related Work

As mentioned in the introduction, the only other reactive processor proposals in the sense of Esterel that we are aware of are the ReFLIX and RePIC designs [11, 12, 7], of which RePIC is the more advanced. The RePIC includes an abort handling block, which is used for handling both strong and weak aborts; it does not handle suspension. These abort types are distinguished by the judicious placement of additional instructions in the assembler code. Figure 1(a)/(b) shows an example from Dayaratne et al. [7] for translating the Esterel weak abort statement to the RePIC assembler. The abort handler is configured with a pair of instructions; ldaaddr (line 4) specifies the continuation address, and abort (line 5) indicates the trigger signal. For weak abortion, the RePIC inserts a chkabort instruction before every await instruction within the abort body to determine whether control stays within the abort body in that logical instant. For example, after emitting signal Z (line 8), the chkabort (line 9) determines whether the "await B", encoded in lines 10-12, should be executed next, or whether a jump to the continuation address should be performed, thus aborting the body. As presented there, this would respond correctly to the presence of the abort signal A; however, if A is absent, execution would reach the await-loop in lines 10-12, and would in the following ticks only be sensitive to the awaited signal B, not to the abort trigger signal A. It seems that this could be remedied by including the chkabort instruction within the await-loop (i. e., changing the "goto 10" in line 12 to "goto 9"). However, what we see as the more significant limitation is that this abort handling mechanism seems not as efficient as it could be, especially when considering nests of aborts. For comparison, the KEP handles aborts directly in hardware, without the need for additional assembler instructions to check the presence of abort signals at each control point, thus resulting in more compact and efficient code. To illustrate, consider the KEP assembler shown in Figure 1(c) for the same Esterel example; a single WABORT assembler instruction configures the abort handler, which is then active concurrently with the execution of the abort body, and which autonomously performs the necessary preemption of the abort body (correctly distinguishing between weak and strong aborts) when the abort signal occurs.

```

% Esterel

1

% KEP ASM

module SPEED:

% module SPEED

2

input Centimeter,Second;

3

INPUT Centimeter, Second

3

output Speed:integer;

OUTPUTV Speed

4

VAR Distance

5

var Distance:=0:integer in

6

AO: LOAD Distance,#0

6

abort

7

ABORT 1, Second, A1

every Centimeter do

8

AWAIT Centimeter

Distance:=Distance+1

A2: ABORT 1, Centimeter, A3

9

10

end every

ADD Distance,#1

10

when Second do

11

HALT

emit Speed(Distance)

12

A3: GOTO A2

12

end abort

13

A1: EMITR Speed, Distance

13

end var

14

GOTO AO

14

end.

15

```

Figure 2: SPEED: an example module including valued signals and variables.

Based on RePIC, Dayaratne *et al.* [7] propose an extension to a multi-processor architecture, called EMPEROR, which allows the handling of Esterel's concurrency operator. This is an interesting approach, which could also be applied to the KEP2 to extend the range of acceptable Esterel programs; see also Section 5.

Finally, the KEP2 itself has evolved from earlier designs, the first of which being KEP version 0.1 [9]. This version already implemented the suspension primitives correctly, but did not include the interface block with the support of the **pre**-operator, did not support variables, and did not allow local signals.

# 3 The Kiel Esterel Processor Architecture

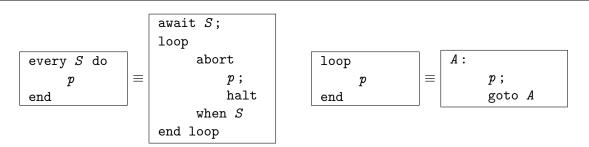

The KEP2 employs a 32-bit wide instruction word with a separate 16-bit wide inner data bus. This gives a range of up to 65535 for the signal counts, which indicate how often a signal must occur before for example an abort is triggered. The KEP assembler language contains thirty instructions. An overview is given in Tables 2 and 3. The most common Esterel statements, including a majority of the reactive kernel statements, can be represented directly. Other Esterel statements can be implemented by standard Esterel syntax translation. To illustrate the compactness of the KEP assembler, consider the Esterel module SPEED [3], shown in Figure 2. This module contains local variables as well as valued signals. To generate the assembler, the translation rules shown in Figure 3 were employed.

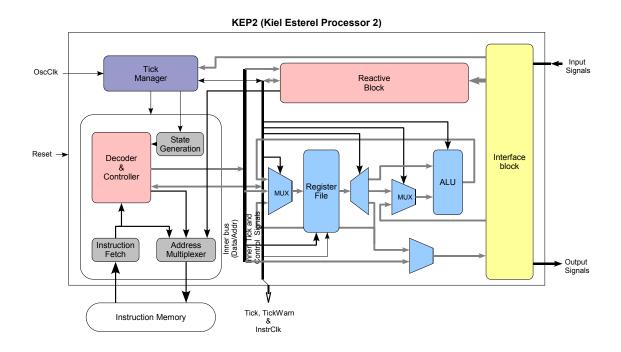

The architecture of the KEP2, shown in Figure 5, is inspired by the three layers that constitute a reactive program [4], i. e., the interface layer, the reactive kernel, and the data handling layer. In the KEP, a Reactive Core decides what computations and what outputs must be generated when it reacts to inputs. An interface block handles input reception and output production. The classical computations are preformed by the data handling block. All of these blocks are scalable and optimized for the Esterel language.

# 3.1 The KEP2 Input/Output Interface

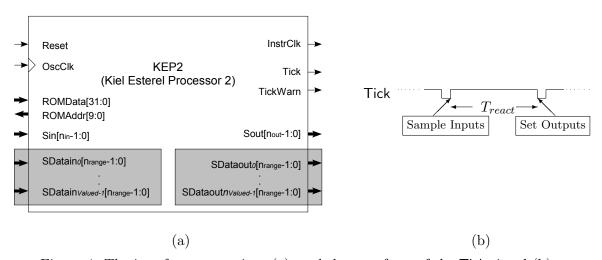

The top-level I/O signals of the KEP2 are illustrated in Figure 4(a). The environment can reset the processor via the Reset pin. An external clock must be connected to the OscClk pin; we use  $T_{osc}$  to denote the rate of that clock. ROMData and ROMAddr are data and address buses

| Mnemonic,                                  | Description                                                              | Corresponding Es-     | See Sec- | See  |

|--------------------------------------------|--------------------------------------------------------------------------|-----------------------|----------|------|

| Operands                                   | -                                                                        | terel Statement       | tion     | page |

| ABORT $n, S,$ $endAddr, startAddr$         | tartAddr Block S                                                         |                       | A.1.1    | 28   |

| WABORT $n, S,$ endAddr, startAddr          | Configures the Watcher in the Reactive Block                             | weak abort            | A.1.2    | 28   |

| SUSPEND 1, $S$ , end $Addr$ , start $Addr$ | Configures the Watcher in the Reactive Block                             | suspendwhen           | A.1.3    | 29   |

| AWAIT S                                    | Configures the AWAIT Element in the Reactive Block                       | await S               | A.2.1    | 30   |

| AWAIT $n, S$                               | Similar to the above, $n$ is the counter value                           | await n S             | A.2.1    | 30   |

| PAUSE (AWAIT TICK)                         | Similar to the above, delays for one instant                             | pause (await<br>tick) | A.2.2    | 30   |

| AWAIT n,TICK                               | Similar to the above, delays for $n$ instants                            | await n tick          | A.2.1    | 30   |

| CAWAIT<br>S,SstartAddr                     | Configures the CAWAIT Element                                            | await case            | A.3.1    | 31   |

| CAWAITE<br>S,SstartAddr                    |                                                                          |                       | A.3.2    | 31   |

| EMIT S                                     | Emits the signal S and keeps it during the current tick                  | emit S                | A.4.1    | 32   |

| EMIT S,#data                               | Emits the valued signal S with data and keeps it during the current tick | emit S(data)          | A.4.1    | 32   |

| EMITR S,reg                                | Emits the valued signal $S$ with contents of the register $reg$          | emit S(var_reg)       | A.4.2    | 32   |

| SUSTAIN S                                  | Sustains the signal $S$                                                  | sustain S             | A.5.1    | 33   |

| SUSTAIN S,#data                            | Sustains the valued signal S with data                                   | sustain S(data)       | A.5.1    | 33   |

| SUSTAINR S, reg                            | Sustains the valued signal $S$ with contents of the register $reg$       | sustain<br>S(var_reg) | A.5.2    | 33   |

| HALT                                       | Halts the system                                                         | halt                  | A.6.1    | 34   |

| NOTHING                                    | Does nothing                                                             | nothing               | A.7.1    | 34   |

| PRESENT S,elseAddr                         | Tests signal S, goes to the address elseAddr if S is not presented       | present S thenend     | A.8.1    | 34   |

| SIGNAL S                                   | Initializes a local signal $S$                                           | signal S inend        | A.9.1    | 35   |

| SIGNAL PRE(S)                              | Executes right after the SIGNAL $S$ instruction                          |                       | A.9.1    | 35   |

| CALL addr                                  | Calls a subroutine which locates on addr                                 | call subroutine       | A.12.2   | 55   |

| RET                                        | Returns from a subroutine                                                |                       | A.12.3   | 55   |

| GOTO addr                                  | Goes to the address addr                                                 |                       | A.12.1   | 54   |

Table 2: Overview of the instruction set architecture (part 1/2).

| Mnemonic,<br>Operands | Description                                                                                                                                                                                                               | Corresponding Esterel Statement                                 | See Section | See<br>page |

|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|-------------|-------------|

| JW Z,elseAddr         | Goes to the address <i>elseAddr</i> if the previous operating result is not <i>zero</i> . Generally it is used right after a SUB instruction to implement the <b>repeat</b> statement                                     | repeat n times                                                  | A.11.1      | 52          |

| JW L,elseAddr         | Goes to the address <code>elseAddr</code> if the previous comparison operating result is not <code>less than</code> . Generally it is used right after a CMP instruction to implement the <code>if</code> statement       | if (A <b) td="" thenelseend<=""><td>A.11.1</td><td>52</td></b)> | A.11.1      | 52          |

| JW G,elseAddr         | Goes to the address elseAddr if the previous comparison operating result is not greater than                                                                                                                              | if (A>B) thenelseend                                            | A.11.1      | 52          |

| JW GE,elseAddr        | Goes to the address elseAddr if the previous comparison operating result is not greater than or equal                                                                                                                     | if (A>=B) thenelseend                                           | A.11.1      | 52          |

| JW LE,elseAddr        | Goes to the address <i>elseAddr</i> if the previous comparison operating result is not <i>less</i> than or <i>equal</i>                                                                                                   | if (A<=B) thenelseend                                           | A.11.1      | 52          |

| JW EE,elseAddr        | Goes to the address <i>elseAddr</i> if the previous comparison operating result is not <i>equal</i>                                                                                                                       | if (A=B) thenelseend                                            | A.11.1      | 52          |

| JW NE,elseAddr        | Goes to the address elseAddr if the previous comparison operating result is equal                                                                                                                                         | if (A<>B) thenelseend                                           | A.11.1      | 52          |

| CLRC                  | Clears carry                                                                                                                                                                                                              |                                                                 | A.10.1      | 35          |

| SETC                  | Sets carry                                                                                                                                                                                                                |                                                                 | A.10.2      | 36          |

| SR reg                | Right shifts the register reg                                                                                                                                                                                             |                                                                 | A.10.3      | 36          |

| SRC reg               | Right shifts the register <i>reg</i> with a carry                                                                                                                                                                         |                                                                 | A.10.4      | 37          |

| NOTR $reg$            | Bitwise logical NOTs the register reg                                                                                                                                                                                     |                                                                 | A.10.5      | 37          |

| LOAD reg,val          | Loads the val to the register reg. The val can be one of the following. (1) #data: an immediate data (2) reg: the contents of a source register (3) ?S: the value of signal S (4) PRE(?S): the previous value of signal S | reg:=val                                                        | A.10.6      | 37          |

| ADD reg,val           | Adds the val to the register reg. See also the LOAD instruction.                                                                                                                                                          | reg:=reg+val                                                    | A.10.7      | 39          |

| ADDC reg,val          | Adds the val to the register reg with the carry. See also the LOAD instruction.                                                                                                                                           |                                                                 | A.10.8      | 40          |

| SUB reg,val           | Subtracts the <i>val</i> from the register <i>reg</i> . See also the LOAD instruction.                                                                                                                                    | reg:=reg-val                                                    | A.10.9      | 41          |

| SUBC reg,val          | Subtracts the <i>val</i> from the register <i>reg</i> with the carry. See also the LOAD instruction.                                                                                                                      |                                                                 | A.10.10     | 43          |

| MUL reg,val           | Multiplies the register <i>reg</i> by the <i>val</i> . See also the LOAD instruction.                                                                                                                                     | reg:=reg*val                                                    | A.10.11     | 44          |

| ANDR $reg, val$       | Bitwise logical ANDs the register <i>reg</i> by the <i>val</i> . See also the LOAD instruction.                                                                                                                           |                                                                 | A.10.12     | 46          |

| ORR reg,val           | Bitwise logical ORs the register reg by the val. See also the LOAD instruction.                                                                                                                                           |                                                                 | A.10.13     | 47          |

| XORR reg,val          | Bitwise logical XORs the register reg by the val. See also the LOAD instruction.                                                                                                                                          |                                                                 | A.10.14     | 49          |

| CMP reg,val           | Compares the contents of the register reg and the val, affects equal and carry bits. See also the LOAD instruction.                                                                                                       |                                                                 | A.10.15     | 50          |

Table 3: Overview of the instruction set architecture (part 2/2).

Figure 3: Translation rules of every and loop statements.

Figure 4: The interface connections (a), and the waveform of the Tick signal (b).

for the instruction memory. There are  $n_{in}$  pins Sin to signal the presence of input signals, and Valued data buses of width  $n_{range}$  to provide values for input signals. There are similar pins and buses for output signals. The InstrClk indicates the instruction clock; each instruction cycle lasts three OscClk cycles. A complete description of the I/O signals can be found in Table 4

| Signal                        | Direction | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-------------------------------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Reset                         | Input     | To reset the KEP2 and to generate a Reset Event, assert this input High for at least one OscClk cycle. A Reset Event is automatically generated, and all outputs will be set to '0'.                                                                                                                                                                                                                                                                                                                                                                                              |

| OscClk                        | Input     | The frequency may range from DC to the maximum operating frequency of the circuit, for example as reported by the FPGA development software. In KEP2, one instruction cycle equals three OscCLK cycles.                                                                                                                                                                                                                                                                                                                                                                           |

| ROMAddr[9:0]                  | Output    | The ROMAddr address bus is an output bus from the KEP2 and it indicates the instruction memory address. RO-MAddr[9:0] will be set to "0000000000" if Reset is set.                                                                                                                                                                                                                                                                                                                                                                                                                |

| ROMData[31:0]                 | Input     | The ROMData data bus is an input bus to the KEP2 and it carries encoding data from instruction memory. When the ROMAddr changes, the new ROMData will be valid on the following clock rising edge.                                                                                                                                                                                                                                                                                                                                                                                |

| InstrClk                      | Output    | InstrClk is an output from KEP2 and it indicates the instruction cycle. It is set to '0' when Reset is set.                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Tick                          | Output    | Tick is an output from KEP2 and it indicates the logical tick of Esterel. It is set to '0' when Reset is set.                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| TickWarn                      | Output    | TickWarn is an output from KEP2 and it is kept high once the physical time of an instant extends the preconcerted value.                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| $Sin[n_{in}-1{:}0]$           | Input     | Presents and keeps valid input signals on this port during the Tick set (high) period. The $n_{in}$ depends on the amount of input signals. e. g., $n_{in}$ equals 8 (Sin[7:0]) when there are 8 input signals. KEP2 supports up to 63 input signals.                                                                                                                                                                                                                                                                                                                             |

| $SDataini[n_{range}-1:0]$     | Input     | Carried data of valued signal S appears on the SDataini $[n_{range}:0]$ port. $i$ ranges from 0 to $n_{valued}-1$ , where $n_{valued}$ is the number of valued signals. $n_{range}$ depends on the range of carried data. For example, assume there are two valued signals, and the range of carried data is from 0 to 200 (decimal). Two ports would be generated. One is SDatain0[7:0] which corresponds to Sout[0], and the other is SDataout1[7:0] which corresponds to Sout[1]. $n_{range}$ is up to 16 (16-bit), which corresponds to values from 0 to $2^{16}$ -1 = 65535. |

| $Sout[n_{out}-1{:}0]$         | Output    | Output signals appear on this port until the current Tick is finished (falling edge). The $n_{out}$ depends on the amount of output signals, see also $Sin[n_{in} - 1:0]$ . KEP2 supports up to 63 output signals.                                                                                                                                                                                                                                                                                                                                                                |

| SDataout $i[n_{range} - 1:0]$ | Output    | Carried data of valued signal S appears on the SDataouti $[n_{range}:0]$ port. See also SDataini $[n_{range}-1:0]$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

Table 4: KEP2 Interface Signals Descriptions.

The Tick pin indicates the logical tick of Esterel. Figure 4(b) shows a waveform of the Tick signal. The activated period (Tick high) is  $T_{react}$ , which indicates the reaction time of the module. A gap of length  $T_{osc}$  identifies when the inputs are sampled and when the outputs are generated by the reactive processor. The processor samples the inputs on the Tick rising edge, and holds the outputs generated during a logical tick until the Tick falling edge. The deactivated

Figure 5: The architecture overview.

period (Tick low) leaves a period for the environment to modify the inputs.

#### 3.2 The KEP Tick Manage

The KEP has a special valued signal \_TICKLEN, which can be set to a certain value by the assembler program to define an upper bound on the number of instructions that may be executed within a logical tick. When the program executes an "EMIT \_TICKLEN" instruction, generally at the beginning of a module, this initializes the Tick Manager. When more than \_TICKLEN instructions have been executed since the last tick delimiting instruction (pause or await), the Tick Manager considers this a tick length timing violation. In this case, the current tick length will be extended automatically until the tick is finished. Furthermore, the timing violation is signaled to the environment via the TickWarn pin.

The programmer can try to find an appropriate value for \_TICKLEN and add a corresponding emit statement to the assembler program. However, we have also developed an analysis procedure that automatically performs this Worst Case Reaction Time (WCRT) analysis [10]. This analysis has been integrated into a compiler that translates Esterel to KEP assembler and automatically sets \_TICKLEN.

#### 3.3 The Reactive Core

The implementation of Esterel's reactive statements relies on the cooperation of the KEP2's Decoder & Controller and the Reactive Block, which together form the Reactive Core. The Reactive Block contains a Preemption Element, which contains a configurable number of Watcher modules, that are responsible for implementing the preemption operations. The Reactive Block also contains the AWAIT and CAWAIT Elements, implementing single and concurrent signal awaiting, and the PRESENT Element, testing for signal presence.

Figure 6: The structure of the Watcher.

#### 3.3.1 The Preemption Element

According to the Esterel semantics, a preemption (abortion or suspension) is *enabled* when control is in its body, and *disabled* when control is outside of its body. When a preemption is *enabled*, the corresponding trigger signal is watched and the module can react to the presence of it (is *active*). Otherwise, the signal does not cause preemption. We call this scheme *Inside/Outside Preemption Range Watching (IOPRW)*.

A Watcher, shown in Figure 6, contains two functions to implement the IOPRW, the Enable Watcher and the Trigger Watcher. The *Enable Watcher* watches the program counter PC and compares it with the corresponding preemption's start and end addresses. Based on that, it decides whether this preemption should be in the *enabled state* or in the *disabled state*. If the watched signal is present on the Tick rising edge and the Watcher is in the enabled state, the Watcher triggers a corresponding action, unless it is overridden by another Watcher with higher priority, *e. g.*, an enclosing nesting activates a suspension and freezes the state of its body. Once the Watcher changes its state from disabled to enabled, which means that the PC re-enters the watching range, the SignalCount will be reloaded into the counter.

The function of the *Trigger Watcher* depends on the configuration of the Watcher. For an abortion, it watches the trigger signal; if the signal occurs, the Watcher goes into the *triggered state* and counts down the signal count; then, depending on whether the trigger signal count specified by the abortion statement has already been reached, the Watcher decides whether it should go into the *terminated state*, which would kill the abort body, or not. For a suspension, the Watcher watches the trigger signal and decides whether the suspension body ought to go into the *suspended state* or not. Once an abortion is terminated or a suspension is activated, a TW event will be emitted.

Figure 7 shows the architecture of a Reactive Block including three Watcher modules. To illustrate its operation, consider the Esterel module NESTED in Figure 8(a), which is an example of a nested preemption. After starting, the module watches C and A as the abortion trigger signals, and B as the suspension trigger signal. The execution stays on line 8 to wait for signal

Figure 7: Architecture of a Reactive Block with three Watchers.

Figure 8: NESTED: the Esterel module illustrating the preemption statements (a), the KEP assembler program (b), and an execution trace (c).

D. Those three preemptive statements constitute a mixed preemption nest, and the priority of the outer preemptive statement is higher than that of the inner one. Figure 8 (b) shows the corresponding KEP assembler program of the NESTED module. Figure 8 (c) shows a possible execution trace.

When executing NESTED, first the watchers Watcher0, Watcher1 and Watcher2 are configured via three preemption instructions (lines 6–8). The PC stays at address (6) (line 9) until any of the signals A, B, C, or D occur. Since this address is within each of the watchers' watching range, all of the watchers are enabled now.

If B and C occur simultaneously, TW1 and TW2 are set at the same time. The Preemption-Flag1 indicates a suspension, and PreemptionFlag2 indicates strong abortion. The PriorityController processes TW events based on rules about priorities and preemption types of Watchers according to the Esterel semantics. In this case, the suspension triggered by B has higher priority. The PriorityController maps Watcher1's outputs to the Reactive Block's output, so the Preemption Element's TP, which means Trigger Preemption, is '1' for denoting an active preemption, and the PreemptionFlag indicates a suspension. The generated control signals will be broadcast to all of the lower priority watchers and other relevant elements. Watcher2 receives the result of the PriorityController, and since the current active preemption is a suspension, Watcher2 will keep its state, which means that the counter of this watcher will not be decremented. A decoder analyzes the TP and PreemptionFlag signals, and decodes them to three signals of the Reactive Block, *i. e.*, rdAbort, weakFlag and rdSuspend, which indicate the current active preemption for the Decoder & Controller. The Decoder & Controller checks the rdAbort, weakFlag, rdSuspend, rdAWAIT, and so on, simultaneously. Since the active preemption is a suspension, the KEP keeps its state until the current tick is finished.

Assuming now that the signals C and D occur simultaneously in the next instant, Watcher2 takes priority. The outputs of Watcher2 are mapped to that of the Preemption Element, so the

Reactive Block's rdAbort is '1' to denote that there is an active abortion. The returnAddr equals 8 (the next instruction address behind the body of abortion C), and the weakFlag is '0' to indicate a strong abortion type. Since the sensitive signal of the AWAIT statement is present, the AWAIT Element sets rdAWAIT to '1' to denote that AWAIT is terminated. The Decoder & Controller checks the rdAbort, weakFlag and rdAWAIT signals and responds to the strong abortion. The returnAddr is mapped to the PC via the Address Multiplexer. The KEP jumps to address 8 and executes "EMIT F" and "AWAIT D".

When signals A and D occur simultaneously in the following instant, weak abortion A takes priority. The PriorityController maps Watcher0's outputs to that of the Preemption Element, so the Reactive Block's rdAbort is '1' to denote an active abortion, the returnAddress equals 13 (the next instruction address behind the body of abortion A), and the weakFlag is '1' to indicate a weak abortion type. At the same time, the AWAIT Element sets rdAWAIT to '1' to denote that the AWAIT is terminated. Since the active abortion is a weak abortion, the KEP will respond to the terminated AWAIT instruction first. "EMIT E" (10) is executed and then the "AWAIT D" (11) is fetched. Since it is a non-instantaneous statement, the Reactive Core will ignore it, and instead respond to the weak abortion. The returnAddress is mapped to the PC, and then control jumps to (13). The KEP executes "EMIT H" (13) and HALT (14).

#### 3.3.2 The AWAIT Element

The above case illustrates how the KEP deals with different preemption types. The KEP correctly and very efficiently implements abort/weak abort/suspend statements and allows arbitrary nesting. The Reactive Block includes further elements to directly implement the majority of reactive statements of Esterel.

The AWAIT and PAUSE instructions are handled by the AWAIT Element, which is shown in Figure 9. The AWAIT Element contains two parameter registers. One registers the watched signal coder value and the other registers the counter value. The element watches sensitive signal on Tick rising edge. If the watched signal is '1', the counter value will be deducted. When the counter value equals zero, the AWAIT Element sets rdAWAIT to '1' to denote the termination of AWAIT.

When the Reactive Core executes an AWAIT or PAUSE instruction for the first time, it configures the AWAIT Element via inner buses. Then after the end of the current tick, the Decoder & Controller waits for the terminating signal from the AWAIT Element. If the Reactive Core responses to an active abortion before the current AWAIT instruction terminates, the AWAIT instruction will be cancelled.

#### 3.3.3 The CAWAIT Element

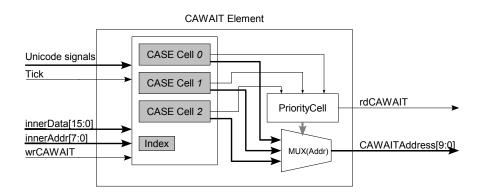

The CAWAIT Element watches several signals in parallel. The architecture of the CAWAIT Element is similar to that of the Preemption Element Element. Every CASE Cell includes two parameters, i.e. SignalCoder and CASEAddr. The CASEAddr registers the start address of the case body. The SignalCoder indicates which signal ought to be watched. Figure 11 illustrates a CAWAIT Element which includes three CASE Cell.

When several watched signals occur simultaneously, the corresponding CASE Cells are all active. The PriorityCell chooses the first active one in the list to take priority. In other words, the earlier case takes priority. The Decoder & Controller will respond to this event and jump to the registered address.

#### 3.3.4 The PRESENT Element

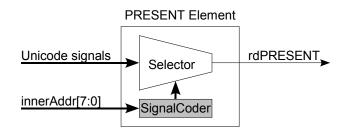

The implementation of PRESENT statement depends on the PRESENT Element, which is shown in 11. The basic form of the Esterel PRESENT statement checks for one signal expression and

Figure 9: Architecture of the AWAIT Element.

Figure 10: Architecture of a CAWAIT Element, with 3 CASE Cells.

Figure 11: Architecture of the PRESENT Element.

performs binary branching. We map  $26_{th}$  to  $19_{th}$  bit of instruction encoding to the selected-signal-coder port of the PRESENT Element. The value of the selected signal is immediately put to an output port which is named as rdPRESENT.

Considering the stages of instruction execution, the selected signal's coder is emitted when KEP2 fetches a PRESENT instruction. When the Core executes the instruction, it just needs to test the rdPRESENT signal to decide whether to branch or not.

#### 3.4 The Interface Block

The Interface Block is created as an interface layer of the reactive system. Figure 12 shows the architecture of an Interface Block, which here is configured with four pure and two valued inputs and outputs. The width of the valued signals' carried data is configured to be eight bits.

The Interface Block supports the pre operation (introduced in Esterel V5.91), which allows to access the previous presence status and value of a signal, directly in hardware. There are two basic pre modes. One is the pre(S), which indicates the previous status of signal S, i.e., its presence status in the previous instant. The other is pre(S), which expresses the value of signal S in the previous instant.

| Signal   | $d_7 - d_2$ | $d_1$ | $d_0$ |                                |                     |                            |

|----------|-------------|-------|-------|--------------------------------|---------------------|----------------------------|

| _TICKLEN | 000000      | 0     | 0     |                                |                     |                            |

| A        | 000001      | 1     | 0     | Bit field                      | Value               | Meaning                    |

| В        | 000010      | 1     | 0     |                                |                     | Wicannig                   |

| C        | 000011      | 1     | 0     | $d_{31} - d_{27}$              | 0011 1              | Opcode                     |

| G        | 000001      | 0     | 0     | $d_{26} - d_{19}$              | 000 0010 0          | The signal's unicode value |

| H        | 000010      | 0     | 0     | $d_{18} - d_{16}$              | 000                 | The extended code          |

| I        | 000011      | 0     | 0     | $d_{15} - d_{00}$              | 0000 0000 0001 1001 | The carried data           |

| PRE(A)   | 000001      | 1     | 1     | $\frac{a_{15}-a_{00}}{a_{10}}$ | 0000100001000111001 | The carried data           |

| PRE(I)   | 000011      | 0     | 1     |                                |                     |                            |

| X        | 000001      |       |       |                                |                     |                            |

|          | (a)         |       |       |                                | (b)                 |                            |

Table 5: The signal codes of the INOUT module (a), and the break down of the instruction encoding of the EMIT G,#25 instruction (hexadecimal 0x38200019) with indications for the half bytes (b).

To illustrate how the Interface Block deals with the input and output signals, consider the INOUT module shown in Figure 13(a), and the corresponding compiled KEP assembler program

# Interface Block Sin[5:0] Unicode signals Pre Signal Register Unicoder Distribute Register File Pre Value Register File SDatain0[7:0] Register Register SDatain1[7:0] Register Register Register Register Tick innerData[15:0] regDatIn[7:0]] innerAddr[7:0] innerMark[2:0] Output Register Sout[5:0] 🔪 Distribute Register File Register SDataout0[7:0] regDatOut[7:0] Register SDataout1[7:0] wrEmit TickLenData Register

Figure 12: The architecture of an Interface Block.

```

% Esterel

1

module INOUT:

2

input A:integer;

INPUTV A,B

3

input B:integer,C;

INPUT C

4

2

output G:integer;

OUTPUTV G,H

3

5

output H:integer,I;

4

OUTPUT I

6

7

var X in

5

VAR X

[0000] {38000005}

await A;

6

EMIT _TICKLEN #5

present C then

[0001] {30300001}

AWAIT A

7

emit I;

[0002] {10700004}

PRESENT C, AO

10

8

end present;

9

[0003] {38600000}

EMIT I

11

await B;

10

[0004] {30500001} AO: AWAIT B

12

[0005]

PRESENT PRE(I), A1

present pre(I) then

{10680009}

11

13

emit G(25);

EMIT G,#25

[0006]

{38200019}

14

12

[0007]

{A03E0400}

LOAD X, PRE (?A)

X:=pre(?A);

13

15

emit H(X);

[8000]

{90400400}

EMITR H,X

14

16

end present;

[0009]

{28000000} A1: HALT

17

15

halt;

18

end.

19

(a)

(b)

```

Figure 13: INOUT: an Esterel module illustrating the processes of I/O statements (a), and the compiled KEP assembler program.

shown in Figure 13(b). Table 5(a) shows the signal codes of the INOUT module. The \_TICKLEN is a reserved name of a valued signal for configuring the Tick Manager, see Section 3. The signal code is 8 bits wide. Bit 0 is used as the pre extended bit of the original signal. Bit 1 is used to describe the signal type, i. e., '1' indicates an input type signal. Bits 7–2 further identify the signal. In this way, all of the signals' current or previous states are mapped to a set of signals and can be accessed directly. A similar method is used for the values of signals and for variables (which are similar to valued signals, but do not carry a presence status). Table 5(b) shows the encoding of an EMIT instruction. Bits 26–19 of an instruction are the Unicode Signals code. In the KEP, all the input and output signals are recoded into a Unicode Signals bus, which can be accessed by the inner blocks and elements directly.

The first instruction in INOUT is "EMIT \_TICKLEN, #5". The emitted value is transmitted to the TickLenData port and received by the Tick Manager for initialization. Then "AWAIT A" configures the AWAIT Element in the Reactive Block. Control stays there and waits for the trigger signal.

Assume the valued input signal A and pure signal C are both present after the initial instant, and A carries the value 20. The Reactive Block sets rdAWAIT to '1' to denote that AWAIT is terminated. The Unicode Signals are multiplexed to the Selector of the PRESENT Element in the Reactive Block. When the "PRESENT C, AO" instruction is fetched, the MUX maps signal 00001110b to the rdPRESENT signal. Since C is present in this instant, the rdPRESENT is high to skip the branch. Then the "EMIT I" is executed, and the output register locks the presence of the emitted signal until the current tick ends. The execution of "AWAIT B" causes the KEP to wait for the next tick.

When the following instant starts, the old status of input and output signals will be written into the Pre Signal Register, and then regarded as the previous signal status ("pre(S)" in Esterel). The carried data of valued signals ("?S") will be written into the Pre Value register file, and can be accessed as the previous value ("pre(?S)"). Assuming that signal B is present, "AWAIT B" terminates. Since the signal I was emitted in the previous instant, PRE(I) is present. Therefore, the "PRESENT PRE(I), A1" instruction will not branch, and "EMIT G,#25" will be

```

% Esterel

% KEP ASM

1

module REINC:

2

% module REINC

2

INPUT S

input S;

3

3

OUTPUT 01,02

output 01,02;

4

loop

5

5

signal S in

SIGNAL S

6

6

present S then

PRESENT S, A1

7

7

emit 01;

EMIT 01

8

8

else

GOTO A2

9

9

emit 02;

10

A1:

10

EMIT 02;

11

end:

11

pause;

12

A2:

12

emit S

13

PAUSE

13

14

end signal

14

EMIT S

end loop

GOTO AO

15

(a)

(b)

```

Figure 14: REINC: Translation of the Esterel signal declaration (a) into to the KEP SIGNAL instruction (b).

executed. The valued signal G consists of two interface hardware objects: a pure signal, which indicates signal presence or absence, and a signal bus, which conveys signal values. The inner buses of the KEP transmit the data to a MUX which selects the source of the data. The data on the inner data bus is selected and written into a distributed register file, and then issued as the value of G.

The instruction "LOAD X,PRE(?A)" causes the previously registered data of signal A to be taken from the Pre Value register file, and to be mapped to the regDatln[7:0] port via MUXs. The Decoder & Controller will write the data into the register file of the processor. The implementation process of the "EMITR H,X" is similar to that of the "EMIT G,#25" instruction, except that the source of the data is the register file of the processor instead of the inner data bus.

#### 3.5 Local Signals

Another feature of the Interface Block is the handling of local signals, which are declared in Esterel with a signal declaration. Unlike the (global) interface signals, a local signal has a limited scope. This may results in *reincarnation* [3]; *i. e.*, in case of an instantaneous repetition of loops, local signals can have several simultaneous instantiations.

The SIGNAL instruction implements a signal scope and correctly handles reincarnation. In the KEP, a local signal is implemented by a pair of connected I/O ports. When executing a "SIGNAL S" statement, the presence status and value of S is cleared, thus effectively introducing a fresh signal. To illustrate, consider the Esterel module REINC, shown in Figure 14 along with the corresponding KEP assembler. In the first instant, the local signal S is declared and initialized. Therefore, its status is absent. The else branch of the present statement is taken and OS is emitted. In the second instant, S is emitted. The loop body terminates and then it is restarted. The local signal declaration is immediately re-initialized, and the fresh incarnation is absent. The present statement tests the fresh incarnation and only OS is emitted.

# 4 Experimental Results

To quantitatively compare the data handling abilities between the Esterel processor and other implementations, we used the CURVE module (contained in the mca200 test bench [6]) as an example, since it is a typical module that includes varied data handling statements. Table 6 compares the resource usages of the KEP2 with different hard- and software implementations. For the hardware implementations, we synthesize the module to VHDL with the Esterel V7 compiler, since other hardware compilers cannot support valued signals. The V7 compiler does not provide a data ranging function, i. e., an integer type valued input signal will always occupy a 32-bit bus to represent the carried value. As an optimization, we manually resized all of the valued signals and variables to 16-bit width, since that range is sufficient for this Esterel module. Then those VHDL programs are implemented by the ISE6.3, and the speed (default) optimization is used. For the software implementation, we use the CEC V0.3 compiler to synthesize the module to a C program, which is then compiled onto the 32-bit Microblaze soft processor core, and the MCS51, which is a classical widely used 8-bit processor.

|                   | KEP-C<br>(16-bit) | Hardware (32-bit) | Hardware (16-bit) | MCS51 <sup>(1)</sup><br>(8-bit) | Microblaze <sup>(2)</sup> (32-bit) |

|-------------------|-------------------|-------------------|-------------------|---------------------------------|------------------------------------|

| Logic Cells       | 1384              | 1510              | 968               | -                               | 1906                               |

| Code size (words) | 185               | -                 | -                 | $1070^{(3)}$                    | 436                                |

| Code size (bytes) | 740               | -                 | -                 | 1636                            | 1744                               |

| RAM Usage (words) | 9                 | -                 | -                 | 31                              | 19                                 |

| RAM Usage (bytes) | 18                | -                 | -                 | 31                              | 76                                 |

- (1) Compiled by Keil C51 compiler V6.12. The level 8 (default) optimization is used.

- (2) Compiled by gcc (for Microblaze) version 2.95.3-4. The level 2 (default) optimization is used.

- (3) The lengths of MCS51's instructions vary; here, a word represents a complete assembler line.

Table 6: The codes size and RAM usage (in word) comparison of CURVE implementation between KEP2, MCS51, and Microblaze.

To evaluate the performance of the KEP2, we use some standard test cases [3, 1, 6]. Those modules are typical Esterel applications, which not only contain the reactive statements, but also include arithmetic and logical data handling. However, we leave out the module which contains the **pre** operator, since the CEC compiler does not support it [5]. The module is first translated into the KEP assembler program and then compiled to the KEP executable codes. This is then compared with software synthesis results of the Esterel Compiler V5.92, the Esterel Compiler V7 and the CEC compiler 0.3. Table 6 reveals that the code for the 32-bit processor is smaller than that of a 8-bit processor (in words). Therefore, we use the Microblaze as reference point in the following.

Tables 7 and 8 illustrates the comparison of executable code size and RAM usage between the KEP implementation and the Microblaze software implementation. The optimized data path of the KEP results on average in a 89% reduction of codes size and 77% reduction of RAM usage in words (or 89% reduction in bytes) when compared with the best result of the Microblaze implementation.

The Esterel module's line count is very close to the KEP2's codes size (in words). This fact implies that the KEP handles the Esterel statements on a high level. Practically, the majority of Esterel statements can be translated into KEP assembler instructions word by word.

As mentioned in the introduction, the KEP has been designed to be highly configurable. Table 9 compares five different KEP2 variants which include different elements to target various applications. The KEP2-E offers similar functions to RePIC and can be compared with RePIC

| Module name      | Esterel |      | Microblaze (words <sup>(1)</sup> ) |     | KEP2    |

|------------------|---------|------|------------------------------------|-----|---------|

|                  | lines   | V5   | V7                                 | CEC | (words) |

| SPEED            | 11      | 276  | 1081                               | 253 | 11      |

| BELT_CONTROL     | 14      | 440  | 1169                               | 340 | 18      |

| TIMER            | 6       | 368  | 1160                               | 295 | 9       |

| CONTROLLER       | 26      | 560  | 1226                               | 487 | 24      |

| DEBOUNCE         | 31      | 392  | 1198                               | 299 | 28      |

| ALARM_COMPARE    | 16      | 315  | 1109                               | 265 | 14      |

| SPEEDOMETER      | 23      | 328  | 1145                               | 293 | 20      |

| DASHBOARD_TIMER  | 77      | 617  | 1388                               | 541 | 65      |

| FRC              | 26      | 375  | 1163                               | 313 | 18      |

| CURVE            | 190     | 1307 | 2017                               | 436 | 185     |

| BAT_DIAG         | 45      | 487  | 1274                               | 378 | 63      |

| VER_ACC_DIAG     | 38      | 433  | 1229                               | 303 | 41      |

| LONG_SPEED_STRAT | 60      | 573  | 1306                               | 319 | 56      |

<sup>(1)</sup> For the code size, one word equals four bytes.

Table 7: Comparison of the codes sizes, in words.

| Module name      | Microblaze (RAM words/bytes) |        |       | KEP2              |

|------------------|------------------------------|--------|-------|-------------------|

|                  | V5                           | V7     | CEC   | (RAM words/bytes) |

| SPEED            | 13/52                        | 12/48  | 9/36  | 1/2               |

| BELT_CONTROL     | 16/64                        | 18/72  | 10/40 | 0/0               |

| TIMER            | 14/56                        | 14/56  | 10/40 | 0/0               |

| CONTROLLER       | 18/72                        | 22/88  | 17/68 | 0/0               |

| DEBOUNCE         | 18/72                        | 17/68  | 12/48 | 4/8               |