# Interactive Model-Based Compilation

A Modeller-Driven Development Approach

Dipl.-Inf. Steven Smyth

Dissertation

zur Erlangung des akademischen Grades

Doktor der Ingenieurwissenschaften

(Dr.-Ing.)

der Technischen Fakultät

der Christian-Albrechts-Universität zu Kiel

eingereicht im Jahr 2020

```

URN:NBN urn:nbn:de:gbv:8:1-zs-00000374-a1

ISSN 2193-6781 (print version)

ISSN 2194-6639 (electronic version)

Electronic version, updates, errata available via https://www.informatik.uni-kiel.de/kcss

The author can be contacted via ssm@rtsys.org

Published by the Department of Computer Science, Kiel University

Real-Time and Embedded Systems Group

Please cite as:

⊳ Steven Smyth. Interactive Model-Based Compilation — A Modeller-Driven Development Ap-

proach 2021/1 in Kiel Computer Science Series. Department of Computer Science, 2021.

Dissertation, Faculty of Engineering, Kiel University.

@book{Smyth21,

= {Steven Smyth},

author

title

= {Interactive Model-Based Compilation

--- A Modeller-Driven Development Approach},

publisher = {Department of Computer Science, CAU Kiel},

vear

= {2021},

number

= \{2021/1\},

doi

= \{10.21941/kcss/2021/1\},

series

= {Kiel Computer Science Series},

= {Dissertation, Faculty of Engineering,

note

Kiel University.}

}

© 2021 by Steven Smyth

```

Kiel Computer Science Series (KCSS) 2021/1 dated 2021-04-01

# **About this Series**

The Kiel Computer Science Series (KCSS) covers dissertations, habilitation theses, lecture notes, textbooks, surveys, collections, handbooks, etc. written at the Department of Computer Science at Kiel University. It was initiated in 2011 to support authors in the dissemination of their work in electronic and printed form, without restricting their rights to their work. The series provides a unified appearance and aims at high-quality typography. The KCSS is an open access series; all series titles are electronically available free of charge at the department's website. In addition, authors are encouraged to make printed copies available at a reasonable price, typically with a print-on-demand service.

Please visit http://www.informatik.uni-kiel.de/kcss for more information, for instructions how to publish in the KCSS, and for access to all existing publications.

1. Gutachter: Prof. Dr. Reinhard von Hanxleden

Christian-Albrechts-Universität zu Kiel

Kiel

2. Gutachter: Prof. Dr. Bernhard Steffen

Technische Universität Dortmund

Dortmund

Datum der mündlichen Prüfung: 07.12.2020

# **Abstract**

There is a growing tendency for using domain-specific languages, which help domain experts to stay focussed on abstract problem solutions. It is important to carefully design these languages and tools, which fundamentally perform model-to-model transformations. The quality of both usually decides the effectiveness of the subsequent development and therefore the quality of the final applications. However, as the complexity and safety requirements of modern systems grow, it becomes increasingly burdensome to create highly customized languages and difficult to provide reasonable overviews within these tools.

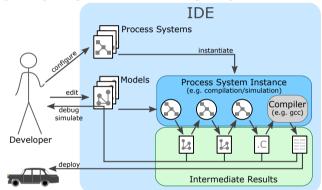

This thesis introduces a new interactive model-based compilation methodology. Compilations for arbitrary model-to-model transformations are themselves described as models. They can be instantiated for particular inputs, e. g. a program, to create concrete compilation runs, which return the result of that compilation. The compilation instance is interactively observable. Intermediate results serve as new inputs and as documentation. They can be used to create highly customized views and facilitate understandability. This methodology guides modellers from the start of the compilation to the final result so that they can interactively refine their models.

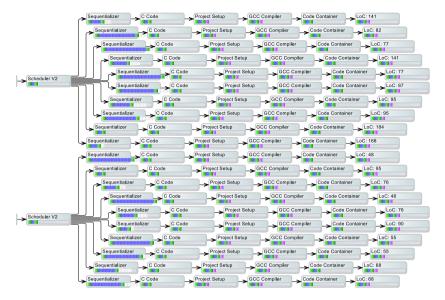

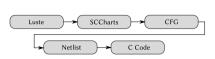

The methodology has been implemented and validated as the KIELER Compiler (KiCo) and is available as part of the KIELER open-source project. It is used to implement the current reference compiler for the SCCharts language, a statecharts dialect designed for specifying safety-critical reactive systems based on a synchronous model of computation. The interactive model-based compilation approach was key to the rapid prototyping of three different compilation strategies, as well as new language extensions, variations and closely related languages. The results are verified with benchmarks, which are again modelled using the same approach and technology. The usability of the SCCharts language and the KiCo tooling is documented with long-term surveys and real-life industrial, academic and teaching examples.

# Zusammenfassung

Es gibt eine steigende Tendenz im Einsatz von domänen-spezifischen Sprachen, welche den Experten dieser Domänen helfen sollen, sich auf die eigentlichen abstrakten Problemlösungen zu konzentrieren. Diese Sprachen und Werkzeuge, welche grundlegend Model-zu-Model-Transformationen ausführen, müssen sorgsam entwickelt werden. Für gewöhnlich entscheidet die Qualität beider über die Effektivität des nachfolgenden Entwicklungsprozesses und letztlich über die Qualität der finalen Anwendungen. Da die Komplexität moderner Systeme, zum Beispiel durch erhöhte Sicherheitsanforderungen, stetig steigt, wird es zunehmend mühsam, maßgeschneiderte Sprachen und Werkzeuge mit verständlichen Übersichten zu erstellen.

Diese Arbeit führt eine neue, interaktive, modell-basierte Übersetzungsmethodik ein. Übersetzungen für beliebige Modell-zu-Modell-Transformationen sind ebenfalls als Modelle definiert. Sie werden für bestimmte Eingaben, wie z.B. Programme, initialisiert, um konkrete Übersetzungsläufe zu starten. Die gesamte Instanz ist interaktiv beobachtbar und das finale sowie alle Zwischenergebnisse werden verständlich veranschaulicht. Diese dienen als neue Eingaben und zur Dokumentation. Sinnvolle, dedizierte Ansichten fördern das Verständnis des Modellierers. Diese Methodik leitet den Modellierer von Beginn an bis hin zum Endergebnis der Übersetzung, so dass die Modelle interaktiv verfeinert werden können.

Die Methodik ist als KIELER Compiler (KiCo) im KIELER Open-Source-Projekt implementiert. Sie dient als Grundlage für den aktuellen Referenz-Übersetzer der SCCharts-Sprache, einen Statecharts-Dialekt, welcher für die Spezifikation von sicherheitskritischen Systemen entwickelt wurde und auf einem synchronen Berechnungsmodell basiert. Der interaktive, modellbasierte Übersetzungsansatz spielt eine Schlüsselrolle in der Prototypenentwicklung von drei verschiedenen Übersetzungsstrategien für SCCharts, neuen Spracherweiterungen und verwandten Sprachen. Die Ergebnisse werden mittels Vergleichswerten, modelliert mit dem gleichen Ansatz und der

gleichen Technologie, überprüft. Die Benutzbarkeit der SCCharts-Sprache und von KiCo ist mit Langzeitstudien, industriellen, akademischen und auch Lehrbeispielen aus der Praxis dokumentiert.

Nothing's as good if you don't share it.

— After Life by Ricky Gervais

# **Contents**

| 1  | Intr                            | oduction                                      | 1   |  |  |  |

|----|---------------------------------|-----------------------------------------------|-----|--|--|--|

|    | 1.1                             | Contributions                                 | 6   |  |  |  |

| 2  | Prel                            | liminaries                                    | 13  |  |  |  |

|    | 2.1                             | SCCharts                                      | 13  |  |  |  |

|    | 2.2                             | The KIELER SCCharts Modelling Tool            | 23  |  |  |  |

|    | 2.3                             | Related Work                                  | 26  |  |  |  |

| Ι  | Int                             | eractive Model-Based Compilation              | 57  |  |  |  |

| 3  | Model-Based Compilation Systems |                                               |     |  |  |  |

|    | 3.1                             | A Generic User Story                          | 59  |  |  |  |

|    | 3.2                             | Modelling Foundations                         | 65  |  |  |  |

|    | 3.3                             | Interactive Compilation Systems               | 73  |  |  |  |

|    | 3.4                             | Derived Compilation Systems                   | 91  |  |  |  |

| 4  | Inte                            | Interactive Prototyping                       |     |  |  |  |

|    | 4.1                             | Interactive Guidance                          | 96  |  |  |  |

|    | 4.2                             | Compilation Systems Universes                 | 107 |  |  |  |

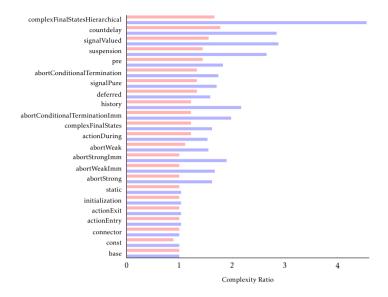

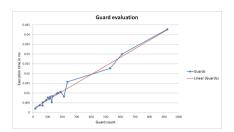

|    | 4.3                             | Transformation Complexity                     | 110 |  |  |  |

| II | В                               | eyond Compiling SCCharts                      | 115 |  |  |  |

| 5  | Inte                            | ractive Compilation for SCCharts              | 117 |  |  |  |

|    | 5.1                             | The Sequentially Constructive Kernel Language | 118 |  |  |  |

|    | 5.2                             | Netlist-Based Compilation                     | 125 |  |  |  |

|    | 5.3                             | Priority-Based Compilation                    | 182 |  |  |  |

## Contents

|     | 5.4                          | State-Based Compilation              | 193  |  |  |  |

|-----|------------------------------|--------------------------------------|------|--|--|--|

|     | 5.5                          | Evaluation of Compilation Approaches |      |  |  |  |

| 6   | Rapid Prototyping            |                                      |      |  |  |  |

|     | 6.1                          | Scheduling Directives                | 237  |  |  |  |

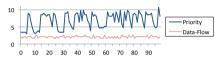

|     | 6.2                          | SCCharts Dataflow                    | 247  |  |  |  |

|     | 6.3                          | Symmetrical Actions                  | 267  |  |  |  |

|     | 6.4                          | Sequentially Constructive Esterel    | 270  |  |  |  |

|     | 6.5                          | Model Extraction of C Code           | 274  |  |  |  |

|     | 6.6                          | SCCharts Language Evaluation         | 277  |  |  |  |

| 7   | Prac                         | etical Applications                  | 303  |  |  |  |

|     | 7.1                          | Specification and Verification       | 304  |  |  |  |

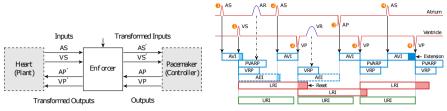

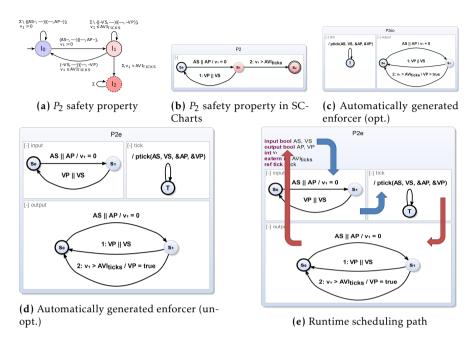

|     | 7.2                          | Runtime Enforcement                  | 312  |  |  |  |

|     | 7.3                          | Teaching                             | 315  |  |  |  |

| 8   | Con                          | clusion                              | 329  |  |  |  |

| O   | 8.1                          | Summary                              |      |  |  |  |

|     | 8.2                          | Future Work                          |      |  |  |  |

|     | D 1                          | 1                                    | 0.41 |  |  |  |

| A   | Pub                          | lications                            | 341  |  |  |  |

| В   | Rela                         | ated Modelling Tools                 | 359  |  |  |  |

| C   | scc                          | Charts iMURD                         | 371  |  |  |  |

| D   | D Extended SCCharts Features |                                      |      |  |  |  |

| Ri  | hlion                        | raphy                                | 387  |  |  |  |

|     | Ū                            | iapii,                               |      |  |  |  |

| Lis | sts                          |                                      | 413  |  |  |  |

## Chapter 1

# Introduction

Although few people are likely to build or even maintain a compiler for a major programming language, the reader can profitably apply the ideas and techniques discussed in this book to general software design.

— Compilers – Principles, Techniques, and Tools

Some might see the aforementioned book from Aho, Sethi and Ullman [ASU86] as the bible of compiler construction. Even so the general statement of the quote remains untouched as many ideas and techniques are great additions to the repertoire of a software engineer, modern tools kits make it increasingly easier to create compilers for various areas of interest. Especially Domain-Specific Languages (DSLs) profit from this development. However, designing, understanding and maintaining these complex programs are different stories. Modern general purpose language compilers for example perform a lot of analyses and optimizations. Although the user has some degree of control over the compilation, compilers are usually black boxes or even a combination of these. Therefore, it is relatively hard to grasp beforehand how the final result of such a compilation chain will look like. It might be even harder to predict intermediate results which in addition are not necessarily executable models or comprehensible in a human-readable way. Maybe, it is not without reason that the infamous book is unofficially dubbed The Dragon Book.

```

int rec_sum(int* arr, int size) {

1 rec sum:

if (size == 0) {

2 .1 FB0:

3

return 0;

pushl

%ebp

} else {

4

mov1

%esp, %ebp

return arr[0] + rec sum(arr +

pushl

%ebx

1, size - 1);

$20, %esp

subl

$0, 12(%ebp)

cmp1

7 }

ine .L2

mov1

$0, %eax

(a) sum rec function in C

imp .L3

11 .L2:

1 .LFB0:

8(%ebp), %eax

mov1

%ebx

2

pushl

mov1

(%eax), %ebx

13

12(%esp), %edx

mov1

mov1

12(%ebp), %eax

14

%eax, %eax

4

xorl

-1(%eax), %edx

leal

15

8(%esp), %ecx

mov1

mov1

8(%ebp), %eax

16

%edx, %edx

testl

addl

$4, %eax

17

je .L2

mov1

%edx, 4(%esp)

18

8 .L3:

mov1

%eax, (%esp)

mov1

(%ecx), %ebx

call

rec sum

20

$4. %ecx

addl

10

%ebx, %eax

addl

21

%ebx, %eax

addl

11

22 .13:

$1, %edx

subl

12

$20, %esp

addl

13

ine .L3

%ebx

popl

24

14 .L2:

popl

%ebp

popl

%ebx

15

ret

26

ret

```

- (b) Generated assembler code of sum\_rec with O2 optimization setting

- (c) Generated assembler code of sum\_rec with O0 optimization setting

**Listing 1.0.1.** Classical results of different compilation optimizations

An example of a classical compiler optimization can be seen in Listing 1.0.1. Listing 1.0.1a shows a C program that calculates the sum of a given array recursively. When compiling this code with a traditional compiler, such as the GCC<sup>1</sup>, the user can usually choose between different levels of optimizations. In the example, Listing 1.0.1c shows an intermediate result of the compilation with no optimization whereas Listing 1.0.1b depicts a optimization level of two (-O2). The intermediate results are assembler codes and readable for a programmer trained in assembler. However, they

<sup>&</sup>lt;sup>1</sup>https://gcc.gnu.org/

(a) A small C program (b) Code excerpt of intermediate representation from the GCC, genexcerpt for illustrating erated with the -fdump-tree-ssa option. intermediate representations

**Listing 1.0.2.** Illustration of intermediate compilation result in the GCC (from [SSH18d])

are no longer in the source language and there is no information on how these assembler snippets were created. Even for a trained developer, understanding large pieces of assembler becomes difficult. Moreover, intermediate optimization steps may not be obtained; at least not in a human-readable form. Also, -O2 itself is an abstract level which does indicate the kind of optimization (although choosing different distinct optimizations is of course possible with the GCC). Without a look into the documentation, it simply states *optimize a lot*.

Nonetheless, the optimization is salient. Without going into the details of assembler, one can see the recursive call of the sum\_rec function in the unoptimized variant in Listing 1.0.1c in Line 20. Besides only needing 16 lines of code instead of 26, the optimized version in Listing 1.0.1c also does not include the call. The optimization completely resolved the recursion. It would be fantastic to see these optimizations instantaneously in a comprehensible way step by step.

As a second example, Listing 1.0.2 illustrates an intermediate representation of the C compilation of the GCC. In compiler construction, a program commonly gets divided in Basic Blocks (BBs). Basically, a BB represents an atomic sequence of program instructions without any branches [All70]. The partitioning of programs in their basic blocks usually makes subsequent

analyses of compilers more efficient. Listing 1.0.2a shows an excerpt of an C program. It first sets a variable x to 3. Then, x is tested and if greater than zero, the assigned value gets multiplied by 7. In the end, variable y is set to x multiplied by 2. When compiled with the GCC, the excerpt gets partitioned into its BBs, which we consider as an Intermediate Representation (IR) of the overall compilation. Using the GCC, the user can look at this result with the -fdump-tree-ssa command line option. The tree is shown in textual form as depicted in Listing 1.0.2b. Without going into too much detail, one can see different incarnations of the variables x and y and goto instructions to BBs, represented by the angle brackets and the bb identifier. While the information of the IR is present, the presentation and possibilities to navigate inside this intermediate result could be improved.

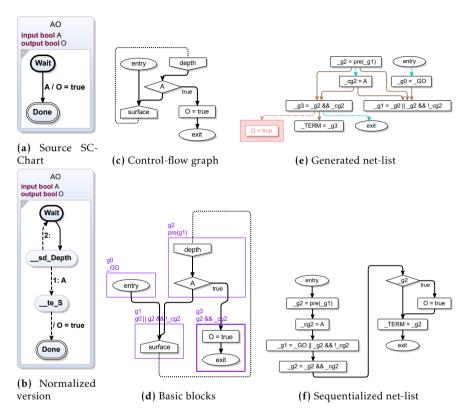

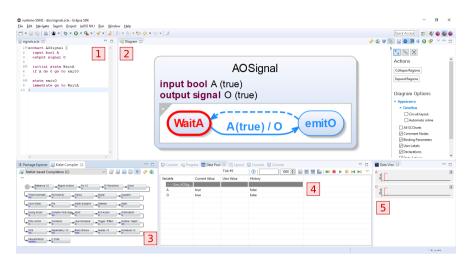

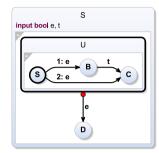

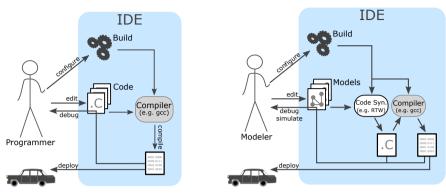

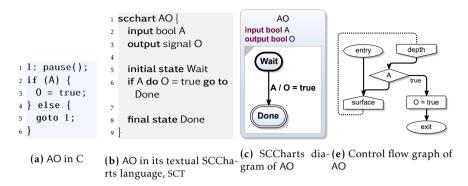

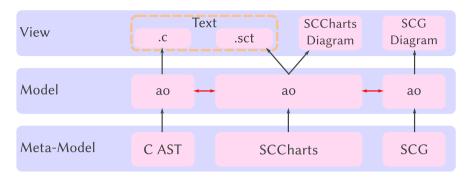

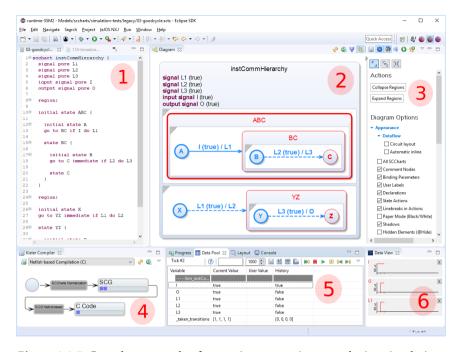

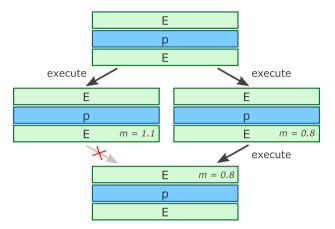

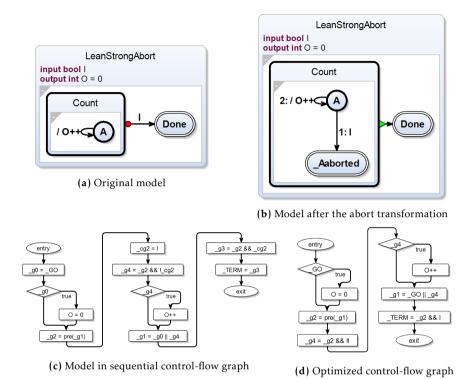

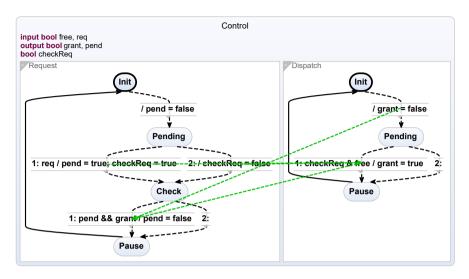

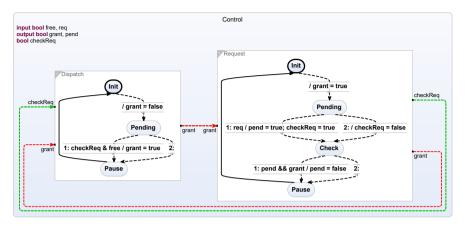

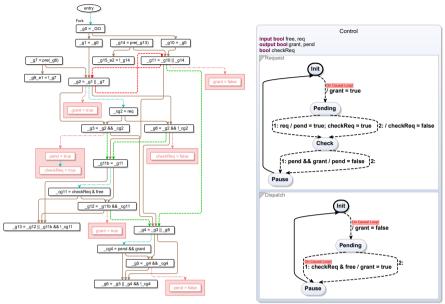

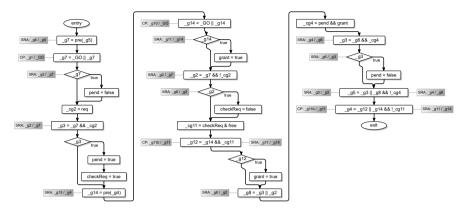

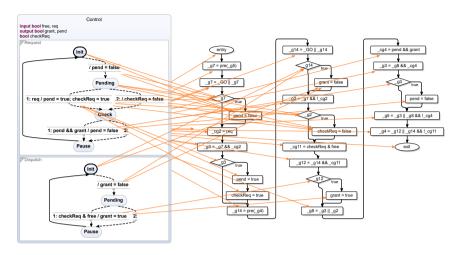

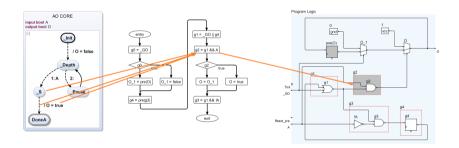

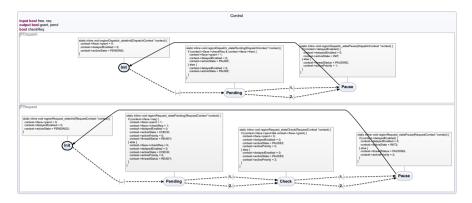

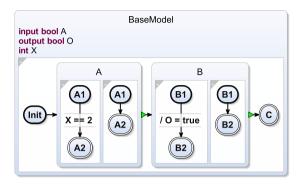

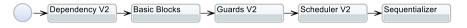

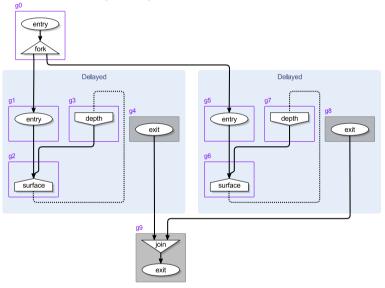

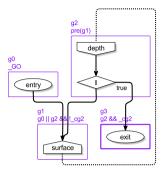

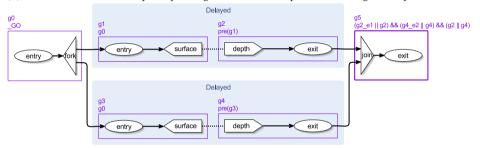

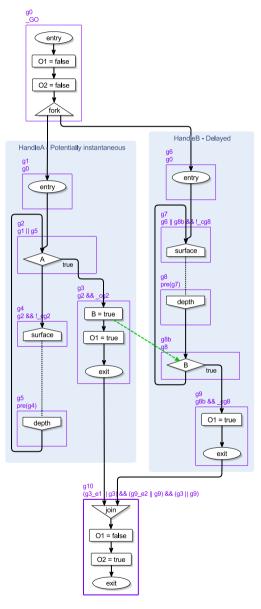

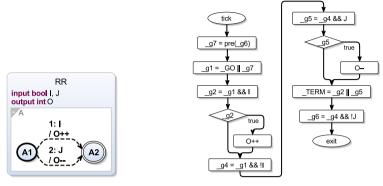

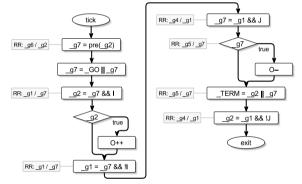

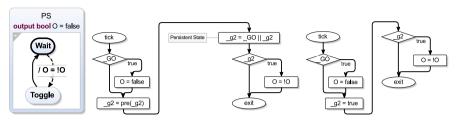

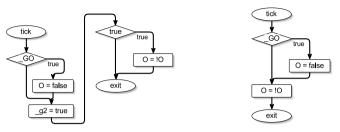

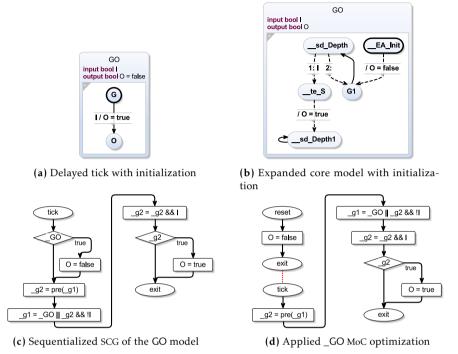

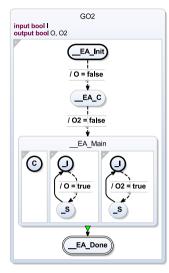

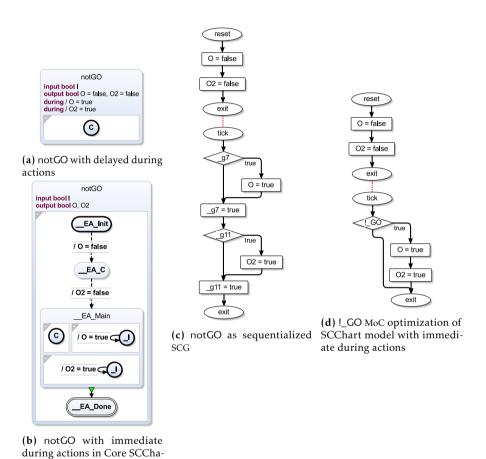

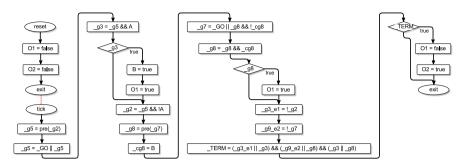

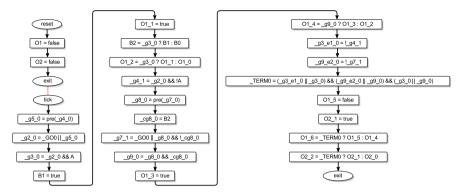

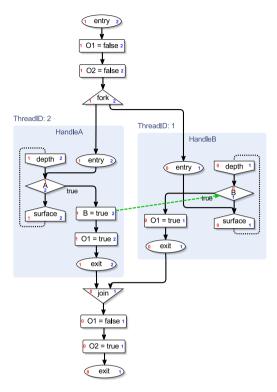

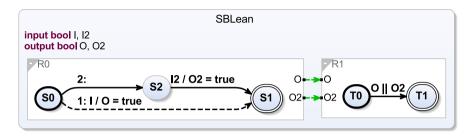

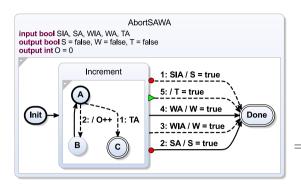

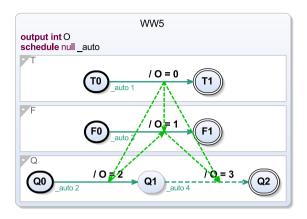

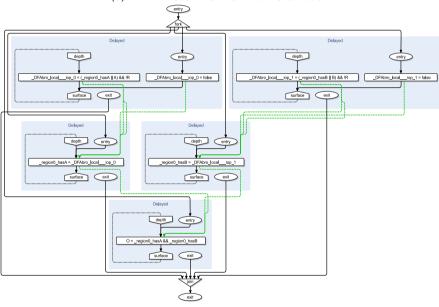

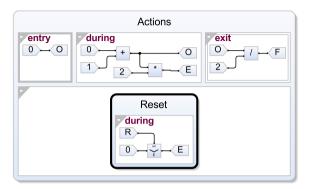

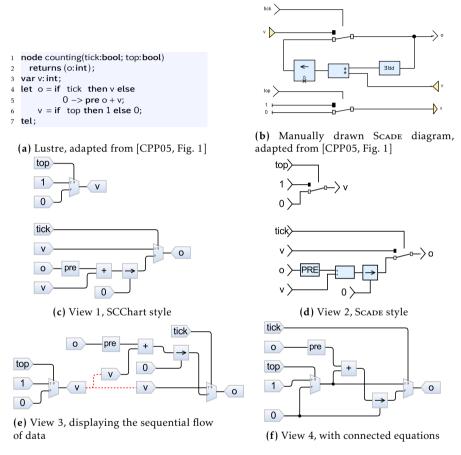

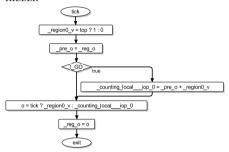

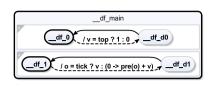

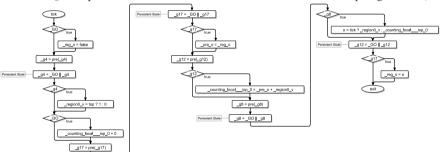

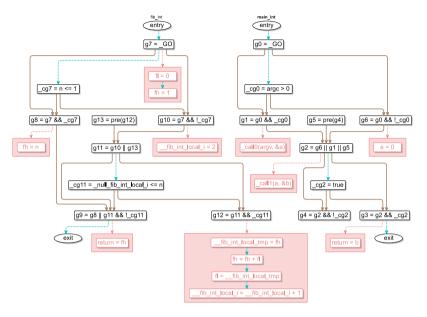

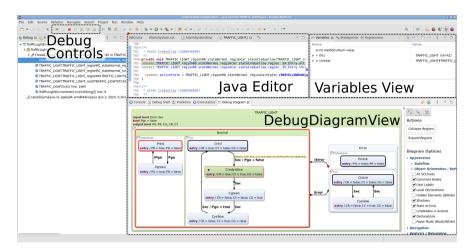

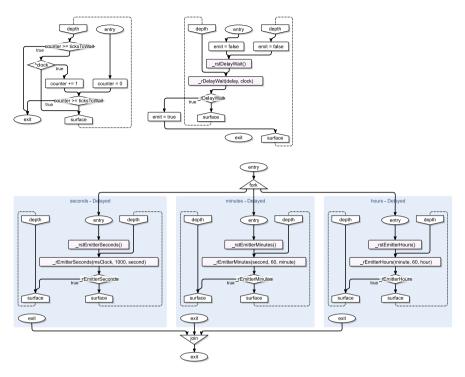

Figure 1.0.1 shows an excerpt of the compilation of an SCChart model within the KIELER tool, which will both be discussed in the following sections. The program waits for an input A to occur and then emits an output O before terminating. Figure 1.0.1a – Figure 1.0.1f show some of the intermediate steps of the compilation, each in an IR fitting for the *abstract syntax*. Figure 1.0.1b uses the same abstract syntax, or *metamodel*, as the source model, whereas Figure 1.0.1c – Figure 1.0.1f use a different one. Even without previous knowledge of compiler construction, a user can spot relationships between the individual IRs, which facilitates the overall understanding on how the steps are connected and lead to the final result.

This thesis presents a methodical approach for these interactive compilation models and exemplifies their use and usefulness with the help of the synchronous language SCCharts, as the IRs of visual languages facilitates the modeller's understanding of the overall workflow and single steps. The approach, however, is not restricted to visual languages or a single language.

**Figure 1.0.1.** Model-driven software development example with interactive compilation from the KIELER SCCharts project: In this example, a) a minimal SCCharts program AO gets compiled. The modeler can inspect every aspect of the compilation as every intermediate result is itself a model that can be visualized instantaneously and in a comprehensible way. This example compilation proceeds along the depicted figures: b) normalization, c) control flow graph creation, d) basic block analysis, e) net-list generation, and f) sequentialization. Each step is explained in detail in Part II of this thesis.

## 1.1 Contributions

The contributions of this thesis are divided into two parts. My relevant publications and supervised theses are cited within the enumeration. Closely related work follows afterwards. A comprehensive list of all publications and supervised theses is given in Appendix A. More related work follows in Chapter 2. In Part I,

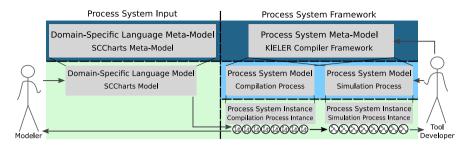

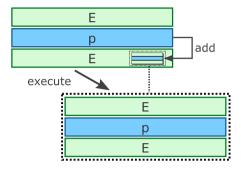

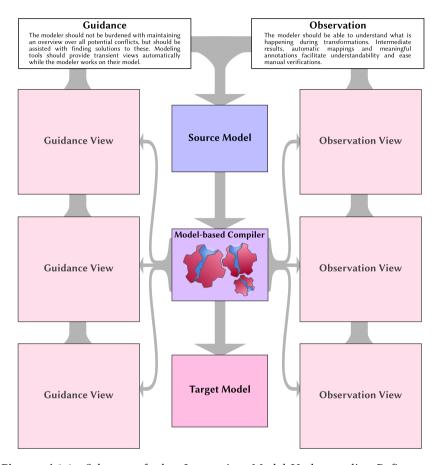

- 1. Chapter 3 presents, a new methodology of **interactive model-based compilation**. The concept builds upon the previously established Single-Pass Language-driven Incremental Compilation (SLIC) approach and enables a developer to define complete compilation processes interactively [SSH18c]. It systematically establishes a notion for model-based compilation systems. These compilation systems are formed by loosely coupled modular model processor to enable arbitrary tasks, such as compilation, simulation and deployment. They are full models themselves and are mutable just as the models they work on during their lifetime.

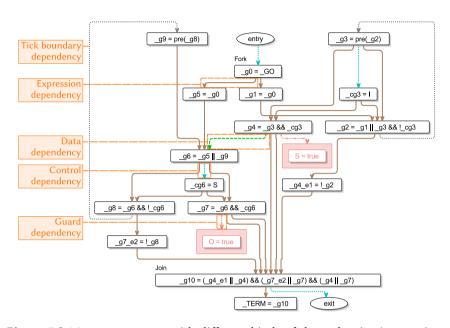

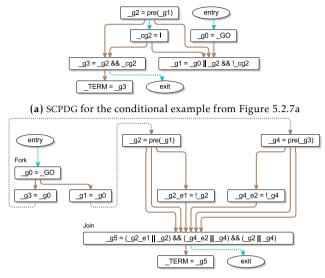

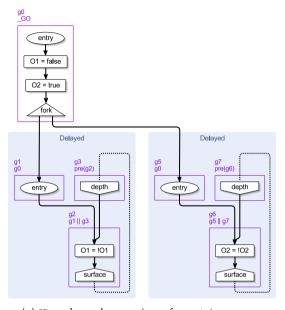

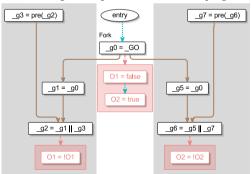

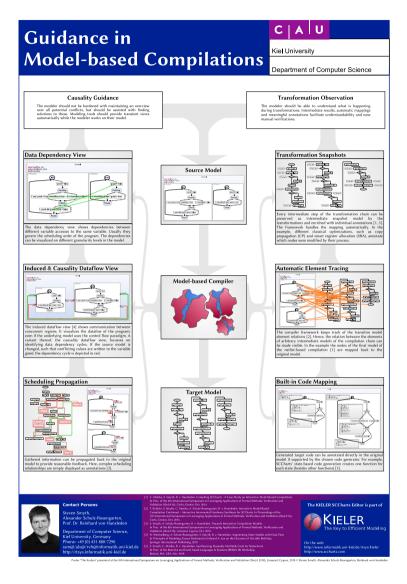

- 2. Building upon the interactive model-based compilation process, I propose a modeller-driven development process in Chapter 4. This results in a refinement feedback loop which supports the modeller in their work, which I will refer to as Interactive Model-Understanding-Refinement-Documentation feedback loop (iMURD) loop [SSH18a]. I investigate unaugmented and augmented model representations, which guide the modeller during the interactive model-based development process. While the concept is not restricted to any particular views, I present six practical examples from the KIELER open-source project, namely, data dependencies, causal dataflow, scheduling propagation, transformation snapshots, automatic element tracing and built-in code mapping. Tool developers can use similar dedicated views to get an overview of the complete compiler infrastructure and universe.

The concepts proposed in Part I are implemented as generic compiler infrastructure, the KiCo. KiCo's highly modular nature turns the infrastructure into a *meta-tool engine*, which allows arbitrary languages to utilize already established compilation chains.

Part II contributes in the practical domain:

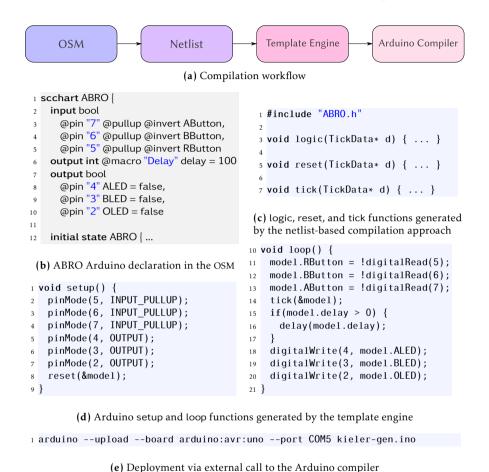

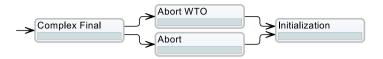

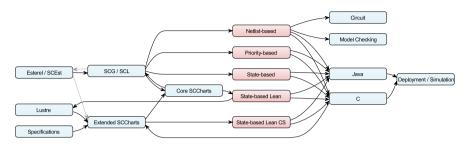

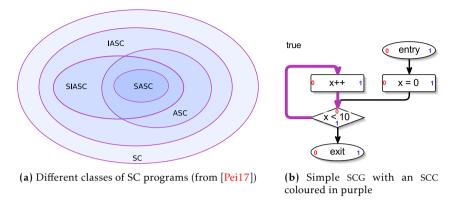

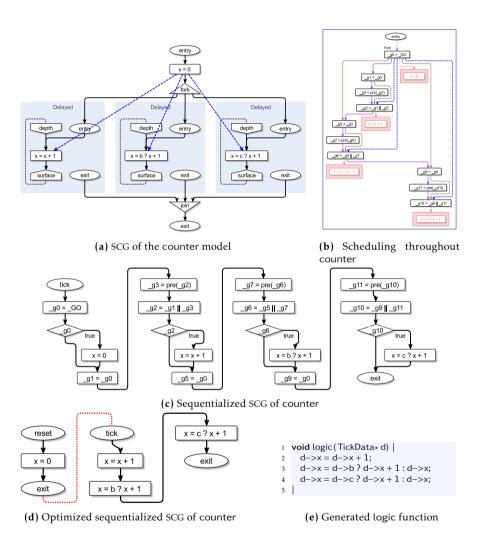

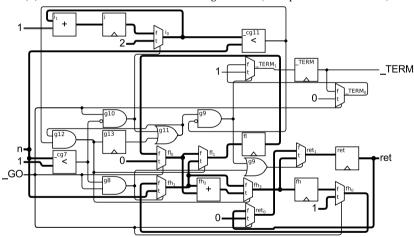

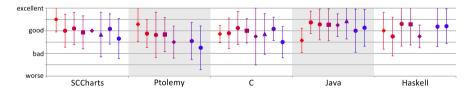

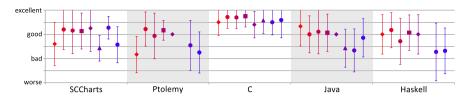

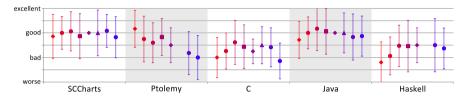

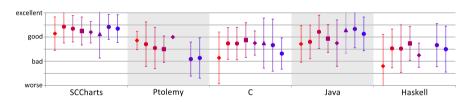

- 3. I illustrate three different low-level compilation approaches for the synchronous language SCCharts to demonstrate the capabilities of the interactive model-based compilation concept in Chapter 5. The netlistbased compilation creates code for software and hardware [SMH15; RSM+16; SLH16][Wei15; Bus16]. While many compilation steps are based on standard compilation techniques, the interactive model-based approach makes a comprehensible observation of all IRs possible. Here, optimizations and synchronous peculiarities, such as schizophrenia, are also addressed [SSH18d][Bus16]. The priority-based compilation approach [Pei17] does not synthesize hardware but scales better w.r.t. to model-size. The **state-based compilation** approach, coming in three variants, facilitates understandability and readability [SMH18; SDH19]. All approaches are evaluated against each other in terms of execution times and user experience. Since capabilities of a language and readability and simplicity are often a question of balance, I formulate ten language requirements which help decision makers in designing similar languages.

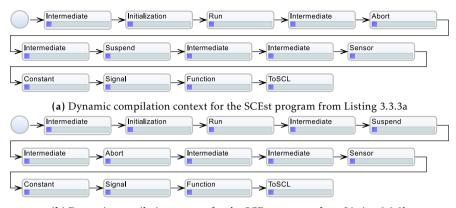

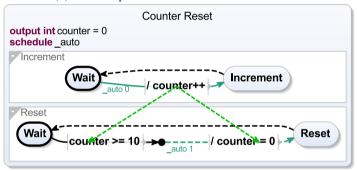

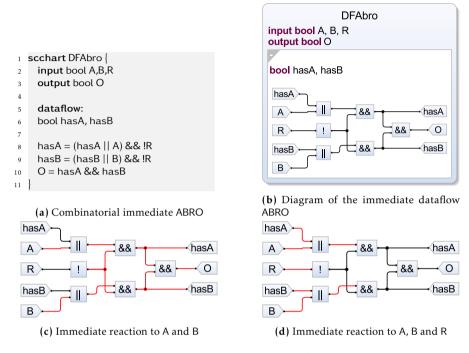

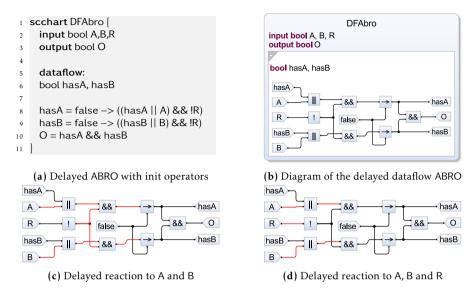

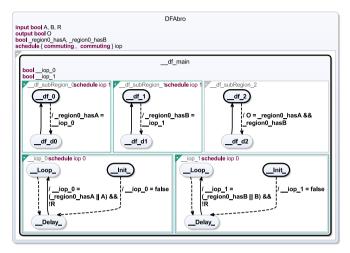

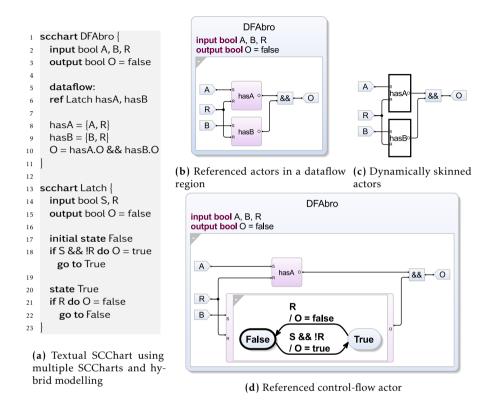

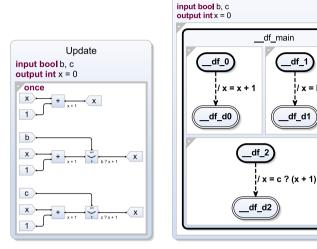

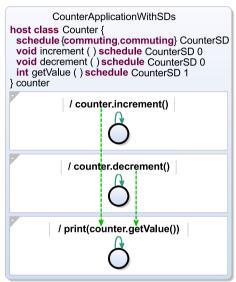

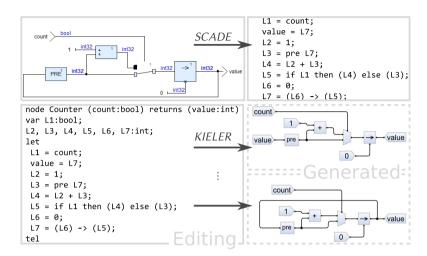

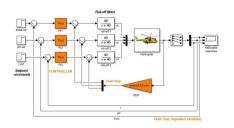

- 4. Chapter 6 presents how the concepts from Part I also facilitate the rapid development of various extensions to the SCCharts language and its underlying Model of Computation (MoC). Specifically, I present novel Scheduling Directives (SDs) as a first class citizen of synchronous languages which directly influence the scheduling of the used MoC [SSH19; SSH18b]. Furthermore, a dataflow extension is added to SCCharts, as control-flow-oriented language example, which allows dataflow and control-flow regions to co-exist in the sequential constructive world of SCCharts [GSS+20; SSS+19; MS15][Uml15]. The Sequentially Constructive Model of Computation (SCMoC) is implemented into the Esterel language using the interactive model-based compilation approach forming a new language dialect, SCEst [SMR+17; RSM+15][Rat15; Rah17]. Further, I show how the interactive model-based approach can be used to turn legacy general purpose languages automatically into comprehensible models that already have a working and tested compilation chain [SLH16][Ols16; Len16; And19]. The SCCharts language and the KiCo tooling are evaluated thoroughly through experimental data and surveys which were gathered during the span of more than five years [SMS+15; MSS+16; SMS+19a].

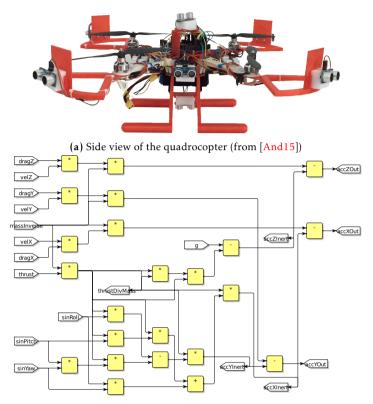

5. To demonstrate further possibilities of the presented approach, I present several **practical applications** in Chapter 7, namely *transient statecharts* from specifications verified by model checking [Sta19], a real-life cyberphysical pacemaker system [PRS+17b; PRS+17a] and applications in teaching, such as Lego Mindstorms [SMS+19a] and student projects involving a railway installation [SMS+15][Eum17], a quadrocopter [Pei15; And15; Mac15] and the Formula Student [SSS+19].

Closely Related Work 1) and 2) are closely related to general purpose compiler infrastructures, such as LLVM [Lat02], which serve as modular frameworks for arbitrary compilers by providing IRs and strictly separate language front-ends from the compiler back-end. The concepts presented here, however, stay as long as possible in the meta-model of the developer to present intermediate compilation steps in a comprehensible way. This facilitates understanding and results in a refined modelling process.

The approach presented here is a generic refinement of the work done w.r.t. SLIC by Motika [Mot17]. SLIC is specifically tailored to the features to the language in question. *Produces* and *can-not-handle* dependencies define the order of model-to-model transformations invocations. The interactive model-based compilation approach creates a generic framework for models, transformations and meters, which influence and evaluate model-based transformation chains. In fact, the approach presented here can be used to re-define and re-implement the previous SLIC approach generically, as demonstrated in Section 3.4.

A closely related modelling process is provided by *meta-tool generators*, such as Cinco [NLK+18]. Cinco is designed for domain experts and can be used to create highly customized Visual Domain-Specific Languages (VDSLs) on demand. While the concept targets a different meta level in creating self-sustained modelling tools, a paramount goal of both concepts is simplicity. They differ in the fact that the interactive model-based compilation approach is not a concept for a generator but for an engine that drives domain-specific requirements.

The processor categorization, orchestration and compilation universe presented in thesis are related to ETI's concept of loose coupling of services [SMB97]. ETI differentiates between two communities, the tool builders and users, to increase simplicity for the latter. The approach presented here goes one step further in creating a feedback loop that facilitates the development process by interactively providing the modeller with comprehensible compilation information. In turn, the tool developer can also profit from the process since the same information is used to refine the underlying transformations.

The graphical syntax and, therefore, the ways of presenting information in this thesis is similar to other modelling tools and Statechart [Har87; Dou99] dialects in general, particularly SyncCharts [And96b] in the case of SCCharts. The diagrams are extended by new information, such as dependency or scheduling information. To display these diagrams interactively in IRs, automatic layout [Fuh11; Rüe18; Sch19] and transient view technologies [SSH13] are used.

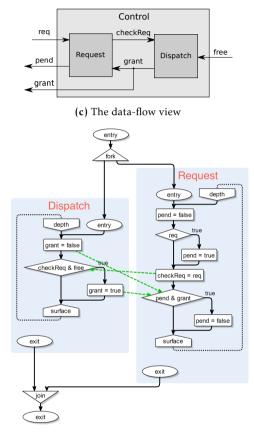

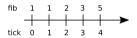

The compilation approaches in 3) use several well-established compilation techniques, such as the Program Dependency Graph (PDG) [FOW87] and copy propagation [ASU86]. They use common statecharts generation patterns [PM03; Sam02]. However, they are adapted to the interactive model-based compilation approach to facilitate understandability. Although possible, the goal is not to reach the most efficient code quickly but to provide the modeller with information about what is happening. The code generations and extensions 4) for synchronous languages are based on established procedures w.r.t. the peculiarities of synchronous MoCs, such as synchronizers and schizophrenia [PEB07; EZ07]. Here, understandability is also the goal in this thesis. Especially the presented state-based approaches are designed for readability and tailored to the topology of SCCharts and statechart dialects in general.

**Outline** Chapter 2 introduces the primary example language, SCCharts and its underlying MoC. It follows with detailed related work and related modelling tools. The chapter further includes the complete lists of publications and supervised theses.

The remainder of this thesis is structured according to the list of contributions. In Part I, Chapter 3 gives a motivation for the interactive model-based compilation approach and explains it in detail. The iMURD methodology and

details on the framework usability from the perspectives of a tool developer and of a modeller are discussed in Chapter 4. In Part II, the methodology established in Part I is used to create the reference compiler for SCCharts implemented in the KIELER SCCharts tools. While SCCharts serve as primary example in Chapter 5, the concepts can be applied to any statechart variation or even completely distinct languages. Chapter 6 explains additions to the SCMoC. Practical use-cases, which have been successfully developed using the technologies presented in this thesis, are demonstrated in Chapter 7. I conclude and give ideas for future work in Chapter 8.

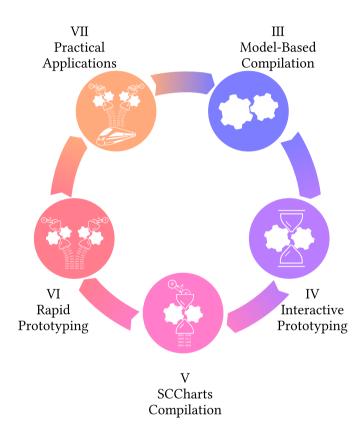

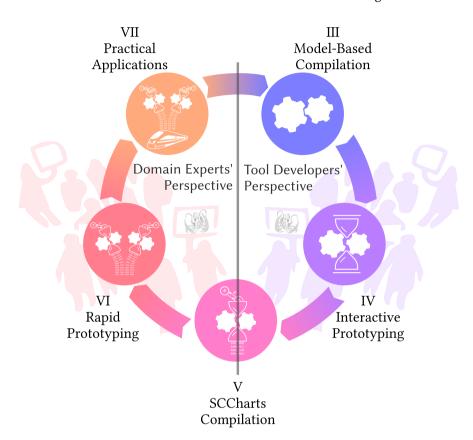

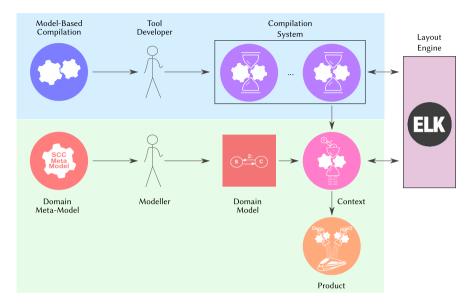

On a higher abstraction level, the relationships between the contents of the different chapters form another refinement cycle, which is illustrated in Figure 1.1.1. Tool developers use the concepts presented in Chapter 3. Following iMURD, they can refine and document prototypes, Chapter 4, until a satisfactory result is achieved. These are used in production, Chapter 5, to create whole compilation universes, e.g. for statechart dialects. The generated meta-tool engine can be extended to the actual needs of the domain experts, Chapter 6. Practical applications, Chapter 7, give new insights on the current workflow, which can then be adjusted to increase efficiency. The lessons learned can be used to iteratively improve the transformations that drive the used meta-tool engine.

## 1.1. Contributions

Figure 1.1.1. Outline of the development ecosystem

# **Preliminaries**

Antoine de Saint-Exupéry, the French writer and aircraft designer, said that

"A designer knows he has arrived at perfection

not when there is no longer anything to add,

but when there is no longer anything to take away".

More programmers should judge their work by this criterion.

Simple programs are usually more reliable, secure, robust and efficient

than their complex cousins, and easier to build and maintain.

— Programming Pearls

This chapter introduces preliminaries about SCCharts, the primary example language, and synchronous languages in Section 2.1. Section 2.2 presents the open-source project KIELER, which comprises the reference implementations of the interactive model-based compiler infrastructure and SCCharts. Section 2.3 discusses further related work and modelling tools in detail.

## 2.1 SCCharts

SCCharts is a synchronous language developed for safety-critical applications [HDM+14]. Chronologically, it can be seen as a successors of Sync-Charts [And95], which will be discussed further in Section 2.3.5, because SCCharts conservatively extends its MoC. This means that every SyncCharts program is also valid in SCCharts. However, the SCCharts SCMoC also includes sequentiality and, hence, accepts a broader class of programs. Sync-Charts, using the statecharts formalism proposed by Harel [Har87], can

#### 2. Preliminaries

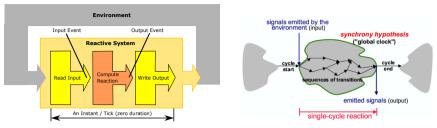

(a) Typical schematic of an embedded, reactive (b) Macro and micro ticks in synchronous lansystem encapsulated in its surrounding enviguages (G. Luettgen, 2001) ronment [MHH13]

Figure 2.1.1. Reactions in synchronous languages

be seen as a graphical form of Esterel [BC84], one of the most prominent synchronous languages.

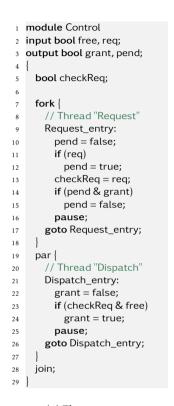

## 2.1.1 Synchronous Languages

Deterministic behaviour becomes difficult when in comes to concurrency. In traditional programming languages, concurrent execution is prone to *race conditions* [Lee06]. Synchronous languages are designed to ensure determinism [BCE+03]. Due to their predictability, synchronous languages are well-suited to model reactive and safety-critical systems. Figure 2.1.1a depicts a typical schematic of an embedded, reactive system. A reactive system constantly reacts to stimuli from its surrounding environment, also known as *inputs*. The system then computes a reaction and sends the *outputs*, e. g. some actuator control, back to the environment. The environment specifies the pace of this cyclic execution, which continues potentially indefinitely.

The classical synchronous MoC states that time is divided in discrete chunks, called *instants* or *macro ticks*. They are often also simply referred to as *ticks*. A macro tick, as depicted in Figure 2.1.1b, represents one reaction of the system, including reading inputs, computation, and writing the outputs. While a macro tick may consist of finitely many single calculations, *micro ticks*, the overall tick is considered to consume no time. Hence, the outputs are generated at the same time when the inputs are read. This is also

known as the synchrony hypothesis and is generally used in all synchronous languages. Esterel, Lustre, and Signal are prominent representatives of these languages.

Such languages use signals to communicate with their environment and also across concurrent regions of a program. Because a tick represents a discrete point of time, signals traditionally must have a coherent status within the same tick. The signal coherence law states that within a tick a signal can only be absent or present but not both at the same time. A signal S is absent by default and only present in a tick if and only if S is emitted in this tick.

```

1 if (!x) {

2 // do something

x = true:

4 }

```

Listing 2.1.1. **Typical** sequential programming pattern forbidden in classical synchronous languages: set flag x to true after some work has been done.

Depending on the concrete semantics, this law sometimes varies slightly, but the consequence for classical synchronous languages is overarching: A signal must have a unique state within a tick. Hence, deterministic behaviour and predictability come at a price. The class of programs that are considered valid, or constructive, is restricted, because even classical sequential programming pattern, as depicted in Listing 2.1.1, are forbidden.

Here, a boolean variable x is checked. If its value is false, a specific task Example should be executed. Afterwards, x is set to true to indicate the completion of the task. If x were a synchronous signal, this program would not be constructive, because x would not have a coherent status as it would be false and true within the same tick.

The SCMoC relaxes this restriction. Instead of using signals which are uniquely defined per tick, the SCMoC directly uses variables which can change their values in every micro tick. All non-concurrent variable access are scheduled in sequential order. Hence, deterministic behaviour and predictability remain untouched while enabling the modeller to create programs that use well-known imperative programming patterns. It is a conservative extension to the classical synchronous MoC. Every program that is constructive under the classical MoC is also valid under the SCMoC.

## 2. Preliminaries

## 2.1.2 Core SCCharts

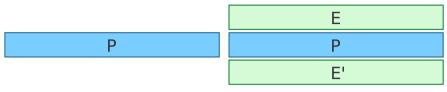

SCCharts is divided into two conceptional parts, *Core* and *Extended* SCCharts. Core SCCharts includes all essential language elements, while Extended SCCharts adds further features on top of Core SCCharts for the modeller's convenience. These features make it more convenient for a modeller to express certain functionality even though it is possible to express the same functionality with more basic features. These models often appear to be more compact because their complexity is hidden. However, all complex features must be translated into the *kernel language* which the compiler understands and uses to generate the output.

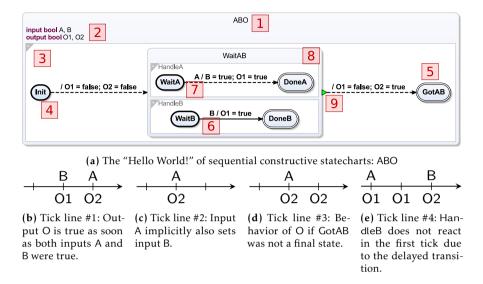

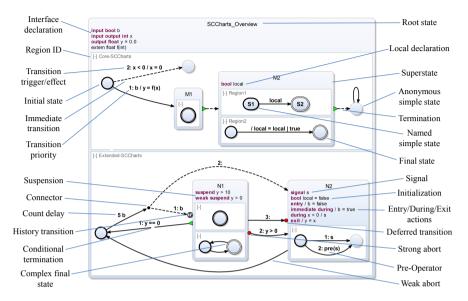

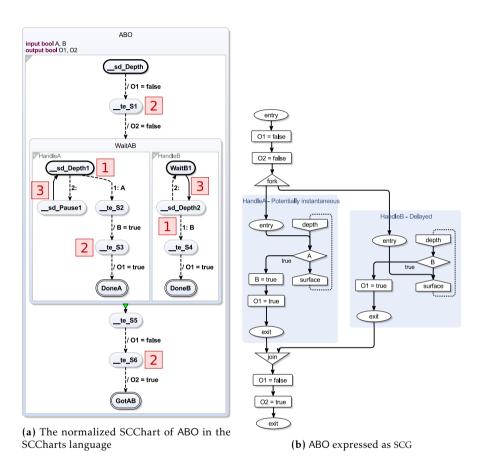

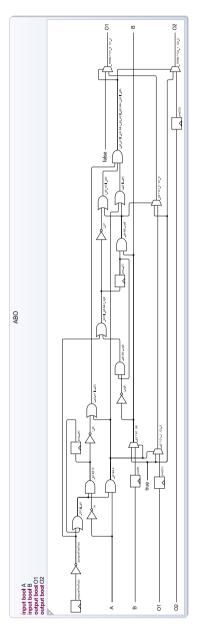

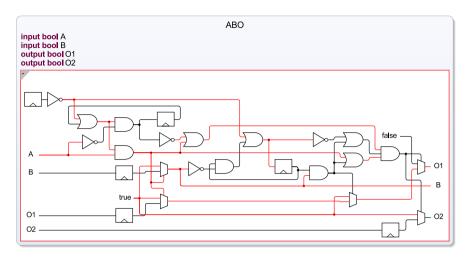

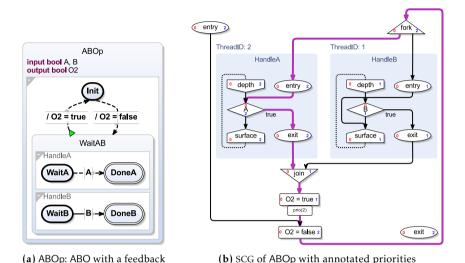

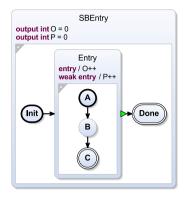

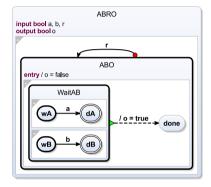

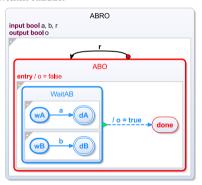

Example

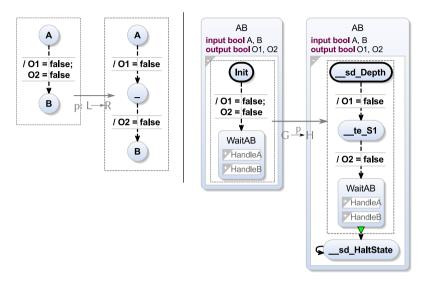

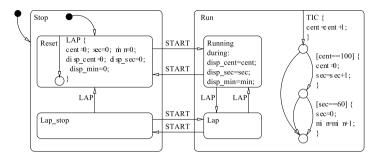

The essentials of SCCharts are exemplified in Figure 2.1.2a. The figure shows ABO, the Hello World! of sequential constructive statecharts. Every SCChart begins with a header area which contains the name of the chart in the middle 1 and an optional *declaration* part 2. This outermost structure is called the *root state*. The declaration part in Core SCCharts can include *input*, output, and local variables. Input and output variables in the declaration area of the chart form the *interface* of the program, because they specify the ways the program can communicate with its surrounding environment. Note that a program that does not specify an interface has no observable behaviour and is semantically equivalent to NULL (if side-effects are excluded). The chart further contains one or more regions that contain states and transitions between states 3. Regions are units of potentially concurrent control-flow and can be seen as threads. If active, they have their own control flow and run concurrently to other regions at the same nesting level. States are locations inside a region where the control of a region rests. They are connected via transitions, which are used to transfer control to another state. If a region becomes active, the control starts at the initial state of the region. It is visualized with a thick border 4. The region terminates, if a final state, displayed with a double-border 5, is reached. Every region must have exactly one initial state and can include arbitrarily many final states. A transitions connects a source state with a target state. A transition is taken, if its source state is active and the trigger of the transition evaluates to true. An omitted trigger implicitly states true. If multiple transitions exist, a transition priority determines in which order the transitions are checked.

**Figure 2.1.2.** Syntax and behaviour of the *Hello World!* of sequential constructive statecharts: ABO

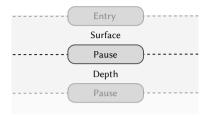

Only the first transition which is eligible to activate is considered. However, transitions have two different *delay types*, *delayed*, displayed as a solid edge **6**, and *immediate*, drawn dashed **7**. A delayed transition cannot activate, if its source state activated in the current tick. Hence, a delayed transition can only become active, if the state was already active at the start of this tick and has not been re-entered in the meantime. When a transition is activated, the control is transferred to the target state and optional effects can be executed. States can be *simple* states or *superstates* **8**. Besides marking a point in the control-flow of the region, a superstate also has inner behaviour. All regions inside the superstate are activated when the superstate itself becomes active. In Core SCCharts, a superstate is exited with a *termination* transition **9**, also known as *join*. A termination transition, visualized with a green triangle at the start of the transition, usually has no trigger. It immediately becomes active when all regions of the superstate have terminated. A superstate can also declare new local variables which are scoped hierarchically. The

## 2. Preliminaries

rootstate of the program is a superstate which declares inputs and outputs and which cannot have any outgoing transitions. The program terminates when the rootstate terminates.

When executed, the control of the program depicted in Figure 2.1.2a starts in the initial state of the root state ABO. It immediately traverses along the only outgoing transition to the superstate WaitAB, because the transition is immediate and the omitted default trigger is always true. Here, the two regions HandleA and HandleB wait for the input signals A and B concurrently. Each region contains an initial Wait state from which a transition points to a final done state. When the transition is taken, O1 is set to true. The transition in HandleA also sets B. After both regions reach their final state, WaitAB terminates and the termination transition is immediately active. Its action sets O1 to false and O2 to true. Once GotAB is reached, the program terminates.

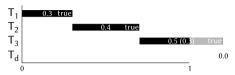

Figure 2.1.2b-Figure 2.1.2e show four example tick lines. Tick lines are a typical means in synchronous languages to illustrate the input/output behaviour of the program. Discrete ticks are marked on the axis. Inputs are written above the tick; outputs below. In Figure 2.1.2b the input B is true in the second tick. After A becomes true in the third tick, the program emits O2. In Figure 2.1.2c A is already present in the second tick. B is not true in the surrounding environment. However, when A becomes true, it also sets B to true as can be seen in HandleA. O2 is emitted in the second tick, but O1 is set to false again because of the termination, which is not permitted in classical synchronous MoCs. Since the program terminates as soon as O2 becomes true, there is no more behaviour after the second tick. This would be different if GotAB would not be a final state. Then, the control would rest in GotAB and since SCCharts use persistent variables for communication, the last variable configuration will remain indefinitely as depicted in Figure 2.1.2e. This does not hold for input variables though, as inputs are set by the environment in every tick. In Figure 2.1.2e, A is true in the first tick. This time, O2 stays false due to the delayed transition in HandleB. The transition is not active in the first tick and HandleB cannot terminate. Furthermore, B is an input and set from the environment in every tick. Hence, the B assignment from the first tick is lost. O2 is finally emitted after B becomes true again in tick \_ three.

#### Concurrent Scheduling 2.1.3

The previous two sections show that concurrency is an essential property of SCCharts and Statechart dialects in general. On the abstract modelling level of synchronous languages, concurrent executions of statements become interesting if they access the same variable in the same tick. It is easy to create concurrent programs that do not behave deterministically. Since deterministic behaviour is an intrinsic feature of all synchronous languages, clear scheduling rules must be established.

A variable can be accessed in two different ways. First, it can be written Definition to, which is referred to as a write access. Second, a variable can be read to retrieve a previously assigned value, which is considered a read access. Two variable accesses are *commuting* if the order in which they are executed does not matter. If all variable accesses inside a schedule for a concurrent context are commuting, the schedule becomes confluent.

For instance, two assignments which assign the same value to a vari- Example able are commuting because no matter in which order the assignments are executed the variable will still hold the same value.

Write accesses are further categorized in absolute writes and relative writes in SCCharts. Relative writes have the form x = f(x,e) where f is so that such assignments are commuting with each other and expression e does not depend on x, and where the evaluation of e does not have any side effects. All non-relative writes are absolute writes. To schedule different types of writes, the sequential constructive approach organizes non-confluent concurrent variable accesses under a strict Initialize-Update-Read Protocol (IURP). In a tick instance, concurrent absolute writes (initializations) must be executed first as long as they are confluent with each other. Secondly, all concurrent relative writes (updates) can run but must be scheduled after the absolute writes. Finally, all reads may proceed. Note that all non-concurrent access are scheduled sequentially and do not have to adhere to the IURP because there is no concurrency to resolve.

A program which contains concurrent non-commuting write accesses Conclusion in any tick of the execution is not schedulable under the IURP and must be rejected by the SCCharts compiler.

#### 2. Preliminaries

(a) The programs waits for input A and emits the signal O.

(b) The automatically generated Core SCCharts variant of the program shown in Figure 2.1.3a.

(d) Tick line for the same program with O being a boolean variable in the source model.

Figure 2.1.3. The Extended and Core SCCharts variants of AO with signals

## 2.1.4 Extended SCCharts

Extended SCCharts include features which can be expressed in Core SCCharts but provides more convenient ways for the modeller. It is also sometimes referred to as the *syntactic sugar* of SCCharts.

Example

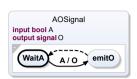

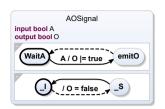

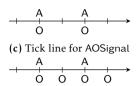

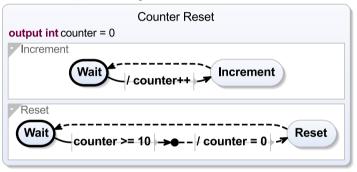

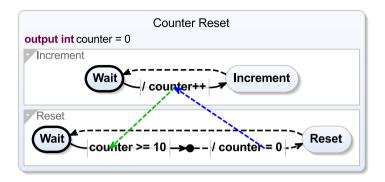

Figure 2.1.3 shows two variants of AO, presented in Figure 1.0.1, with signals, which are an extended feature in SCCharts. The first version in Figure 2.1.3a uses the extended SCCharts syntax. Output O can directly be declared as signal. Hence, O is only true in the ticks in which also A is true. Otherwise, O is set to false as can be seen in Figure 2.1.3c, because it is a signal. Figure 2.1.3d visualizes the behaviour of AOSignal if O in the source model would have been declared as standard boolean variable.

Eventually, the Extended SCChart is transformed into a semantically identical Core SCChart during compilation. The result for this particular extended feature is depicted in Figure 2.1.3b. One can see that the output O is now a boolean type. In every tick, O is explicitly set to false and the emit of O got transformed to a relative write assignment. As explained in Section 2.1.3, the IURP takes care of the concurrent scheduling and makes sure that the initialization happens before the relative write access.

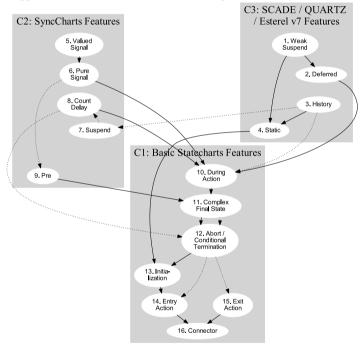

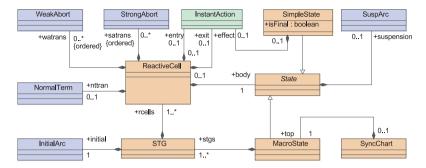

SCCharts does not reinvent the wheel when it comes to the features of synchronous languages. Many extended features are borrowed from related languages, such as Esterel [GR83], SyncCharts [And96b], SCADE [CPP17] and Quartz [Sch09]. The complete language overview is depicted in Fig-

Figure 2.1.4. SCCharts feature overview

ure 2.1.4. Since Motika [Mot17] gives a full overview over all common extended features and their transformations, they are not discussed in detail here. However, the meanings of the most common extended features, which are also used during this thesis, are briefly recapitulated:

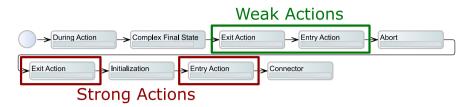

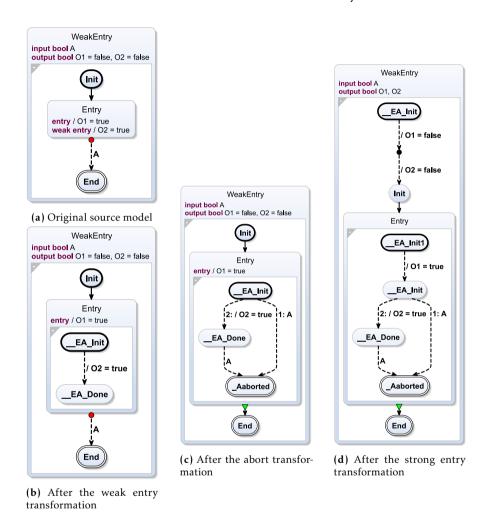

**Strong Abort** A strong abort preempts inner behaviour of a superstate. If a strong abort transition is taken, the inner behaviour of a superstate is not executed. Strong aborts are depicted with an red tail circle at the transition in the graphical syntax.

**Weak Abort** A weak abort grants a superstate its *last wish*. The superstate is allowed to finish its inner behaviour of the actual tick and is then preempted. Weak aborts do not have a tail decorator in the graphical syntax. Conclusively, a superstate transition can be a termination (green triangle), a strong abort (red circle), or a weak abort (no special decorator). Note that different preemption types are not reasonable on simple states, because the different types only differ in the handling

## 2. Preliminaries

- of the inner behaviour. Therefore, simple states should simply be left with unqualified transitions w.r.t. preemption. Syntactically, they are identical to weak aborts in SCCharts.

- **Entry Action** An entry action is executed immediately when the parent state is entered even if the state is immediately left again. The actions are executed in sequential order in which they appear before any internals continue.

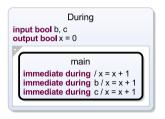

- **During Action** As long as the superstate is active, its during actions are executed. They all run concurrently.

- **Exit Action** An exit action is executed when the parent superstate is left. This includes preemption. Like entry action, exit actions are ordered.

- Complex Final State A complex final state is a final state that has inner behaviour or outgoing transitions. Hence, a complex final state can execute inner behaviour and can also be left before the parent superstates terminates. It contributes to the join such that the superstate terminates if the all other regions' control also rests in a final state but continues to operate otherwise.

- **Pre Operator** A pre operator can be used inside expressions. It retrieves the value of a variable of the preceding tick. Pre operators can be nested. Hence, pre(pre(x)) will return the value of x from two ticks ago.

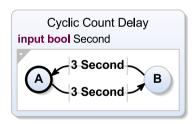

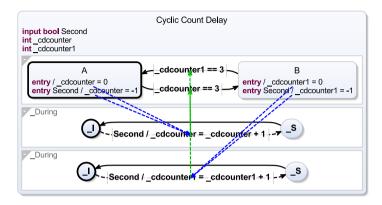

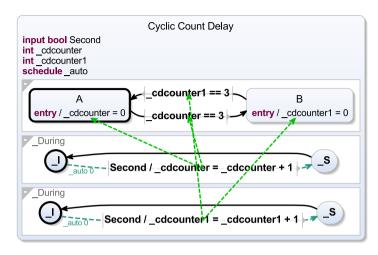

- **Count Delay** A preceding integer n in front of a transition or action trigger is called a count delay. It states that this trigger must happen n times before the transition, resp. action, enables.

The symmetrical handling of entry and exit actions [Mot17] is a break with the SyncCharts semantics, where entry actions are simply abbreviations of similar actions of incoming transitions which cannot be preempted by an aborting transition because the state has not been entered yet. Contrary, exit actions can be skipped by a preemption. However, adding two unambiguous new actions in Section 6.3 will solve this asymmetry and hence, bring the SCCharts semantics in line again with the semantics of SyncCharts.

Remark

A frequently asked question is if there is a difference between "SCCharts" and "SCChart" and when to use which. In general, when talking about SCCharts, the language SCCharts is meant as a whole. Consequently, if one talks about *the* or *an* SCChart, they usually refer to a single SCCharts model.

## 2.2 The KIELER SCCharts Modelling Tool

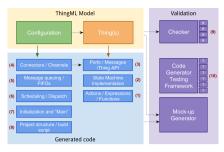

The Kiel Integrated Environment for Layout Eclipse Rich Client (KIELER) is an academic research project which is mainly divided into two parts, namely semantics and pragmatics. In this context, the semantics area covers modelling of programming languages and model-based compilation of these with a particular focus on synchronous languages and interactive compilation which are suited for safety-critical applications. The pragmatics teams deals with automatic layout, diagram synthesis and usability questions. Especially the development of layout and transient view frameworks, such as the Eclipse Layout Kernel (ELK) [Rüe18; Sch19] and KLighD [SSH13], are the main foci.

As of July 2020, over 100 committers with over 16000 commits alone in the semantics area of KIELER contributed to the project during its lifetime. The KIELER SCCharts Release 1.0 comprises 35 Eclipse plug-ins, which result in over 2.3M Lines of Code (LoC). However, due to an increasingly streamlined workflow, most of this code is auto-generated nowadays. In fact, only 200k – 300k LoC are written manually in Java or Xtend<sup>1</sup>. The implementation of the compiler infrastructure, which is discussed in Part I, is known as KIELER Compiler (KiCo).

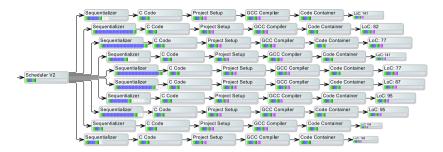

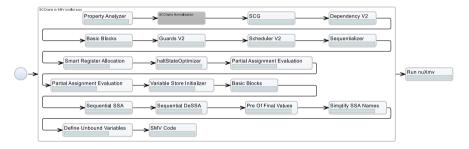

KiCo is used to realize the SCCharts reference compiler, which consists of over 80 dedicated compilation systems and 165 modular processing units that can be combined to form new compilation systems. The compiler is released as the KIELER SCCharts Editor. It enables a user to model, compile and simulate any SCCharts model.

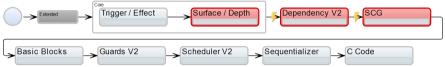

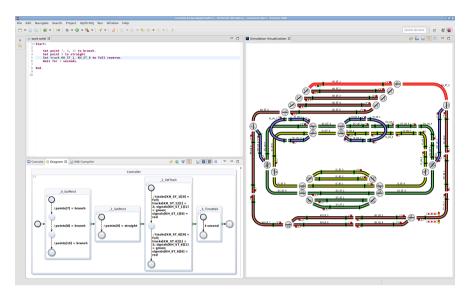

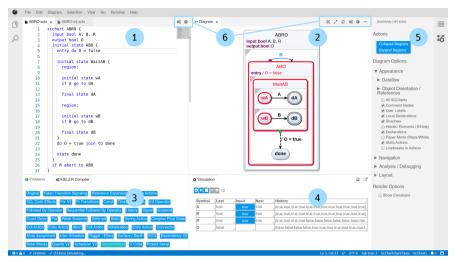

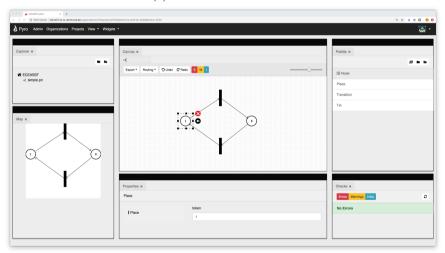

Figure 2.2.1 shows the default simulation perspective of the KIELER SC- Example Charts IDE. The editor is located on the left side 1. Here, the modeller can edit and save the source model. The modelled program is instantly visualized as layouted statemachine in the Diagram view in the middle 2. The process of instantly and automatically generated, layouted diagrams from source models is called *synthesis*. This area also highlights running simulations.

<sup>&</sup>lt;sup>1</sup>https://www.eclipse.org/xtend

## 2. Preliminaries

Figure 2.2.1. KIELER SCCharts Editor – Simulation perspective

Synthesis options, which are specialized for the currently active synthesis, can be modified on the left panel in this view. In the lower left area 3, the developer can inspect the actual compilation chain. Intermediate results can be selected and simulated like the source model. The lower middle view 4 hosts controls for the simulation such as value tables for the environment. Here, it is also possible to modify the pace of the simulation or issuing single discrete steps. All components that have been active in this tick are highlighted in light blue. States in which the control rests at the end of the tick are red. On the lower right 5, single values can be inspected. Their history is depicted as a graph appropriate for the corresponding data type.

Remark

It is noteworthy that while being the most complete implementation, the artefact is not a full implementation of all SCCharts possibilities which have been proposed. Additionally, it is an academic project to test and evaluate research. As time goes on, new features will be added and no longer maintained ones will perish. However, the individual release snapshots should remain of course.

#### 2.2. The KIELER SCCharts Modelling Tool

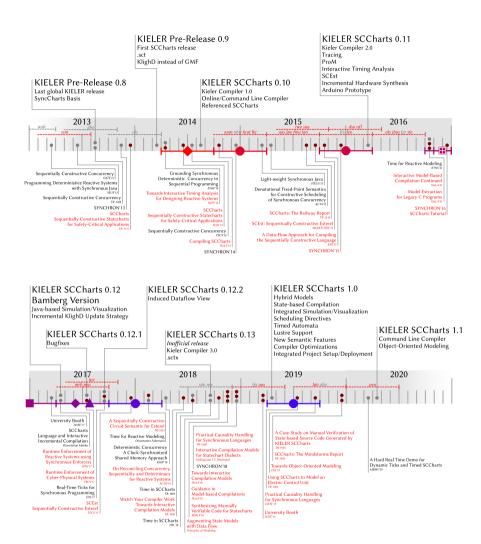

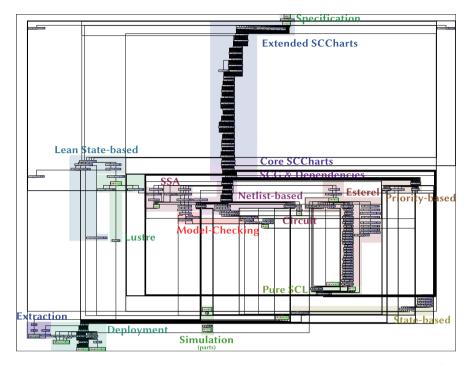

**Figure 2.2.2.** The KIELER SCCharts development timeline with releases on top, publications on the bottom side, theses inline and conducted surveys on the border. The author's involvement is marked in red.

An overview over the complete SCCharts project is depicted in Figure 2.2.2. The timeline shows the complete SCCharts development from 2013, in which year the last SyncCharts variant of KIELER was released, up until the 2020 with upcoming future releases. My involvement is marked in red. All major releases are shown on the top side of the timeline. They led to the version which was used mainly throughout this book, which is KIELER SCCharts 1.0. The publications related to SCCharts are shown on the bottom side. The theses that are related to the KIELER semantics area are depicted on the timeline and the conducted surveys are shown on the bottom border. A comprehensive list of all my publications and advised theses is listed in Appendix A.

### 2.3 Related Work

Previous work done by Motika and Fuhrmann is explained in Section 2.3.1. The subsequent sections will cover related topics towards compiler infrastructures, modelling tools, model-based compilation patterns and synchronous languages.

## 2.3.1 SLIC and Interactive Timing Analysis

This section discusses the results from Motika [Mot17] and separates them from the contributions of this thesis. There has also been joint work on the topic of Interactive Timing Analysis [Fuh17], which can be seen as a demonstrator for the pragmatic and interactive modelling approach.

Relevant ongoing related work towards SCCharts, e.g. research towards object-orientation in statecharts by Schulz-Rosengarten and sequential constructiveness in dataflow languages, such as Lustre, by Grimm, are also not part of this thesis but will be sketched out in future works in Section 8.2.

SCCharts—Language and Interactive Incremental Compilation Motika finished his PhD thesis [Mot17] in 2017 and was the former team leader of the KIELER semantics team and the mentor of this thesis' author. As his list of major publications shows [Mot17, p. 10 ff.], he heavily contributed towards

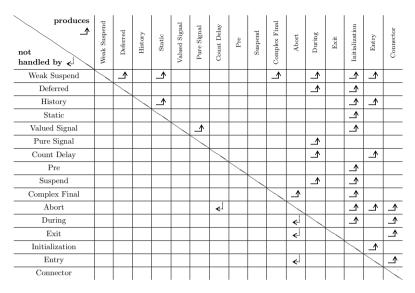

the design and high-level compilation of SCCharts. This section clearly differentiates the contributions of this thesis to the work done previously. Motika presented first steps of an interactive and incremental compilation approach named Single-Pass Language-driven Incremental Compilation (SLIC). It is a model-based compilation approach which consists out of a series of Model-to-Model Transformations (M2MTs) [MSH14] and is defined by the four letters that form the acronym.

- 1) **Single-Pass** Each transformation in a SLIC schedule is only executed once. Cyclic dependencies between transformations are forbidden.

- 2) Language-Driven The transformation invocation order depends on the features of the particular language. They form a dependency graph that describes which transformation *produces* other features and which transformation *cannot handle* other features of the language. Hence, transformations in the SLIC approach are categorized in *produced* and *not-handled-by* transformations. Obeying the first rule 1) of SLIC, the dependencies must form an acyclic graph and there might be more than one valid graph for a specific compilation target.

- 3) Incremental In the case of SLIC and due to its model-driven nature, incremental means that every feature of a language gets transformed each by each. Consequently, it is expected that a transformation resolves a specific language feature and that this feature is no longer contained in the model after the transformation is finished.

- 4) Compilation SLIC is a compilation approach.

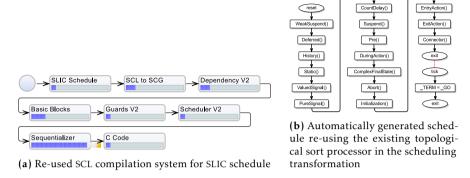

The SLIC approach was an inspiration for the interactive model-based approach presented in this thesis. Chronologically, the SLIC compiler is the predecessor of the KiCo approach. The KiCo development profited greatly from the lessons learned during the SLIC development. Today, KiCo is the predominant approach used in KIELER. Hence, the two main contributions from Motika are not part of this thesis. Particularly,

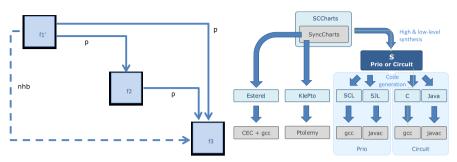

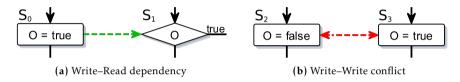

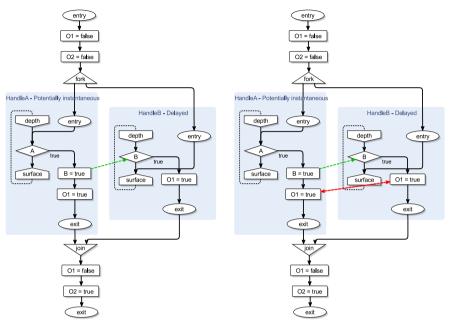

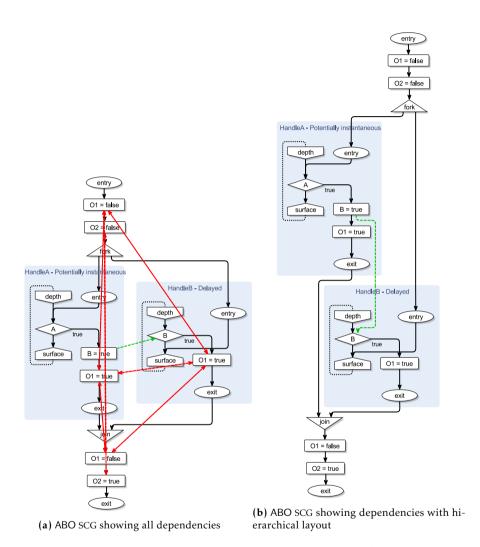

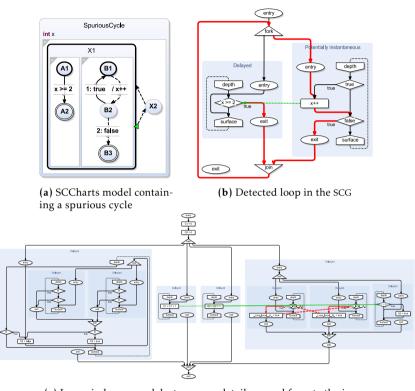

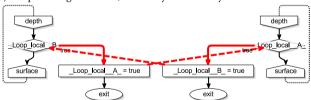

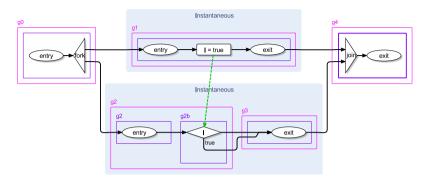

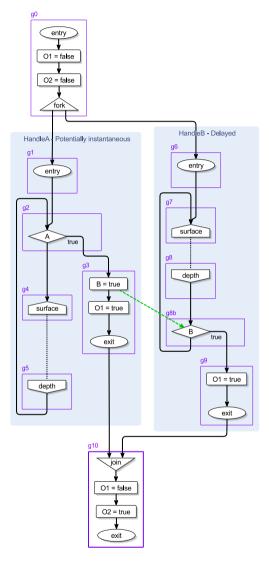

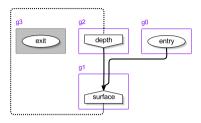

SLIC is specifically tailored to the features to the language in question.

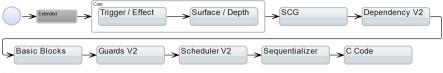

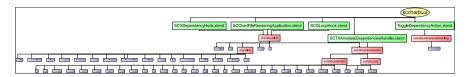

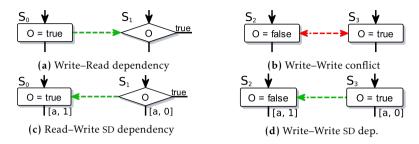

Produces and can-not-handle dependencies, depicted in Figure 2.3.1a,

determine in which order arbitrary model-to-model transformations are

executed. The SLIC dependencies between the transformations of the extended SCCharts features from Motika's work are shown in Figure 2.3.1c.

- (a) *Produces* and *not-handled-by* dependencies of the SLIC approach

- **(b)** Compilation steps of the previous SCCharts compilation

(c) SLIC dependencies between the SCCharts features

**Figure 2.3.1.** Previous work done regarding the compilation of SCCharts by Motika (from [Mot17])

The developer has limited influence on the compilation and depends on the correct implemented and configured transformations. Especially, SLIC rules 2) and 3) are tailored to SCCharts and similar languages. However, even within the SCCharts downstream compilation in the SCG, an intermediate control-flow representation for synchronous models, rules 2) and 3) are weakened because features are not really resolved but extended. The SLIC implementation in KIELER does not define or enforce any specifications on the transformations and will only return limited information about the compilation itself. At most times, simply the transformation result will be returned if the compilation was successful.

The interactive model-based compilation approach presented in this thesis takes a step back. It creates a generic framework for models, transformations and measures to define, influence and evaluate model-based transformation chains. In fact, the approach presented here can be used to re-define and re-implement the previous SLIC approach, which is demonstrated in Section 3.4. On the other side, it can also be seen as continuation of the previous work in making the former SLIC definition more generic and easy to use without restriction to already established features. It is not restricted to any language or underlying meta-model and easy to configure on a project-basis.

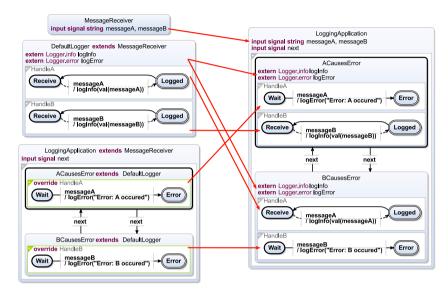

• The second related part from Motika [Mot17] covers the compilation of SCCharts using SLIC. The work focuses on the high-level transformations from Extended SCCharts to Core and Normalized SCCharts and only sketches out further low-level compilation possibilities, as also already described previously [MSH14; SMH15]. It presented the intermediate language S, which served as common target for the model-based compilation and as source for the final code serialization. The general design is depicted in Figure 2.3.1b.

This thesis does not discuss the high-level transformations of SCCharts covered by Motika. Chapter 5 focuses on low-level compilation approaches using SCCharts as example language. While the general design flow, shown in Figure 2.3.1b, remains untouched for the most parts, the interactive model-based approach makes this process fully modular and not restricted to any meta-models. External components, such as external compilers

(shown in grey in the figure), can be included into the compilation chains to enable in-editor simulation and deployment easily. Furthermore, S is not used anymore by default, because the default compilation systems are configured such that the intermediate results are synthesized in a model representation known by the developer to facilitate understandability. However, if desired, a meta-model for S can be implemented and used for particular steps.

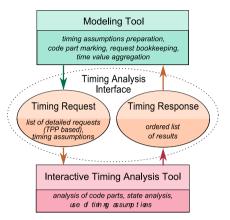

Interactive Timing Analysis Fuhrmann used the model-based approach in her thesis [Fuh17] to facilitate timing analyses. The modeller can fetch timing values from dedicated timing analysis tools interactively while modelling. If building models with safety-critical timing constraints, they are able to identify critical program parts early on in the development. A generalized interface makes the approach feasible for different modelling and timing tools. The overall design flow is depicted in Figure 2.3.2a.

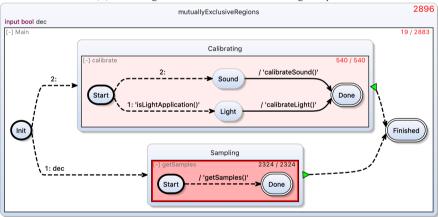

The approach has exemplary been implemented for SCCharts [FBS+14a] [FBH+16]. Figure 2.3.2b shows an SCChart model within the modelling environment with interactively annotated timing values. Critical regions w.r.t. to timing are highlighted in red. Hence, the modeller receives instant feedback about their timing constraints. Since the Interactive Timing Analysis (ITA) tool had to be partly hardwired in the previous version of the KiCo, it is a good example for the possibilities of the model-based compilation approach. In todays version of the compiler, which is explained in detail in Part I, the whole design flow and annotated visualization can be realized. Nonetheless, ITA is not part of this thesis.

## 2.3.2 A Modular Compiler Infrastructure—LLVM

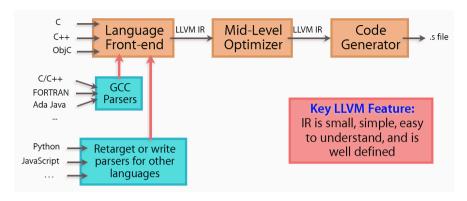

LLVM [Lat02] is a modular compiler infrastructure for arbitrary many programming language, with Clang being one of the most prominent ones. Since its beginnings as a research project in 2002, LLVM has grown to an umbrella project for various commercial and open-source sub-projects, such as Clang, libc++ or SAFECode, a memory safety compiler for C/C++ programs. The LLVM architecture, which can be seen in Figure 2.3.3, strictly distinguishes between front- and back-end. Different languages use their

#### 2.3. Related Work

(a) The design flow of the interactive timing analysis

(b) SCCharts example within the modelling environment with interactively annotated timing values and hot spot highlighting for timing critical regions

**Figure 2.3.2.** Previous work done regarding interactive timing analysis by Fuhrmann (from [Fuh17])

Figure 2.3.3. LLVM Architecture [Lat06]

dedicated front-ends to compile source code, including debug information, to the LLVM Intermediate Representation (LLVM IR). From here modular units can optimize the IR before it is processed further by the code generator and hence, all front-ends benefit from the succeeding optimizations and the code generation.

Lattner distinguishes a compiler from a compiler infrastructure by defining both.

Definition

A *compiler* is a tool that inspects and manipulates a representation of programs. A *compiler infrastructure*

- provides modular and reusable components for building compilers,

- reduces the time and cost to construct a particular compiler,

- allows components to be shared across different compilers and

- allows choice of the *right component for the job* [Lat06].

This thesis shows that by this definition, KiCo, as implementation of the interactive model-based compilation approach presented in this thesis, classifies as compiler infrastructure.

Following the SLIC idea, every unit of work of the interactive model-based approach creates a fully functional artefact but defined by the underlying meta-model instead of an IR defined by the compiler. Language front-ends

often try to reach a common IR in modular compiler infrastructures to facilitate modularity. In contrast, the compilation systems in interactive model-based compilations try to stay in their domain meta-model as long as possible to support understandability and readability. This design decision sacrifices some of the cross-language capabilities but provides the modeller with views they understand. Nonetheless, even with this sacrifice, languages which operate in similar domains, e. g. synchronous languages, can profit from cross-language modularity. The approach is presented in Part I. Furthermore, Chapter 5 discusses common compilation techniques and ways how general purpose compilations can also benefit from the approach presented in this thesis.

The LLVM team won the ACM Software System Award, which recognizes *Remark* a software system that has had a lasting influence, reflected in contributions to concepts, in commercial acceptance, or both (across the entire software industry), in 2012<sup>2</sup>.

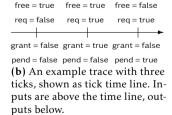

2.3.3 Meta-Tool Generators—ETI and Cinco

The close relation between compilation and modelling techniques has been observed quite early by Steffen, who proposes to make use of *consistency models* to detect inconsistencies between different model descriptions and relates this to giving a semantics to a programming language by translation into an intermediate language [Ste97]. The operational behaviour was modelled as temporal or causal models, which fundamentally is a combination of labelled transition systems and Kripke structures [Sti92]. The definition of adequate unifying model structures was paramount here. The trade-off between expressiveness and manageability was resolved by giving priority to *simplicity*, which is also a decisive factor in designing modular modelling systems in my eyes. Steffen's observation of the trade-off between model size and complexity of interpretation can also be found in SCCharts' distinction between Core and Extended SCCharts.

The growing complexity of software and hardware systems prompted the development of the Electronic Tool Integration (ETI) platform. It is an

<sup>&</sup>lt;sup>2</sup>https://awards.acm.org/software-system/award-winners

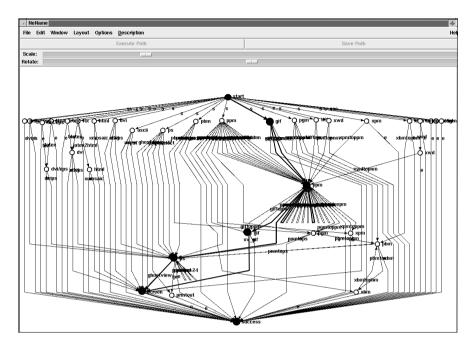

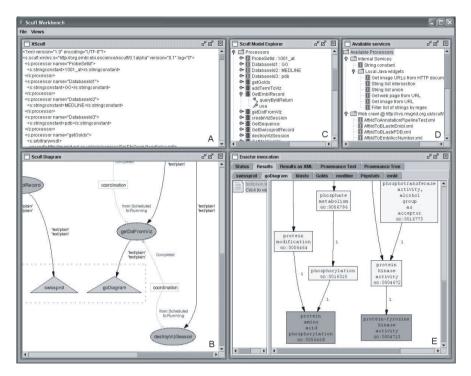

Figure 2.3.4. The UNIX coordination universe (from [SMB97])

online service for experimentation, coordination and evaluation of tool functionalities. ETI addresses two different communities, namely *tool builders* and *tool users*, which influenced the central design decision of strict separation of integration and coordination at the expense of increased effort during the integration phase. The trade-off is another step towards simplicity on the users side. A small group of experts has to do a little more work to increase user comfort. ETI allows a *loose* coupling of services, which is done via *coordination sequences*. A coordination sequence is a triple of the form (input-type, activity, output-type) [SMB97].

The different user roles also play a major role in the design of the approach presented here, which is explained in Section 3.2.3. While different groups of communities may have different foci, they can still benefit from each others developments. Moreover, interactive model-based compilations

**Figure 2.3.5.** CINCO generates ready-to-run modelling tools from abstract tool specification (from [NLK+18]).

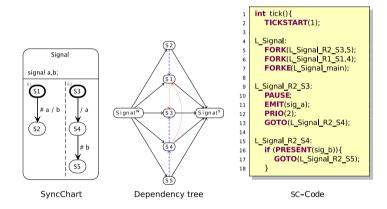

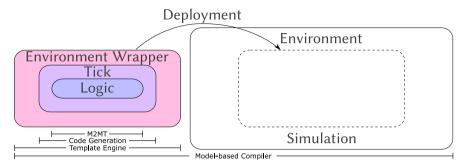

use *environments*, explained in detail in Section 3.1.3, as general form of inputs and outputs for its compilation units. While an environment is an amalgamation of data, a compilation unit can be written as triple of the form (input environment, process, output environment). Also, compilation units are categorized into specialized work units, which is in line with ETI's process systems.

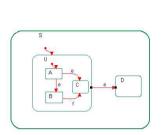

To fulfil coordination requests, ETI uses *coordination graphs*, which represent *all*, the *minimal* and the *shortest* solution to these requests. An example for the UNIX universe can be seen in Figure 2.3.4. The highlighted path depicts a solution for the request gif & F {rotate, relief, display}. A similar graph will be constructed interactively for all compilation units available in KiCo in Section 4.2. This compilation systems' graph represents all possible routes from source to target meta-models and therefore covers all possible compilation paths. Similar to ETI, compilation requests could be realized as service.

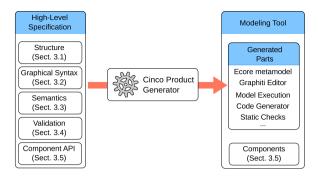

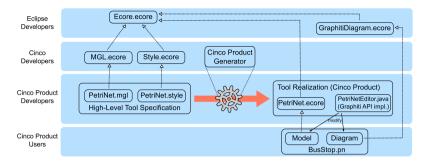

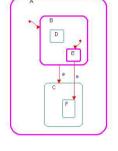

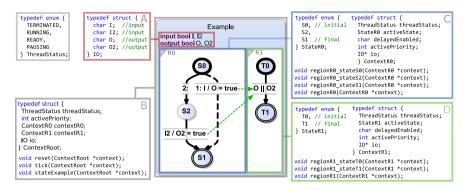

Despite the fact that DSLs bring problem solving solutions to domain experts, creating domain-specific graphic modelling tool is often complex and repetitive. To reduce this tedious task, the meta-model generator CINCO was developed. CINCO is a meta-model generator which generates domain-specific graphical modelling tools from specifications. Therefore, as is depicted in Figure 2.3.5, high-level specifications serve as input for the CINCO

**Figure 2.3.6.** Petrinet modelling tool automatically generated by CINCO (from [NLK+18])

product generator which generates a corresponding graph-based modelling tool fully automatically. As before, simplicity is a central design criterion [MS10]. Universality is traded for intuitive and simple specifications. While building on the modelling capabilities of the Eclipse Rich Client Platform [MLA10] and the Eclipse Modeling Framework (EMF) [SBP+08], technical details are hidden from the user. [NLK+18]

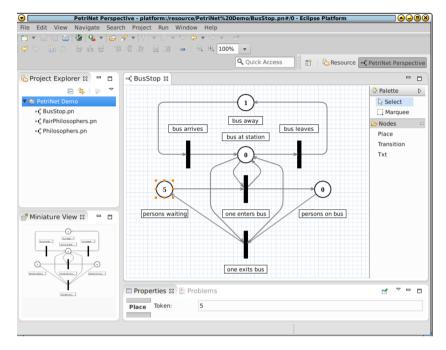

CINCO'S meta graph languages specifies what kind of nodes, edges and containers are present in a certain DSL. These can be annotated by style modifiers which influence their looks. Model transformations then add semantics to the graph model. As an example, Figure 2.3.6 shows a fully generated graphical editor for Petri Nets [Pet62].

Figure 2.3.7. Developer role layer from Cinco's point of view (from [NLK+18])

The approach presented in this thesis is agnostic towards the metamodels of the compilation artefacts. The KiCo approach is not a meta-model generator. The generic framework can be used to implement various source and target languages and re-use already existing compilation systems, which makes it are *meta-model engine*. The pragmatic transient view concept enables domain-specific modelling accompanied by instantaneous graphical support. This is an alternative to the graph model approach and attempts to combine the best of the textual and graphical modelling worlds.

Figure 2.3.7 shows the different roles involved with a Cinco product, in this case, the Petri Net example. As said, Cinco builds upon Eclipse, so the top two rows show the roles programming experts have to solve. In the third row, the experts the particular domain are involved. They specify the graph language and generate the modelling tool. Finally, domain experts can use the final product to solve their domain-specific problems.

The interactive model-based approach also separates the target audience in two groups, the domain experts using the compiler and the compiler developers. As the requirements of both groups differ, the approach tries to find a good middle-ground of complexity so that both groups can benefit from each others work-flows. Developers should be conscious of the different groups which are involved in a product. Tools should guide them in order to increase efficiency and should not be overloaded with complex features to appeal to all possible groups. Chapter 4 discusses examples towards guidance in modelling environments.

Figure 2.3.8. Web-based Cinco product development (from [Zwe18])

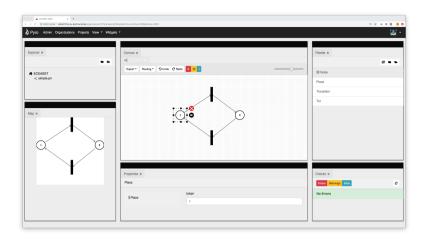

Another development which is becoming increasingly dominant is the Integrated Development Environments (IDEs)' and products' shift from classical desktop towards web applications. This is not exclusive to Cinco but can be exemplified here as Cinco can also be used to generate a fully functional web toolkit for its graph specifications. The web version of a Petri net editor generated by Cinco is shown in Figure 2.3.8. The kit called Pyro builds upon the Graphical Language Server Protocol (GLSP) and uses common web framework for its browser support. While being generated by Cinco it is independent from the remainder of its code base Pyro [Zwe18].

The tools' movement towards the web is not part of this work. However, an outlook and more related work with concrete connection to the KIELER product is discussed in Section 8.2.

Remark

Despite the fact that the Cinco and the KIELER teams may be working on different meta-levels and are focusing on different pragmatical aspects, I see the spirits of both teams very much aligned. Thereby, I would like to adopt the slogan of the Cinco team "Hard for us, easy for them" and extend it in the following to "If necessary, hard for us—but always easy for them" for the KIELER team.

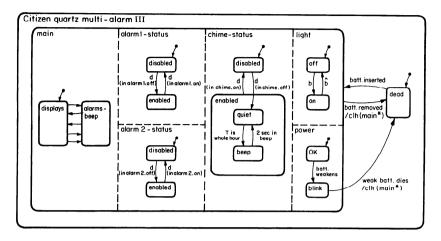

Figure 2.3.9. Part of the Citizen Quartz clock example (from [Har87])

#### 2.3.4 Statecharts

Statecharts, presented by Harel in 1987 [Har87], are a visual formalism for describing behaviour. They extend the classical state-transition diagrams with hierarchy, orthogonality and communication. In that they are compact and expressive as well as modular. In fact, they were set out to counter many of the objections people had against visual representations of behaviour at the time of publishing.

Figure 2.3.9 shows a part of the Citizen Quartz clock, the leading exam-Example ple in Harel's initial contribution. Even without further explanation, one can identify states, hierarchy (superstates), orthogonality (different regions separated by dashed edges) and communication via trigger and effects on the transitions. Basically, statecharts are Mealy Machines [Mea55] with hierarchy, concurrency and broadcast communication.

Statecharts shifted the way developers worked. Instead of relying on graphical representations only for guidance while working on textual artefacts, visual languages became the pre-dominant objects for description, verification and code generation – at least in some areas, such as the avionics industry. Statecharts are a *clear* and *precise* visual programming language

which programs can be analysed, compiled and executed [Har09]. Harel reminds to caution because even though many people would agree that a picture is worth a thousands words, not everything can be visualized or depicted in a way that is clear and fitting for the brain. While the interactive model-based approach is agnostic towards the compilation artefacts, VDSLs, e. g. SCCharts, are well-suited for the approach presented in this thesis, since every intermediate compilation step can be presented in a way the domain experts understands.

The initial contribution also encouraged to exploit pragmatic peculiarities of the language, such as *zooming in* on different abstraction levels, which nowadays has become a common feature and is also used in KIELER [SSH13] instead of opening up separate windows for each hierarchy. While the statecharts team strongly believed in the virtues of visual languages, they acknowledged that the visuals can be replaced by their textual or algebraic descriptions. The pragmatics-aware modelling approach tries to combine the best of both worlds, which was also coined *textical modelling* by Motika [Mot17]. The modeller works on a textual description, while inspecting the instantaneously created graphical representation, even though this modelling philosophy is not a requirement for the KiCo approach.

Statecharts sparked a whole family of Statechart dialects, many of which implementing or discarding specific languages features or having semantic variation points. The lack of clear guidance regarding the semantics of statecharts proved out to be an issue; von der Beeck [Bee94] summarized 21 Statechart variations, including the initial semantics proposed by Harel et al. [HPS+87] and their differences in 19 semantic variation points. The report did not, however, contain the semantics of the original statecharts implemented in Statemate [HN96]. One of the more controversial questions was - and is still today in the synchronous community - if the reactions of a system can be sensed within the same tick or at earliest in the following. SCCharts, being a conservative extension to SyncCharts and hence, Esterel, follows the first approach. The latter approach is, e.g. implemented in languages such as ForeC [YGR+16]. Statecharts' standard feature of inter-hierarchy transitions is not part of SyncCharts and hence, also not implemented in SCCharts. However, it can be realized on extended level and could be added to the repertoire of the SCCharts language if needed.

#### 2.3. Related Work

(a) Substate transitions override superstate transitions in Rhapsody (from [HK04]).

**(b)** Transition priorities in Rhapsody are determined inside-out (from [HK04]).

(c) Model from (a) in SCCharts

Figure 2.3.10. Conflicting Transitions in Rhapsody and Statemate

Some arguably exotic features initially presented by Harel are *selection entrances*, *parameterized states*, and *recursive and probabilistic statecharts*. An implementation of probabilistic transitions in SCCharts is sketched out in Section D.2. *Hybrid systems*, implemented in KIELER SCCharts via dataflow regions as extended feature, are explained in Section 6.2. A way of model verification via *model checking* is briefly discussed in Section 7.1.2.

I recommend Harel's notes about the making of statecharts [Har09] for *Remark* further reading as they contain an interesting (personal) view on the history of statecharts, important design decisions and clearing up some confusion that arose during the years.

The first tool built for statecharts was Statemate, released initially in 1986 [HLN+90]. Here, statecharts describe component behaviour. *Activity charts*, basically hierarchical dataflow diagrams, are used to model the functional structure of the system. The actual structure of the system was modelled via *module charts*, which specified real components and their connections. Created statecharts could be analysed, used for documentation and served as source for the automatic code generation, which produces code in Ada or C. Being one of the first real model-driven system development tools, Statemate can be seen as important step towards the standardized

Unified Modeling Language (UML) efforts for model-driven engineering we have today.

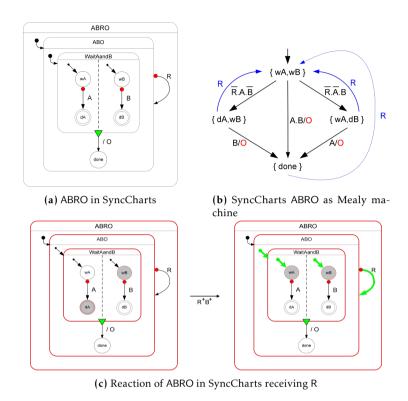

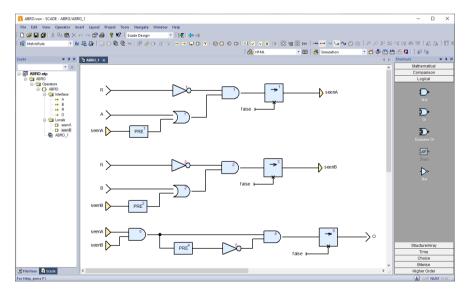

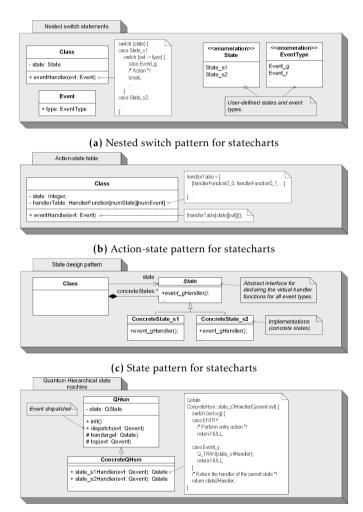

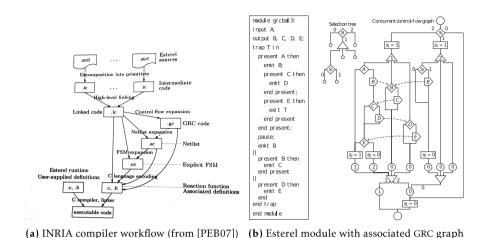

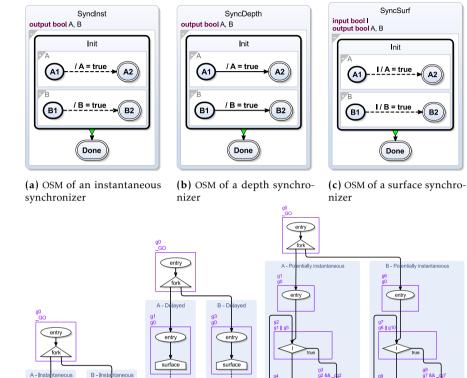

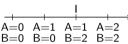

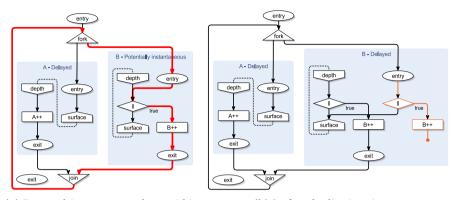

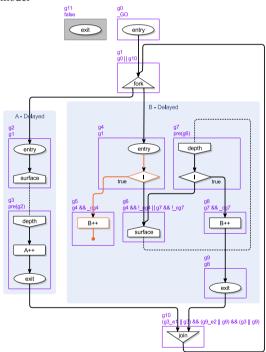

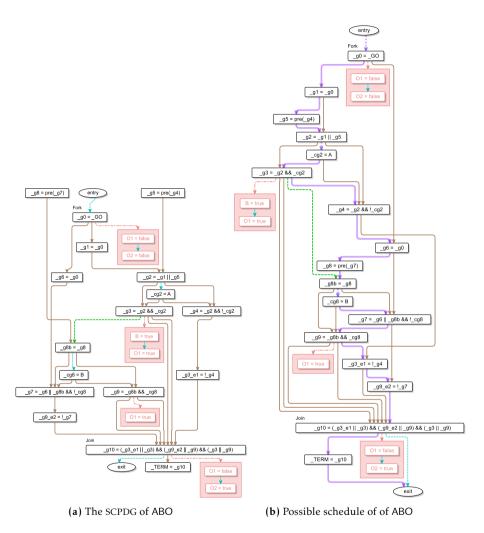

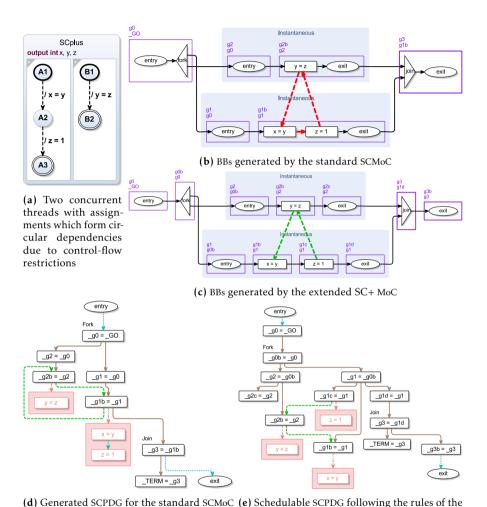

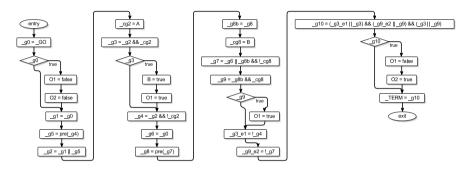

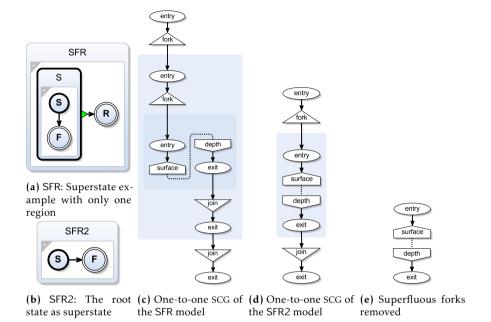

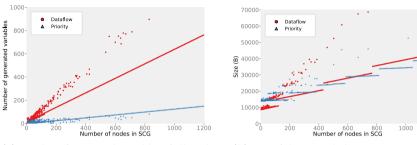

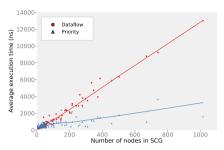

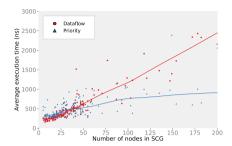

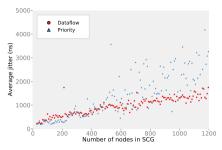

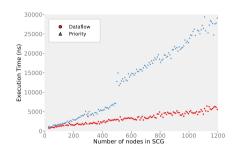

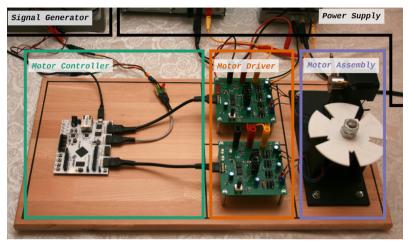

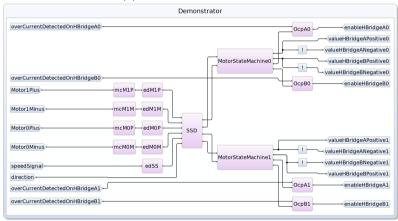

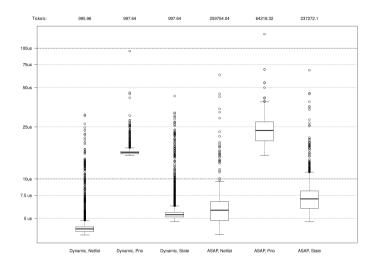

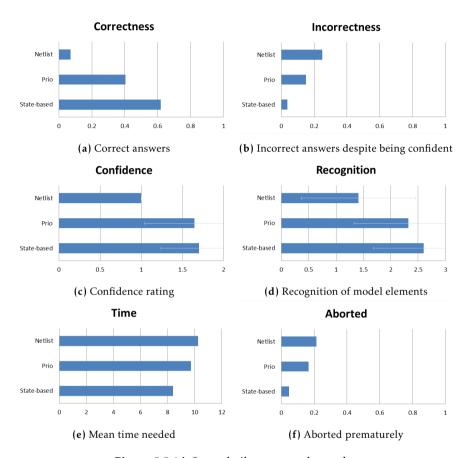

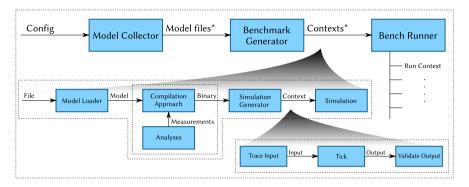

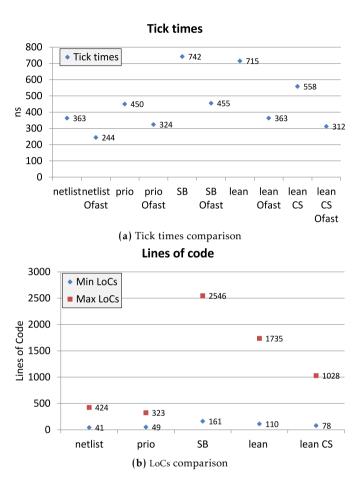

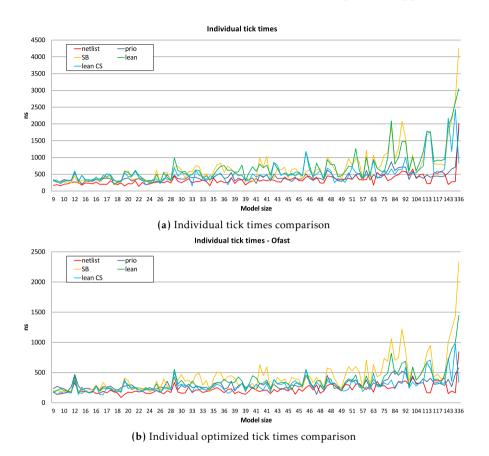

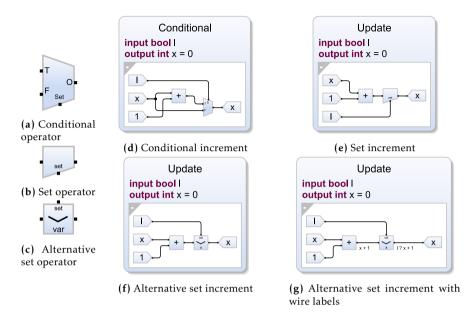

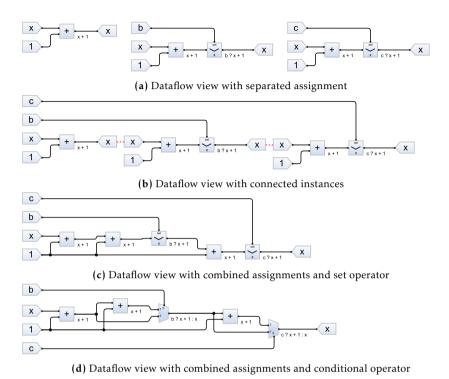

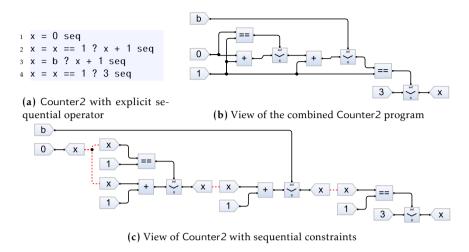

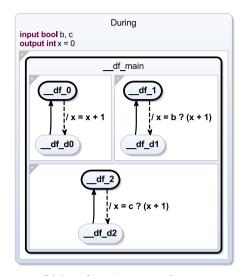

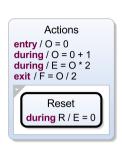

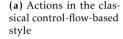

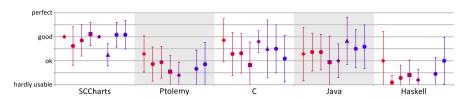

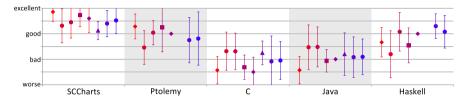

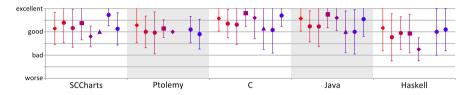

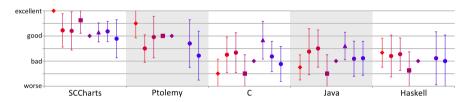

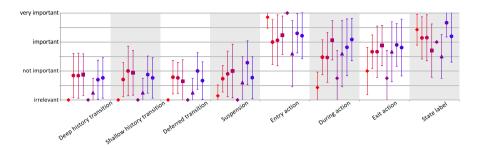

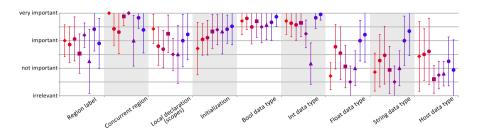

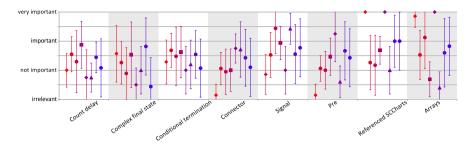

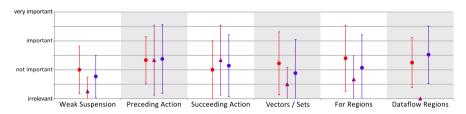

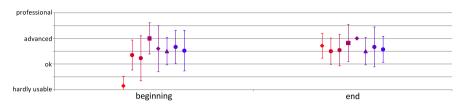

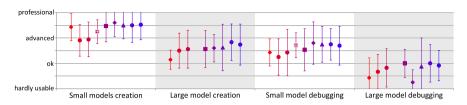

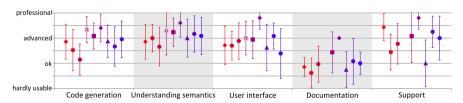

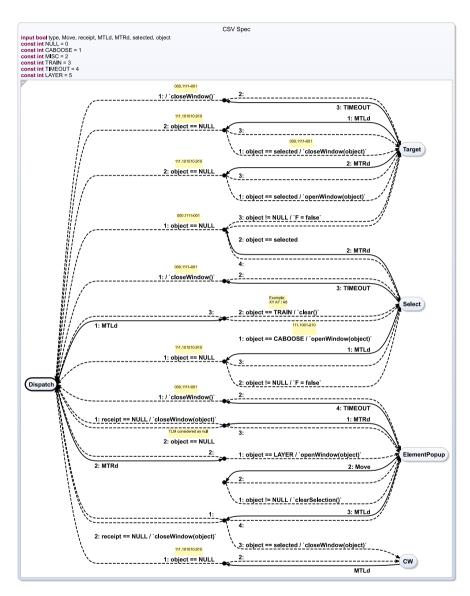

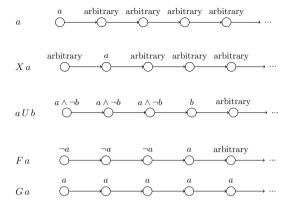

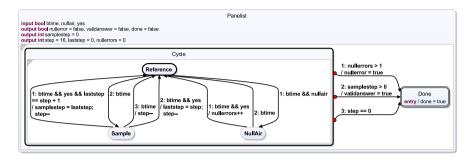

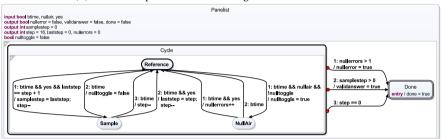

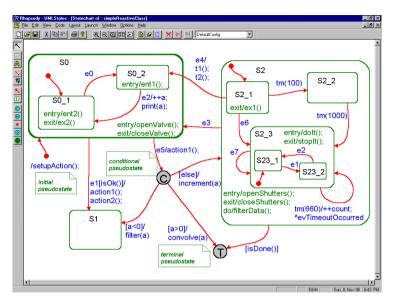

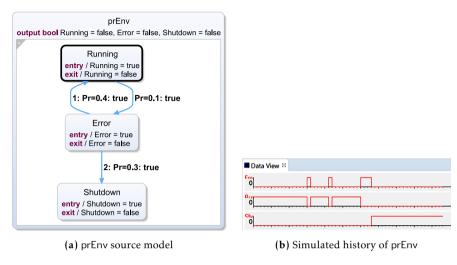

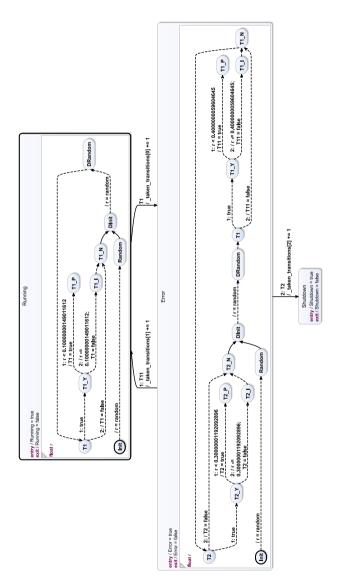

Remark