# **Active Thermal Control and Digital Twin-based Observation of Hybrid Grids-Feeding Smart Transformers**

#### **Dissertation**

zur Erlangung des akademischen Grades

Doktor der Ingenieurwissenschaften

(Dr.-Ing.)

Technische Fakultät

der Christian-Albrechts-Universität zu Kiel

vorgelegt von

Johannes Kuprat, M. Sc.

aus

Neumünster 2023

## Erklärung

Ich erkläre an Eides statt, dass ich die Dissertation zum Thema:

Active Thermal Control and Digital Twin-based Observation of Hybrid Grids-Feeding

Smart Transformers

abgesehen von der Betreuung durch Herrn Prof. Marco Liserre selbstständig und ohne Hilfe angefertigt habe und bisher weder ganz noch zum Teil an einer anderen Stelle im Rahmen eines Prüfungsverfahrens vorgelegt, veröffentlicht oder zur Veröffentlichung eingereicht habe. Weiterhin versichere ich hiermit, dass mir kein akademischer Grad entzogen wurde, ich die vorliegende Arbeit unter Einhaltung der Regeln guter wissenschaftlicher Praxis der Deutschen Forschungsgemeinschaft angefertigt habe und alle von anderen Autoren wörtlich übernommenen Stellen, wie auch die sich an die Gedankengänge anderer Autoren eng anlehnenden Ausführungen meiner Arbeit besonders gekennzeichnet und die entsprechenden Quellen angegeben sind.

Kiel, den 22. August 2023

Johannes Kuprat

1. Gutachter: Prof. Marco Liserre, Ph.D.

Gutachter: Prof. Sibylle Dieckerhoff, Dr.-Ing.

Gutachter: Prof. Maryam Saeedifard, Ph.D.

Datum der mündlichen Prüfung: 18.06.2024

Acknowledgment

I would like to thank Prof. Marco Liserre for the supervision and guidance during my doctor-

ate. I learned a lot during the time at the Chair of Power Electronics, which finally resulted

in this dissertation.

Further, I would like to thank Prof. Sibylle Dieckerhoff for reviewing my dissertation and

participating in my disputation.

Additionally, I would like to thank Prof. Maryam Saeedifard for reviewing my disserta-

tion.

Thanks to Markus and Vivek for introducing me to the scientific work in power electronics

during my time as a student.

A big thanks goes to Marius for the support and all the important discussions. Also, a

big thanks to Joscha for all the times we spent together in the laboratory as well as the

collaborative works and discussions. Thanks to Max for the advice in hardware topics. And

to all for the shared laughs and the friendship.

Thanks to Yoann, Karthik, Sante, and Ko for the joint works.

A big thanks to my family, especially my parents, who always supported me in my time as a

student and in my doctorate.

In the end, a huge thanks to my wife, who always had my back during my doctorate.

Neumünster, September 2024

Johannes Kuprat

Contents

## **Contents**

| Deu | tscne  | Kurzia   | issung der Arbeit                                                    | V          |

|-----|--------|----------|----------------------------------------------------------------------|------------|

| Eng | lish S | Summar   | y                                                                    | V          |

| Use | d syn  | nbols ar | nd abbreviations                                                     | V]         |

| 1.  | Intro  | oduction | 1                                                                    | 1          |

|     | 1.1.   | Motiva   | ation of hybrid grids-feeding Smart Transformers                     | 1          |

|     | 1.2.   | Motiva   | ation of observation of the thermal behavior of power modules        | 2          |

|     | 1.3.   | Motiva   | ation of active thermal control of power electronics converters      | 3          |

|     | 1.4.   | Resear   | ch proposal                                                          | 4          |

|     | 1.5.   | Structu  | are of this work                                                     | 5          |

|     | 1.6.   | List of  | publications                                                         | 7          |

| 2.  | Fun    | dament   | als of hybrid grids-feeding Smart Transformers                       | 9          |

|     | 2.1.   | Hybrid   | I grids advantages and requirements                                  | 9          |

|     |        | 2.1.1.   | Hybrid grids definition                                              | 9          |

|     |        | 2.1.2.   | Hybrid grids advantages                                              | 9          |

|     |        | 2.1.3.   | Hybrid grids requirements                                            | 10         |

|     | 2.2.   | Smart    | Transformer architectures                                            | 1          |

|     |        | 2.2.1.   | General ST architectures                                             | 1          |

|     |        | 2.2.2.   | Hybrid grids-feeding ST architectures                                | 1          |

|     |        | 2.2.3.   | Review on hybrid grids-feeding ST topologies                         | 12         |

|     | 2.3.   | Power    | electronics converters for Smart Transformers                        | 13         |

|     |        | 2.3.1.   | Semiconductor losses                                                 | 14         |

|     |        | 2.3.2.   | Transformer losses                                                   | 17         |

|     |        | 2.3.3.   | Dual active bridge                                                   | 21         |

|     |        | 2.3.4.   | Two-level three phase inverter                                       | 26         |

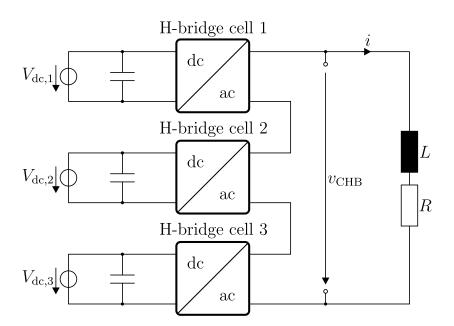

|     |        | 2.3.5.   | Cascaded H-Bridge                                                    | 28         |

|     | 2.4.   | Summ     | ary and conclusions of the chapter                                   | 30         |

| 3.  | Effic  | ciency o | optimization and design of hybrid grids-feeding STs                  | 31         |

|     | 3.1.   | Topolo   | ogies of hybrid grids-feeding STs                                    | 31         |

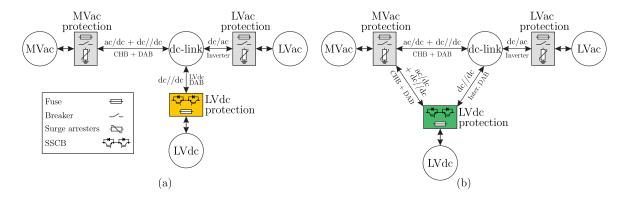

|     |        | 3.1.1.   | Non-interconnected topology                                          | 31         |

|     |        | 3.1.2.   | Interconnected topology                                              | 33         |

|     |        | 3.1.3.   | Method for system efficiency calculation                             | 35         |

|     | 3.2.   | Design   | of converter power rating for hybrid grids-feeding STs               | 39         |

|     |        | 3.2.1.   | Mission profile-based converter power rating design                  | <b>1</b> 0 |

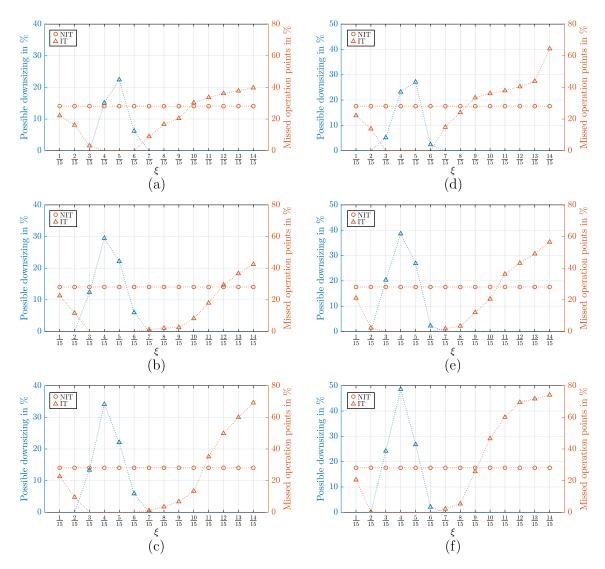

|     |        | 3.2.2.   | Downsizing opportunity of interconnecting dual active bridge 4       | 12         |

|     |        | 3.2.3.   | Sensitivity of converter sizing against mission profile deviations 4 | 18         |

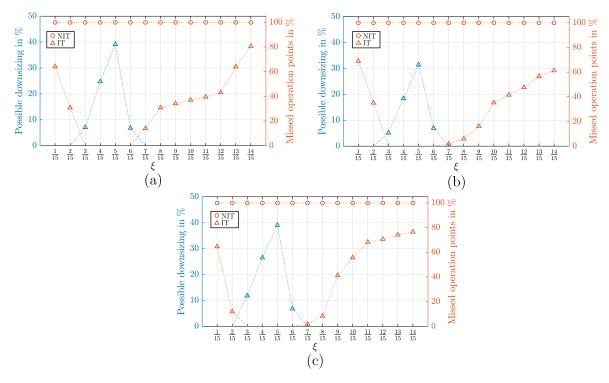

|     | 3.3.   | Passiv   | e power routing for efficiency by design $\epsilon$                  | 54         |

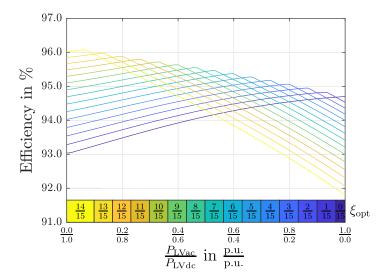

|     |        | 3.3.1.   | Efficiency influence of link ratio choice                            | 55         |

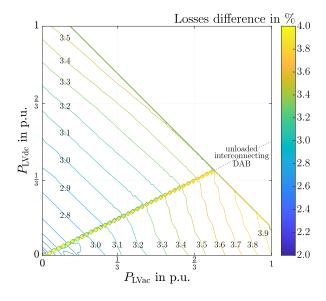

|     |        | 3.3.2.   | Link ratio choice approaches for optimal system efficiency 6         | 66         |

Contents

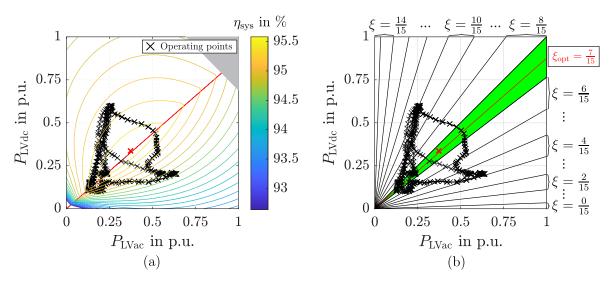

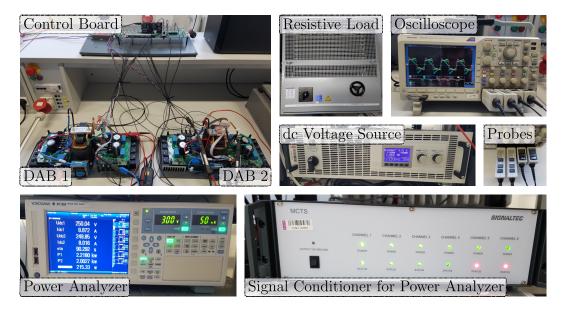

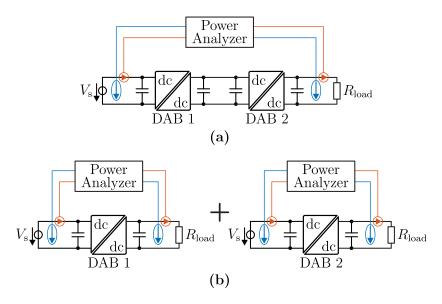

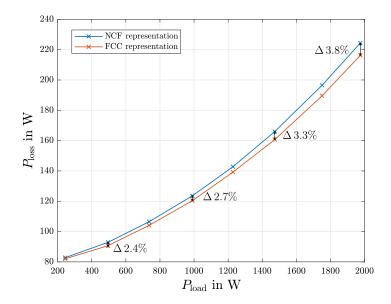

|    |      | 3.3.3.   | Laboratory validation of link ratio efficiency influence               | 70    |

|----|------|----------|------------------------------------------------------------------------|-------|

|    | 3.4. | Summ     | ary and conclusions of the chapter                                     | 76    |

| 4. | The  | rmal diş | gital twins for condition monitoring and temperature observation       | 78    |

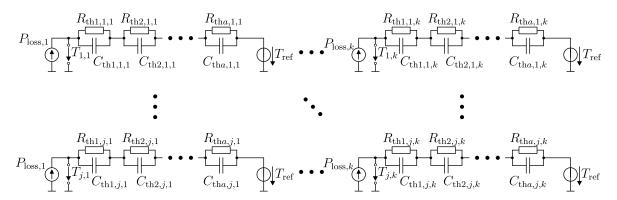

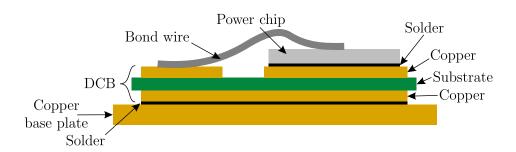

|    | 4.1. | Funda    | mentals of thermal modeling                                            | 78    |

|    |      | 4.1.1.   | Basics of thermal modeling                                             | 79    |

|    |      | 4.1.2.   | Single chip thermal networks                                           | 80    |

|    |      | 4.1.3.   | Multichip thermal networks                                             | 82    |

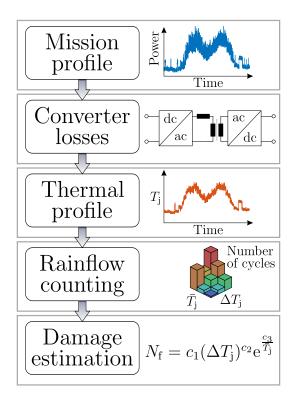

|    | 4.2. | Therm    | al influence on power semiconductor module reliability                 | 83    |

|    |      | 4.2.1.   | Degradation mechanism                                                  | 83    |

|    |      | 4.2.2.   | Thermal cycle-based lifetime estimation                                | 85    |

|    |      | 4.2.3.   | Review on condition monitoring of power semiconductors via ther-       |       |

|    |      |          | mal behavior                                                           | 88    |

|    | 4.3. | Digital  | l twin-based observation of power semiconductor thermal behavior .     | 90    |

|    |      | 4.3.1.   | Basic principle of a thermal digital twin                              | 91    |

|    |      | 4.3.2.   | Particle swarm optimization-based thermal digital twin                 | 94    |

|    |      | 4.3.3.   | Dual extended Kalman filter-based thermal digital twin                 | 100   |

|    |      | 4.3.4.   | Comparison of the thermal digital twin approaches                      | 105   |

|    |      | 4.3.5.   | Multichip thermal digital twin                                         | 115   |

|    | 4.4. | Summ     | ary and conclusions of the chapter                                     | 123   |

| 5. | Reli | ability- | driven active thermal control and design for failure tolerance         | 125   |

|    | 5.1. | Review   | w on Active Thermal Control                                            | 125   |

|    |      | 5.1.1.   | Overview on active thermal control methods                             | 126   |

|    |      | 5.1.2.   | Evaluation of active thermal control methods for the ST                | 129   |

|    | 5.2. | Graph    | theory-based modeling for power routing                                | 131   |

|    |      |          | Graph theory-based modeling of power electronics converter systems     | 131   |

|    |      | 5.2.2.   | Graph theory-based modeling of hybrid grids-feeding Smart Trans-       |       |

|    |      |          | formers                                                                | 133   |

|    |      | 5.2.3.   | Laboratory validation of non-conserved power flow modeling impact      |       |

|    |      |          | on losses                                                              | 141   |

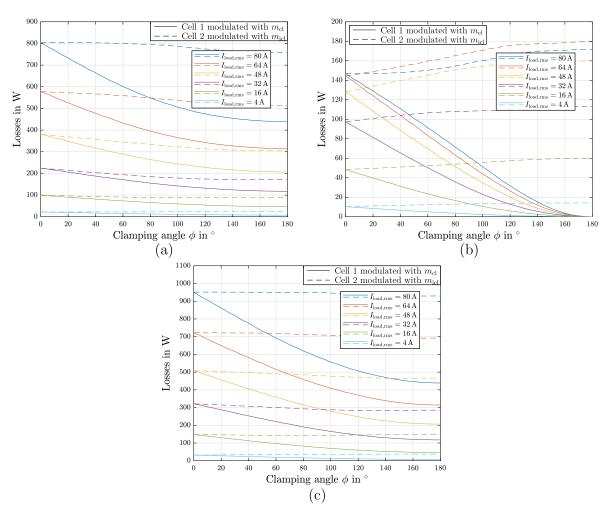

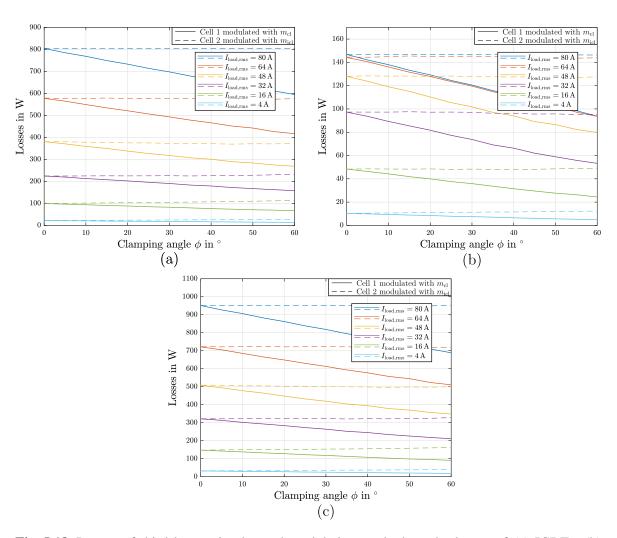

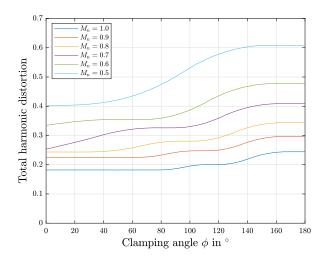

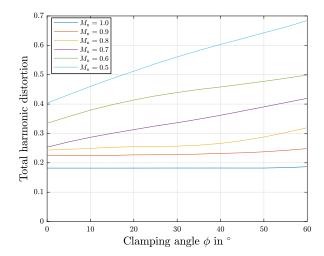

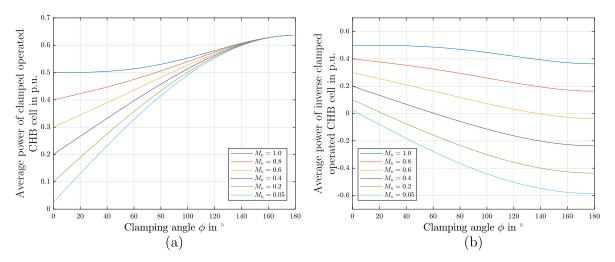

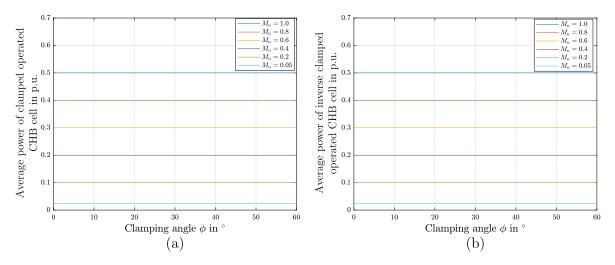

|    | 5.3. | Discor   | ntinuous modulation-based active thermal control for cascaded H-bridge | s 143 |

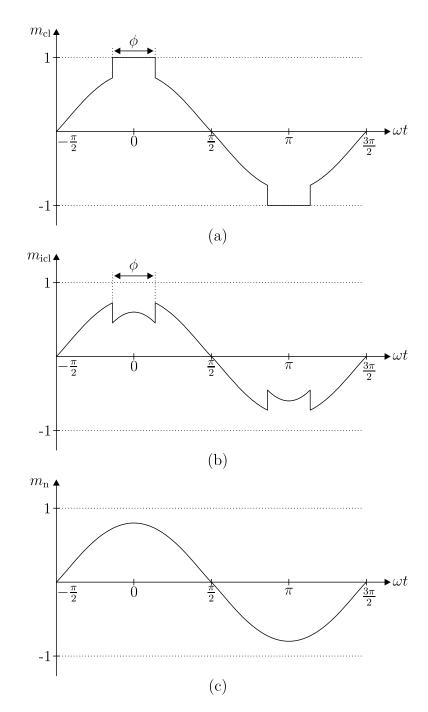

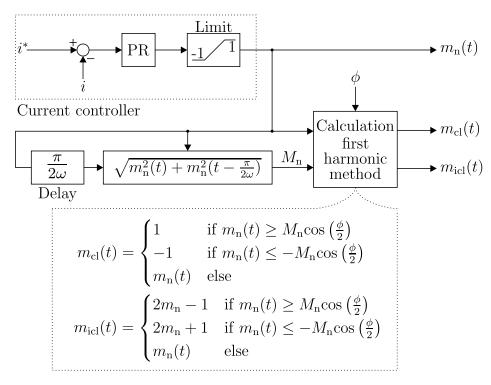

|    |      | 5.3.1.   | First harmonic clamped modulation method                               | 143   |

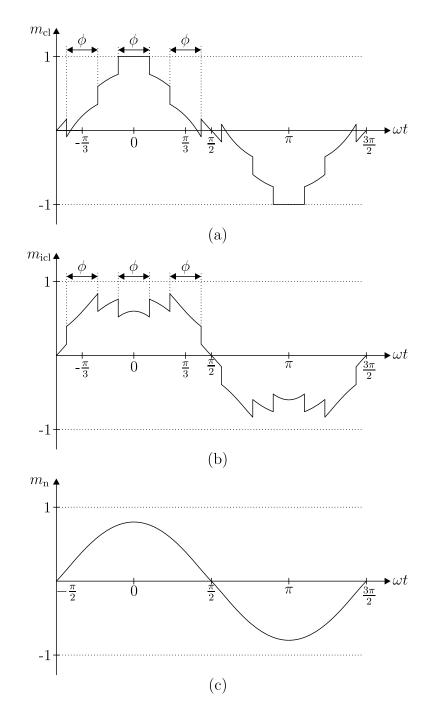

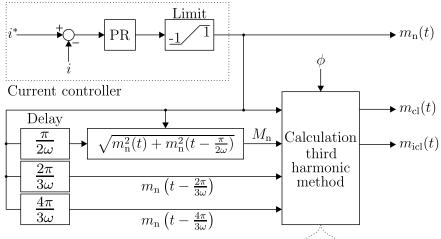

|    |      | 5.3.2.   | Third harmonic clamped modulation method                               | 145   |

|    |      | 5.3.3.   | Comparison of first and third harmonic clamped modulation method       | 148   |

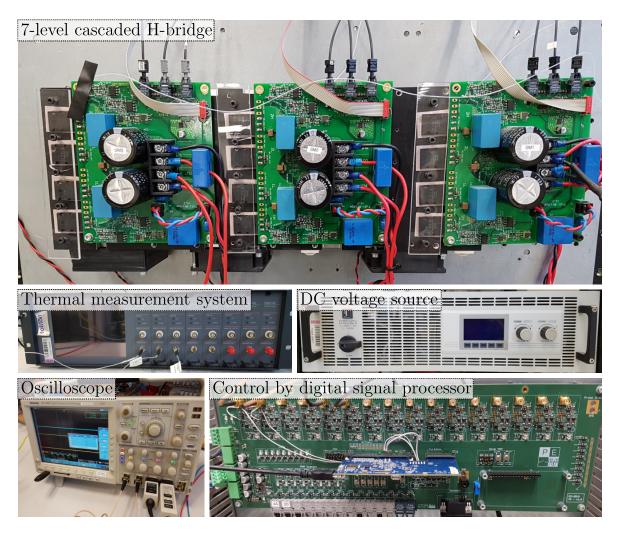

|    |      | 5.3.4.   | Laboratory validation of clamped modulation impact on processed        |       |

|    |      |          | cascaded H-bridge cell power and temperature                           | 155   |

|    | 5.4. | Design   | n for failure tolerance of hybrid grids-feeding STs via passive power  |       |

|    |      | routing  | g                                                                      | 164   |

|    |      | 5.4.1.   | Considered failure cases and structure of the hybrid grids-feeding ST  | 164   |

|    |      | 5.4.2.   | Impact of MVac power electronics building block failures on possi-     |       |

|    |      |          | ble operation points                                                   | 165   |

Contents III

|      | 5.4.3. Impact of modular LVdc and interconnecting dual active bridge power |    |

|------|----------------------------------------------------------------------------|----|

|      | electronics building block failures on possible operation points 10        | 67 |

|      | 5.5. Summary and conclusions of the chapter                                | 71 |

| 6.   | Summary, conclusions and future research                                   | 74 |

|      | 6.1. Summary and conclusions                                               | 74 |

|      | 6.2. Future research                                                       | 78 |

| Refe | rences                                                                     | 81 |

| List | of Figures                                                                 | 11 |

| List | of Tables                                                                  | 22 |

## **Deutsche Kurzfassung der Arbeit**

Die zunehmende Integration von dezentralen erneuerbaren Energiequellen (EE) und Ladesystemen für Elektrofahrzeuge (LEF) in das Stromnetz stellt Herausforderungen für den Umgang mit hohen Schwankungen bei Erzeugung und Verbrauch dar. Der Einsatz eines hybriden Verteilungssystems - das Gleichstromnetze in die bestehende Wechselstromnetzstruktur einbettet - kann eine Integration von EE und LEF mit hohem Wirkungsgrad über Gleichstromnetze mit den etablierten Schutzmechanismen von Wechselstromnetzen kombinieren. Die Bereitstellung einer flexiblen Wechsel- und Gleichstromverteilung und möglicher Netzdienstleistungen kann durch den Smart Transformator (ST) ermöglicht werden, dies ist ein Leistungs-elektronik-basierter Transformator mit fortschrittlichen Regelungsfunktionen. Zwei Haupt-bedenken bestehen, welche die Einführung von STs für das Verteilungssystem behindern: Wirkungsgrad und Zuverlässigkeit.

Diese Arbeit trägt zur Verbesserung des Wirkungsgrades und der Zuverlässigkeit des STs bei, indem sie eine optimierte ST-Topologie für hohe Wirkungsgrade bei der Bereitstellung von hybriden Netzen vorschlägt, Konzepte digitaler Zwillinge für die Beobachtung des thermischen Verhaltens von Leistungsmodulen entwickelt und für die Unterstüzung eines zuverlässigen ST-Betriebs wesentliche Ansätze zur aktiven thermischen Regelung ausarbeitet.

Zunächst werden die Vorteile und Anforderungen von hybriden Netzen und die geeigneten ST-Architekturen vorgestellt. Außerdem werden leistungselektronische Stromrichter eingeführt, welche zur Realisierung von ST-Topologien verwendet werden.

Eine konfigurierbare ST-Topologie für einen optimalen Wirkungsgrad bei vorgegebenem hybriden Netzbetriebsprofil wird vorgeschlagen. Es werden ein auf Betriebsprofilen basierendes Entwurfsverfahren für die Stromrichterleistungen und die Möglichkeit zur konfigurationsbedingten Verkleinerung des Vermaschungsstromrichters vorgestellt.

Leistungshalbleiter gehören zu den fehleranfälligsten Komponenten in leistungselektronischen Systemen. Ihr thermisches Verhalten ist ein Faktor, der zur Überwachung ihres Gesundheitszustandes herangezogen werden kann. Daher sind thermische Echtzeitmodelle, deren Parameter auf der Grundlage des Vergleichs von geschätzten Temperaturen mit Mess-ungen am physischen System optimiert werden, - thermische Digitale Zwillinge - von Vorteil. In dieser Arbeit werden zwei Ansätze entwickelt, die auf einer Partikel-Schwarm-Optimier-ung und einem dualen erweiterten Kalman-Filter basieren.

Die Reduzierung und Verlagerung der thermischen Belastung von Leistungshalbleitern durch aktive thermische Regelung (ATR) kann einen zuverlässigen ST-Betrieb unterstützen. Diese Arbeit gibt einen Überblick über ATR-Methoden und geht auf zwei für den ST wesentliche Methoden ein - Graphentheorie-basierte Leistungsverteilung und diskontinuierliche Modulation. Außerdem wird vorgeschlagen, die geringere Stromrichterbelastung in der vermaschten ST-Topologie für zusätzliche Fehlertoleranz zu nutzen.

## **English Summary**

The increasing integration of distributed renewable energy sources (RES) and electric vehicle (EV) charging systems into the electricity grid poses challenges in handling high generation and demand variability. The utilization of a hybrid distribution system - which embeds do grids inside the existing ac grid structure - could combine an efficient integration of RES and EV charging stations via dc grids with the established protection mechanisms of ac grids. The provision of a flexible ac and dc distribution and further possible grid services can be enabled by the Smart Transformer (ST), which is a power electronics-based transformer with advanced control functionalities. However, two major concerns impeding the adoption of STs for the distribution system are the efficiency and reliability.

This work contributes to the advancement of efficiency and reliability in the ST by proposing an optimized ST topology for efficiently establishing hybrid grids, developing digital twin approaches for observing the thermal behavior of power modules, and elaborating on active thermal control approaches essential to support a reliable ST operation.

The advantages and requirements of hybrid grids and the suitable ST architectures are presented as a first step. Further, power electronics converters to realize ST topologies based on these architectures are introduced.

Based on these fundamentals, an interconnected ST topology whose configuration can be adjusted to provide optimized efficiency for a hybrid grid mission profile is proposed. Furthermore, a mission profile-based design procedure for the converter power ratings in the proposed topology is presented and the opportunity for downsizing the interconnecting converter based on the configuration revealed.

Power semiconductors are among the components most prone to failure in power electronics systems. Their thermal behavior is one factor which can be used to monitor their health condition. Therefore, thermal digital real time models whose parameters are optimized based on the comparison of estimated temperatures with measurements on the physical system - thermal digital twins - are advantageous. This work develops two approaches based on a particle swarm optimization and a dual extended Kalman filter.

Reducing and relocating the thermal stress on power semiconductors via active thermal control (ATC) can support a reliable ST operation. This work gives an overview on ATC methods and elaborates on two essential ones for the ST - graph theory-based power routing and discontinuous modulation. Further, utilizing the lower converter loading in the interconnected ST topology for additional failure tolerance is proposed.

## **Used symbols and abbreviations**

#### **General symbols**

#### **General notations**

x(t), x Time-variant variable

x(y) Variable x depends on variable y f(y) Function that depends on variable y

x, X Vector or matrix  $\bar{x}$  Average value  $\hat{x}$  Estimated value  $\hat{x}$  Time derivative

$P_{j,k}$  Power flow from node j to node k in a directed graph

$W_{j,k}$  Weight of the arc from node j to node k in a directed graph

(j,k) Arc originating in node j and ending in node k in a directed graph

$(P_{LVac}P_{LVdc})$  Hybrid grid operation point

#### **Superscripts**

\* Indicates reference variables' Indicates compensated variables

Indicates variables after the correction step in a Kalman filter

Indicates variables before the correction step in a Kalman filter

conv Indicates variables that converged to a steady value CS Indicates variables referring to a current source DAB Indicates variables referring to a dual active bridge

filt Indicates variables that a smoothing filter was applied to graphic Indicates variables referring to a graphical representation

max Maximum value

max, graphic Maximum value that can be read from the graphical representation

min Minimum value

#### **Subscripts**

a Index of variables referring to an ambient condition ac Index of variables referring to an alternating current

ac, rms, ph Index of variables referring to a root mean square alternating current

value between line and neutral conductor

amp Index of variables referring to an amplitude value aux Index of auxiliary variables for case distinction

AWE Index of variables referring to the average weighted system efficiency block Index of variables referring to the blocking state of a semiconductor block, ref Index of variables referring to a reference value of the blocking state of

a semiconductor

buck Index of variables referring to a buck converter c Index of variables referring to the collector cauer Index of variables referring to a Cauer network

cc Maximum value at the collector

ce Index of variables between collector and emitter

cell Index of variables referring to one cell of a cascaded H-bridge

ce(sat) Saturation value between collector and emitter

CHB Index of variables referring to a cascaded H-bridge

CHB, dc Index of variables referring to a direct current value of a cascaded

H-bridge

CHB, ph Index of variables referring to one phase of a cascaded H-bridge

CHB, rms Index of variables referring to a root mean square value of a cascaded

H-bridge

CHB, rms, fund Index of variables referring to a root mean square value at fundamental

frequency of a cascaded H-bridge

chip Index of variables referring to a chip of a power semiconductor module cl Index of variables referring to the clamped operated cell of a cascaded

H-bridge

cl, 1st Index of variables referring to the clamped operated cell of a cascaded

H-bridge for first harmonic clamped modulation method

cl, 3rd Index of variables referring to the clamped operated cell of a cascaded

H-bridge for third harmonic clamped modulation method

CoM Index of variables referring to the center of the mission profile

con Index of variables referring to the conduction

con, diode Index of variables referring to the conduction of a diode

con, IGBT Index of variables referring to the conduction of an insulated gate bipolar

transistor

cond, pri Index of variables referring to the conductor on the primary side of a

transformer

cond, sec Index of variables referring to the conductor on the secondary side of a

transformer

core Index of variables referring to the core of a transformer

core, win Index of variables referring to a transformer core window

cr Index of variables referring to a cross section

CS, in Index of variables referring to the virtual input of a current source

CS, out Index of variables referring to the output of a current source

$C_{\rm th}$  Index of variables referring to a thermal capacitor

Cu Index of variables referring to copper

Cu, pri Index of variables referring to copper on the primary side of a

transformer

Cu, sec Index of variables referring to copper on the secondary side of a

transformer

d Index of variables referring to the damping part of a controller

D Index of variables referring to a diode

DAB Index of variables referring to a dual active bridge

DAB, NIT Index of variables referring to the low voltage direct current dual active

bridge in the non-interconnected topology

DAB, in Index of variables referring to the input of a dual active bridge

DAB, IT Index of variables referring to the interconnecting dual active bridge in

the interconnected topology

DAB, out Index of variables referring to the output of a dual active bridge

dc Index of variables referring to a direct current

dc – link Index of variables referring to the direct current-link

dia Index of variables referring to a diameter

exe Index of variables referring to the execution of an electrical simulation

f Index of variables referring to the failure of a device

g Index of variables referring to a grid

ge Index of variables between gate and emitter ge(th) Threshold value between gate and emitter

gg Maximum value at the gate

i Index of variables referring to the interconnecting dual active bridge icl Index of variables referring to the inverse clamped operated cell of a

cascaded H-bridge

icl, 1st Index of variables referring to the inverse clamped operated cell of a

cascaded H-bridge for first harmonic clamped modulation method

icl, 3rd Index of variables referring to the inverse clamped operated cell of a

cascaded H-bridge for third harmonic clamped modulation method

in Index of variables referring to the input of a system

inv Index of variables referring to an inverter

j Index of variables referring to the junction of a transistor

L Index of variables referring to an inductor

$L_{\text{buck}}$  Index of variables referring to the inductance of a buck converter

link Index of variables referring to a link between converters

load Index of variables referring to a load

load, rms Index of variables referring to a root mean square value of a load

loss Index of variables referring to losses

loss, const Index of variables referring to constant losses

loss, core Index of variables referring to transformer core losses

loss, Cu, pri Index of variables referring to copper losses on the primary side of a

transformer

loss, Cu, sec Index of variables referring to copper losses on the secondary side of a

transformer

loss, interDAB Index of variables referring to the losses of the interconnecting dual

active bridge

loss, inv Index of variables referring to the losses of the inverter

loss, PEBB,  $1 - \xi$  Index of variables referring to the losses of medium voltage alternating

current power electronics building blocks connected to the

direct current-link

loss, PEBB,  $\xi$  Index of variables referring to the losses of medium voltage alternating

current power electronics building blocks connected to the low voltage

direct current feeder

loss,rr Index of variables referring to reverse recovery losses of a diode

loss, sw Index of variables referring to switching losses of an insulated gate

bipolar transistor

LVac Index of variables referring to a low voltage alternating current grid

LVac, CoM Index of variables referring the low voltage alternating current grid part

of the center of the mission profile

LVdc Index of variables referring to a low voltage direct current grid

LVdc, CoM Index of variables referring the low voltage direct current grid part of the

center of the mission profile

max Maximum value

MB Index of variables referring to the multibus

MB, dc – link Index of variables referring to the multibus cells connected to the

direct current-link

MB,LVdc Index of variables referring to the multibus cells connected to the low

voltage direct current feeder

mc Index of variables referring to a multichip version of the dual extended

Kalman filter based thermal digital twin

meas Index of variables referring to measurements

min Minimum value

MVac Index of variables referring to the medium voltage alternating current

grid

MVac, PEBB Index of variables referring to a medium voltage alternating current

power electronics building block

n Index of variables referring to a normally operated cell of a cascaded

H-bridge

obj Index of variables referring to an objective

obj, best Index of variables referring to a best value for an objective

obj, ref Index of variables referring to a reference objective off Index of variables referring to the turn-off of a transistor on Index of variables referring to the turn-on of a transistor

op, DEKF Index of variables referring to the mathematical operations in a dual

extended Kalman filter

op, PSO Index of variables referring to the mathematical operations in the

particle-swarm-optimization

opt Index of variables referring result of an optimization out Index of variables referring to the output of a system

P Index of variables referring to proportional part of a controller

ph Index of variables referring to one phase of an inverter

grid

pri Index of variables referring to the primary side of a transformer

pri, rms Index of variables referring to a root mean square value on the primary

side of a transformer

pri, rms, max Index of variables referring to a maximum root mean square value on

the primary side of a transformer

pk Peak value

PSO Index of variables referring to the particle-swarm-optimization PSO, best Index of variables referring to best values in the particle-swarm-

optimization

PSO, d Index of variables referring to derivative in the particle-swarm-

optimization

r Index of variables referring to rising behavior

R Index of variables referring to a resistor rated Index of variables referring to a rating

ref Reference variable index

res Index of variables referring to the resonant part of a controller rr Index of variables referring to the reverse recovery of a diode

s Index of variables referring to a source

sec Index of variables referring to the secondary side of a transformer

sec, rms Index of variables referring to a root mean square value on the secondary

side of a transformer

sec, rms, max Index of variables referring to a maximum root mean square value on

the secondary side of a transformer

stm Index of variables referring to the Steinmetz equation sw Index of variables referring to the switching of transistors

sw, CHB Index of variables referring to the switching of transistors in a cascaded

H-bridge

sw, DAB Index of variables referring to the switching of transistors in a dual

active bridge

sys Index of variables referring to the whole system

sys,in Index of variables referring to the total input of a system sys,loss Index of variables referring to the total losses of a system

sys, loss, FCC Index of variables referring to the total losses of a system calculated

assuming the flow conservation constraint

sys, loss, NCF Index of variables referring to the total losses of a system calculated

with non-conserved flows

sys, loss, rel Index of variables referring to the relative difference between total

losses of a system calculated under consideration of the flow

conservation constraint and without it

sys, out Index of variables referring to the total output of a system

T Index of variables referring to a transistor

th Index of variables referring to the thermal behavior

th, cr Index of variables referring to the thermal cross coupling effect

winding Index of variables referring to a winding 0 Index of variables referring to base value

$1-\xi$  Index of variables referring to the counterpart of the link ratio

## **Special symbols**

a Running index

A Set of arcs of a directed graph

$A_{\text{cond,pri}}$  Cross section of the conductor on the primary side of a transformer  $A_{\text{cond,sec}}$  Cross section of the conductor on the secondary side of a transformer

$A_{\text{core,win}}$  Area of one window in a transformer core  $A_{\text{cr}}$  Cross sectional area of a transformer core

b Running indexB Running index

$b_{\rm dia}$  Diameter of a bond wire

$B_{\rm pk}$  Peak value of the magnetic flux density of the transformer core material

without saturation

$B_{\rm PSO}$  Number of particles in the particle-swarm-optimization

c Coefficient in a formulaC Electrical capacitance

$C_{\text{cell}}$  Electrical capacitance of one cell of a cascaded H-bridge

$C_{\text{DAB,in}}$  Electrical input capacitance of a dual active bridge  $C_{\text{DAB,out}}$  Electrical output capacitance of a dual active bridge

$C_{\text{dc-link}}$  Electrical direct current-link capacitance

$c_{\text{form}}$  Coefficient which describes the impact of the applied electrical

waveforms on the saturation of the transformer core

$C_{\text{LVdc}}$  Electrical low voltage direct current grid capacitance

$c_{\rm PSO}$  Coefficient in the particle-swarm-optimization

$c_{\rm PSO,d}$  Weighting coefficient of the derivative part of the objective function in

the particle-swarm-optimization

$c_{\text{stm}}$  Coefficient of the Steinmetz equation

$C_{\rm th}$  Thermal capacitance

$\hat{C}_{th}$  Estimated thermal capacitance

$\hat{C}_{ ext{th}}^{ ext{conv}}$  Estimated thermal capacitance that converged to a steady value

DDual active bridge duty cycle $D_{\text{buck}}$ Buck converter duty cycle $d_{\text{exe}}$ Electrical simulation time step

$d_{PSO}$  Particle-swarm-optimization execution time step

$d_{\rm th}$  Thermal simulation time step

**E** Identity matrix

$E_{\rm off}$  Energy converted to heat during one turn-off of an insulated gate bipolar

transistor

$E_{\rm on}$  Energy converted to heat during one turn-on of an insulated gate bipolar

transistor

$E_{\rm rr}$  Energy converted to heat during one reverse recovery of a diode

f Frequency

**F** Jacobian matrix of system state functions

f(x, u) System state functions

$f_{ac}$  Alternating current fundamental frequency

$F_{\rm mc}$  Jacobian matrix of system state functions of the multichip version of

the dual extended Kalman filter based thermal digital twin

$f_{\rm obi}$  Objective function

$f_{\text{obj,best}}$  Best achieved objective function value

$f_{\text{obj,ref}}$  Reference objective function

$f_{\text{ref}}$  Reference frequency

$f_{\rm sw}$  Switching frequency of transistors

$f_{\text{sw.CHB}}$  Switching frequency of transistors in a cascaded H-bridge

Switching frequency of transistors in a dual active bridge  $f_{\rm sw,DAB}$

GDirected graph

$G_{\mathrm{DAB}}$ Voltage gain of a dual active bridge

H Jacobian matrix of system output functions

h(x)System output functions Height of a core window  $h_{\rm core,win}$

Alternating current Direct current

Estimated alternating current  $i^*$ Alternating reference current

$I_{\rm amp}^*$ Alternating reference current amplitude Amplitude of an alternating current  $I_{\rm amp}$

Collector current  $i_{\rm c}$ Diode current  $i_{\rm D}$ Inductor current  $i_{\rm L}$

Current of the inductance of a buck converter  $i_{L_{

m buck}}$

Constant load current  $I_{\rm load}$

Root mean square current of a load  $I_{\rm load,rms}$

Phase current  $i_{\rm ph}$

Primary side current of a transformer  $i_{\rm pri}$

Root mean square current on the primary side of a transformer  $I_{\rm pri,rms}$

Maximum root mean square current on the primary side of a transformer  $I_{\rm pri,rms,max}$

Secondary side current of a transformer  $i_{\rm sec}$

Root mean square current on the secondary side of a transformer  $I_{\text{sec,rms}}$  $I_{\text{sec,rms,max}}$ Maximum root mean square current on the secondary side of a

transformer

Transistor current  $i_{\rm T}$ j Running index Running index

$\boldsymbol{K}$ Kalman gain in a Kalman filter  $K_{\rm d}$ Damping gain of a controller  $K_{\rm P}$ Proportional gain of a controller  $K_{\rm res}$ Resonant gain of a controller

LInductance

$L_{\text{buck}}$ Buck converter inductance  $L_{\rm DAB}$ Dual active bridge inductance

Grid inductance  $L_{g}$

Length of the conductor on the primary side of a transformer  $l_{\rm pri}$

Locally best set of parameters of neighbor particles in the particle-swarm $l_{\mathrm{PSO,best}}$

optimization

$l_{\rm sec}$  Length of the conductor on the secondary side of a transformer

M Set of operation points of a hybrid grid mission profile

*m* Modulation signal

$m_{\text{CHB}}$  Modulation signal of a cascaded H-bridge

$m_{\text{cell}}$  Modulation signal a cell of a cascaded H-bridge

$m_{\rm cl}$  Modulation signal of the clamped operated cell of a cascaded H-bridge  $m_{\rm cl,1st}$  Modulation signal of the clamped operated cell of a cascaded H-bridge

for first harmonic clamped modulation method

$m_{\rm cl,3rd}$  Modulation signal of the clamped operated cell of a cascaded H-bridge

for third harmonic clamped modulation method

$m_{\rm icl}$  Modulation signal of the inverse clamped operated cell of a cascaded

H-bridge

$m_{\rm icl,1st}$  Modulation signal of the inverse clamped operated cell of a cascaded

H-bridge for first harmonic clamped modulation method

$m_{\rm icl,3rd}$  Modulation signal of the inverse clamped operated cell of a cascaded

H-bridge for third harmonic clamped modulation method

$m_{\rm n}$  Modulation signal of a normally operated cell of a cascaded H-bridge  $M_{\rm n}$  Amplitude modulation ratio of a normally operated cell of a cascaded

H-bridge

*n* Turns ratio of a transformer

$n_{\rm f}$  Counted number of cycles for specific thermal cycle

N Set of nodes of a directed graph

$N_{\text{cauer}}$  Number of chain elements of a Cauer network

N<sub>CHB</sub> Number of cells in one phase of a cascaded H-bridge

$N_{\rm f}$  Number of cycles to the failure of a device  $N_{\rm MB}$  Number of multibus cells in one phase

$N_{\rm MB,dc-link}$  Number of multibus cells connected to the direct current-link

$N_{\text{MB dc-link}}^{\text{CS}}$  Number of multibus cells connected to the direct current-link emulated

by current sources in the laboratory

$N_{\mathrm{MB,dc-link}}^{\mathrm{DAB}}$  Number of multibus cells connected to the direct current-link realized

by dual active bridges in the laboratory

$N_{\rm MB,LVdc}$  Number of multibus cells connected to the low voltage direct current

feeder

$N_{

m MB,LVdc}^{

m CS}$  Number of multibus cells connected to the low voltage direct current

feeder emulated by current sources in the laboratory

$N_{\rm MB\,I\,Vdc}^{\rm DAB}$  Number of multibus cells connected to the low voltage direct current

feeder realized by dual active bridges in the laboratory

$N_{\text{op,DEKF}}$  Number of mathematical operations in a dual extended Kalman filter  $N_{\text{op,PSO}}$  Number of mathematical operations in the particle-swarm-optimization

$N_{\rm pri}$  Number of windings on the primary side of a transformer

$N_{\rm sec}$  Number of windings on the secondary side of a transformer

$N_{\hat{x}}$  Number of states and estimated parameters in a dual extended Kalman

filter

$N_y$  Number of chip temperature measurements on the physical system in a

thermal digital twin

$O^-$  Estimated error covariance matrix before the correction step in a Kalman

filter

$O^+$  Estimated error covariance matrix after the correction step in a Kalman

filter

P Power flow

$P_{\text{aux}}$  Auxiliary variable for case distinction

$\bar{P}_{\text{cell}}$  Average power processed by one cell of a cascaded H-bridge

$P_{\text{CHB,ph}}$  Power processed in one phase of a cascaded H-bridge

$P_{\rm con}$  Conduction power losses

$\bar{P}_{\text{con.diode}}$  Average conduction losses of a diode

$\bar{P}_{\text{con,IGBT}}$  Average conduction losses of an insulated gate bipolar transistor

$P_{\text{CS,in}}$  Virtual input power of a current source

$P'_{CS,in}$  Compensated virtual input power of a current source

$P_{\text{CS.out}}$  Output power of a current source

$\bar{P}_{DAB}$  Average power processed by a dual active bridge

$P_{\text{DAB,in}}$  Input power of a dual active bridge

$P'_{\text{DAB.in}}$  Compensated input power of a dual active bridge

$P_{\text{DAB,IT}}$  Power of the interconnecting dual active bridge in the interconnected

topology

$P_{\mathrm{DAB,IT}}^{\mathrm{graphic}}$  Power of the interconnecting dual active bridge in the interconnected

topology that can be read from the low voltage power plane

$P_{\mathrm{DAB,IT}}^{\mathrm{max}}$  Maximum power of the interconnecting dual active bridge in the

interconnected topology

$P_{\mathrm{DAB,1T}}^{\mathrm{max,graphic}}$  Maximum power of the interconnecting dual active bridge in the

interconnected topology that can be read from the low voltage power

plane

$P_{\mathrm{DAB,NIT}}^{\mathrm{max}}$  Maximum power of the low voltage direct current dual active bridge in

the non-interconnected topology

$P_{\text{DAB,out}}$  Output power of a dual active bridge

$P_{\rm in}$  Input power of a system

$P_{\text{inv}}^{\text{max}}$  Maximum power of the inverter

$P_{\text{loss}}$  Power losses

$P_{loss}$ Power losses vector $\hat{P}_{loss}$ Estimated power losses $P_{loss.const}$ Constant power losses

$P_{\text{loss,core}}$  Transformer core losses

$P_{loss,Cu,pri}$  Copper losses of the conductor on the primary side of a transformer  $P_{loss,Cu,sec}$  Copper losses of the conductor on the secondary side of a transformer

*P*<sub>loss,interDAB</sub> Power losses of the interconnecting dual active bridge

$P_{\text{loss,inv}}$  Power losses of the inverter

$P_{\text{loss,PEBB},1-\xi}$  Power losses of medium voltage alternating current power electronics

building blocks connected to the direct current-link

$P_{\text{loss,PEBB},\xi}$  Power losses of medium voltage alternating current power electronics

building blocks connected to the low voltage direct current feeder

$\bar{P}_{\text{loss,rr}}$  Average reverse recovery losses of a diode

$\bar{P}_{loss,sw}$  Average switching losses of an insulated gate bipolar transistor

$P_{\text{LVac}}$  Active power of the low voltage alternating current grid

$P_{\text{LVac}}^{\text{max}}$  Maximum active power of the low voltage alternating current grid

$P_{\text{LVac,CoM}}$  Low voltage alternating current active power at the center of the mission

profile

$P_{\text{LVdc}}$  Power of the low voltage direct current grid

$P_{\text{LVdc}}^{\text{max}}$  Maximum power of the low voltage direct current grid

$P_{\text{LVdc,CoM}}$  Low voltage direct current power at the center of the mission profile

$P_{\text{MVac}}$  Active power of the medium voltage alternating current grid

$P_{\text{MVac,PEBB}}^{\text{max}}$  Maximum power of one medium voltage alternating current power

electronics building block

*P*<sub>out</sub> Output power of a system

$P_{\rm ph}$  Power processed by one phase of an inverter

$p_{\mathrm{PSO}}$  Set of parameters of a particle in the particle-swarm-optimization  $p_{\mathrm{PSO,best}}$  Set of parameters of a particle in the particle-swarm-optimization

which achieved a best objective function value of the particle

$P_{\rm R}$ Power consumed by a resistor $P_{\rm rated}$ Rated power of a converter $P_{\rm sys,in}$ Total input power of a system $P_{\rm sys,loss}$ Total power losses of a system

$P_{\text{sys,loss,FCC}}$  Total power losses of a system calculated assuming the flow conservation

constraint

$P_{\text{sys,loss,NCF}}$  Total power losses of a system calculated with non-conserved flows

$P_{\text{sys,out}}$  Total output power of a system

Q Noise covariance matrix of the system states in a Kalman filter

$Q_{\hat{C}_{th}}$  Entry of the noise covariance matrix of the system states in a Kalman

filter for an estimated thermal capacitance

$Q_{\rm mc}$  Noise covariance matrix of the system states in the multichip version of

the dual extended Kalman filter based thermal digital twin

$Q_{\text{mc},\hat{C}_{th}}$  Entry of the noise covariance matrix of the system states in the multichip

|                                   | version of the dual extended Kalman filter based thermal digital twin for  |

|-----------------------------------|----------------------------------------------------------------------------|

|                                   | an estimated thermal capacitance                                           |

| $Q_{ m mc,\hat{R}_{ m th}}$       | Entry of the noise covariance matrix of the system states in the multichip |

| $\sim$ IIIC, $R_{th}$             | version of the dual extended Kalman filter based thermal digital twin for  |

|                                   | an estimated thermal resistance                                            |

| $Q_{ m mc,\hat{R}_{ m th,cr}}$    | Entry of the noise covariance matrix of the system states in the multichip |

| $\sim$ IIIC, $R_{\rm th,cr}$      | version of the dual extended Kalman filter based thermal digital twin for  |

|                                   | an estimated thermal resistance which models a thermal cross coupling      |

|                                   | effect                                                                     |

| $Q_{mc.\hat{T}}$                  | Entry of the noise covariance matrix of the system states in the multichip |

| ≥mc,T                             | version of the dual extended Kalman filter based thermal digital twin for  |

|                                   | an estimated temperature                                                   |

| $Q_{ m mc,\hat{T}_{ m chip}}$     | Entry of the noise covariance matrix of the system states in the multichip |

| $\sim$ mc, $I_{\rm chip}$         | version of the dual extended Kalman filter based thermal digital twin for  |

|                                   | an estimated chip temperature                                              |

| $Q_{\hat{R}_{th}}$                | Entry of the noise covariance matrix of the system states in a Kalman      |

| $\sim \kappa_{ m th}$             | filter for an estimated thermal resistance                                 |

| $Q_{\hat{R}_{	ext{th,cr}}}$       | Entry of the noise covariance matrix of the system states in a Kalman      |

| ~ K <sub>th,cr</sub>              | filter for an estimated thermal resistance which models a thermal cross    |

|                                   | coupling effect                                                            |

| $Q_{\hat{T}}$                     | Entry of the noise covariance matrix of the system states in a Kalman      |

| •                                 | filter for an estimated temperature                                        |

| $Q_{\hat{T}_{	ext{chip}}}$        | Entry of the noise covariance matrix of the system states in a Kalman      |

| СШР                               | filter for an estimated chip temperature                                   |

| R                                 | Electrical resistance                                                      |

| $R_{\rm ac}$                      | Electrical alternating current resistance                                  |

| $R_{ m cell}$                     | Electrical load resistance of one cell of a cascaded H-bridge              |

| $R_{\mathrm{Cu,pri}}$             | Resistance of conductor copper on the primary side of a transformer        |

| $R_{\mathrm{Cu,sec}}$             | Resistance of conductor copper on the secondary side of a transformer      |

| $R_{ m dc}$                       | Electrical alternating current resistance                                  |

| $R_{\text{load}}$                 | Electrical load resistance                                                 |

| $r_{\rm PSO}$                     | Randomly generated number in the particle-swarm-optimization               |

| $R_{ m th}$                       | Thermal resistance                                                         |

| $\hat{R}_{	ext{th}}$              | Estimated thermal resistance                                               |

| $\hat{R}_{	ext{th}}^{	ext{conv}}$ | Estimated thermal resistance that converged to a steady value              |

| $R_{\mathrm{th,cr}}$              | Thermal resistance modeling a thermal cross coupling effect                |

| $\hat{R}_{	ext{th,cr}}$           | Estimated thermal resistance modeling a thermal cross coupling effect      |

| $r_{ m winding}$                  | Radius of a winding                                                        |

| S                                 | Variable of the Laplace transformation                                     |

S Noise covariance matrix of the measurements in a Kalman filter

$s_{

m meas}$  Measurement noise

$S_{T_{chin}}$  Entry of noise covariance matrix of the measurements in a Kalman filter

for a chip temperature

*t* Time

$t_{\rm r}$  Time of the temperature rise (heating time)

Temperature

$\hat{T}$  Estimated temperature

$\hat{T}$  Vector of estimated temperatures

$T_{\rm a}$  Ambient temperature  $T_{\rm chip}$  Chip temperature

$\hat{T}_{\text{chip}}$  Estimated chip temperature

$T_{C_{th}}$  Temperature of a thermal capacitor

$T_{\rm i}$  Junction temperature

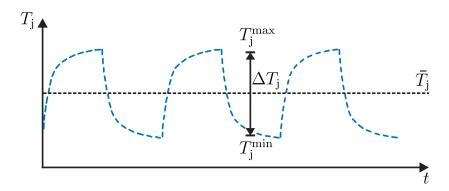

$ar{T_j}$  Average junction temperature  $T_j^{ ext{max}}$  Maximum junction temperature  $T_j^{ ext{min}}$  Minimum junction temperature  $ar{T_j}$  Average junction temperature  $T_j^{ ext{max}}$  Maximum junction temperature  $T_j^{ ext{min}}$  Minimum junction temperature

$T_{\rm ref}$  Reference temperature

$T_{\rm ref}$  Reference temperature vector

*u* Inputs of a system

$u_{

m mc}$  Inputs of the multichip version of the dual extended Kalman filter based

thermal digital twin

v Voltage

$\hat{v}$  Estimated voltage

v<sub>ac</sub> Alternating current voltage, grid voltage

$V_{\text{ac,rms,ph}}$  Root mean square alternating current voltage between line and neutral

conductor

$V_{\rm block}$  Blocking state voltage of a semiconductor

$V_{\text{block,ref}}$  Reference value of the blocking state voltage of a semiconductor

$V_{\rm cc}$  Voltage between collector and emitter in blocking state

$v_{ce}$  Voltage between collector and emitter

$v_{\text{cell}}$  Alternating current voltage of one cell of a cascaded H-bridge

$V_{\text{ce(sat)}}$  Saturation voltage between collector and emitter  $v_{\text{CHB}}$  Alternating current voltage of a cascaded H-bridge

$V_{\text{CHB.dc}}$  Direct current part of the alternating current voltage of a cascaded

H-bridge

$V_{\text{CHB,rms}}$  Root mean square of the alternating current voltage of a cascaded

H-bridge

V<sub>CHB.rms.fund</sub> Root mean square of the alternating voltage at fundamental frequency of

a cascaded H-bridge

$V_{\rm core}$  Volume of the core of a transformer

$v_{\rm D}$  Forward voltage of a diode  $V_{

m dc}$  Direct current voltage

$V_{\rm dc}^*$  Direct current reference voltage

$V_{

m dc}^{

m filt}$  Direct current voltage that a smoothing filter has been applied to

$V_{\text{dc-link}}$  Direct current-link voltage

$V_{

m dc-link}^*$  Direct current-link reference voltage  $v_{

m ge}$  Voltage between gate and emitter

$V_{\rm ge(th)}$  Threshold voltage between gate and emitter

$V_{\rm gg}$  Designed operation voltage between gate and emitter

$V_{\rm in}$  Input direct current voltage

v<sub>L</sub> Inductor voltage

$v_{L_{\text{buck}}}$  Voltage of the inductance of a buck converter

$v_{L_{\text{DAR}}}$  Voltage of the inductance of a dual active bridge converter

$V_{\text{link}}$  Direct current voltage of a link between converters

$V_{\text{load}}$  Direct current load voltage

$V_{\text{LVdc}}$  Low voltage direct current grid voltage

$V_{\rm LVdc}^*$  Low voltage direct current grid reference voltage

V<sub>out</sub> Output direct current voltage

$V_{\text{pri}}$  Root mean square voltage on the primary side of a transformer  $v_{\text{PSO}}$  Set of parameter velocities of a particle in the particle-swarm-

optimization

$V_{\text{rated}}$  Rated voltage of semiconductor

*v*<sub>ref</sub> Reference voltage

$V_{\rm s}$  Voltage of a direct current source

$V_{\rm sec}$  Root mean square voltage on the secondary side of a transformer

W Set of weights of the arcs in a directed graph

w Process noise

$w_{\rm core,win}$  Width of a core window

x States of a system

$oldsymbol{x}_0$  Initial states of a system  $oldsymbol{\hat{x}}$  Estimated states of a system

$\hat{x}_{

m mc}$  Estimated states of the multichip version of the dual extended Kalman

filter based thermal digital twin

$\hat{x}^-$  Estimated states of a system before the correction step in a Kalman filter  $\hat{x}^+$  Estimated states of a system after the correction step in a Kalman filter

y Outputs of a system

$\hat{y}$  Estimated outputs of a system

$\hat{y}_{mc}$  Estimated outputs of the multichip version of the dual extended Kalman

filter based thermal digital twin

$Z_{\text{th}}$  Thermal impedance

$\dot{Z}_{th}$  Time derivative of the thermal impedance

$\dot{Z}_{th}$  Time derivative of the thermal impedance matrix

$\alpha$  Unspecific angle

$\gamma$  Distortion factor of the coordinate transformation in the low voltage

power plane by the link ratio for the interconnected topology

$\Delta P_{\text{sys,loss,rel}}$  Relative difference between total power losses of a system calculated

under consideration of the flow conservation constraint and without it

$\Delta T$  Temperature difference

$\Delta T_i$  Junction temperature swing

$\eta$  Efficiency

$\eta_{\rm DAB}$  Efficiency of a dual active bridge

$\eta_{j,b}$  Efficiency for backward power flow in a converter described by node j in

a directed graph

$\eta_{j,f}$  Efficiency for forward power flow in a converter described by node j in a

directed graph

$\eta_{\rm sys}$  Efficiency of the whole system

$\bar{\eta}_{\rm sys}$  Average weighted efficiency of the whole system

θ Angle in a periodic signal

$\xi$  Link ratio of the interconnected topology

$\xi_{\text{AWE}}$  Link ratio chosen according to the average weighted system efficiency  $\xi_{\text{CoM}}$  Link ratio chosen according to the location of the center of the mission

profile

$\xi_{\text{opt}}$  Link ratio of the interconnected topology to provide optimal efficiency

$\rho_{\text{Cu}}$  Specific resistance of copper

au Specific time period  $au_{th}$  Thermal time constant

$\phi$  Clamping angle

$\varphi$  Phase shift of a dual active bridge

$\varphi_{i}$  Phase shift of the interconnecting dual active bridge

$\varphi_{\text{LVac}}$  Phase shift between voltage and current in a low voltage alternating

current grid

$\varphi_{\text{MVac}}$  Phase shift between voltage and current in a medium voltage alternating

current grid

$\varphi_{1-\xi}$  Angle in the low voltage power plane connected to the counterpart of

the link ratio

$\omega$  Angular frequency

$\omega_0$  Base angular frequency  $\omega_{\rm g}$  Grid angular frequency

$\omega_{\rm PSO}$  Inertia weight in the particle-swarm-optimization

#### **Abbreviations**

ac Alternating current

ATC Active thermal control

ATR Aktive thermische Regelung

AWE Average weighted system efficiency

BESS Battery energy storage system

c Converter node in a directed graph

CHB Cascaded H-bridge

CM Condition monitoring

CoM Center of the mission profile

CTE Coefficient of thermal expansion

D Diode

DAB Dual active bridge dc Direct current

DCB Direct copper bond

DEKF Dual extended Kalman filter

DSP Digital signal processor

DT Digital twin

E End/sink node in a directed graph

EE Erneuerbare Energiequellen

EV Electric vehicle

FCC Flow conservation constraint

HIL Hardware-in-the-loop

IGBT Insulated gate bipolar transistor

IPOP Input parallel output parallel

ISOP Input series output parallel

IT Interconnected topology

L1 First line of an alternating current three phase grid

L2 Second line of an alternating current three phase grid

L3 Third line of an alternating current three phase grid

LEF Ladesysteme für Elektrofahrzeuge

LV Low voltage

LVac Low voltage alternating current

LVdc Low voltage direct current MAB Multiple active bridge

MV Medium voltage

MVac Medium voltage alternating current

N Neutral line of a grid NCF Non-conserved flows

NIT Non-interconnected topology

NP Neutral point

PE Power electronics

PEBB Power electronics building block

PI Proportional-integral

PLL Phase-locked loop

PR Proportional-resonant

PSO Particle-swarm-optimization

p.u. Per unit

PV Photo voltaic

PWM Pulse width modulation

RES Renewable energy sources

RMS Root mean square

RR Reverse recovery

RTS Real-time simulation

RUL Remaining useful lifetime

S Source node in a directed graph

SOGI Second-order generalized integrator

SoH State of health

ST Smart transformer

SST Solid state transformer

T Transistor

THD Total harmonic distortion

TSEP Temperature sensitive electrical parameter

v Virtual node in a directed graph

ZVS Zero voltage switching

#### 1. Introduction

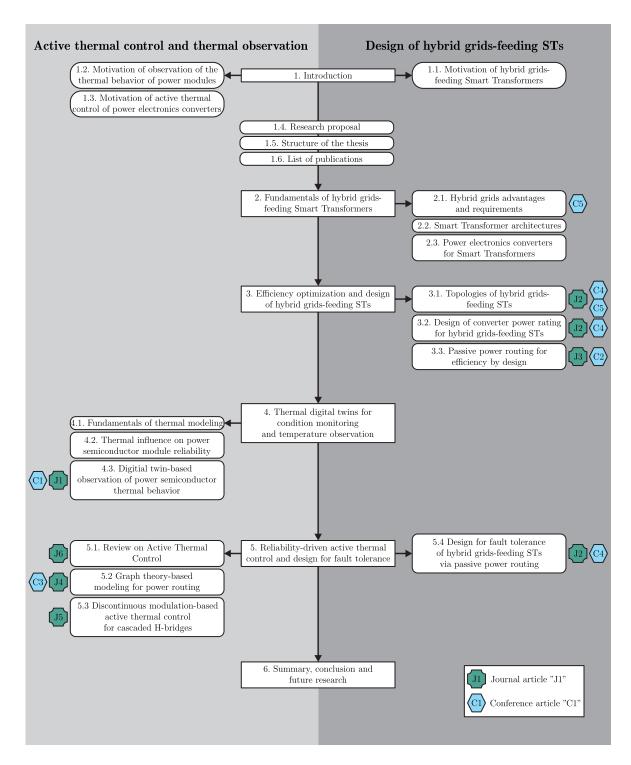

This chapter introduces the motivation of the main directions in this work. The first main direction is the *design of hybrid grids-feeding Smart Transformers*, which is related to the efficiency of power electronics. The second main direction is *active thermal control and thermal observation*, which is composed of two directions: *observation of the thermal behavior of power modules* and *active thermal control of power electronics converters*. This second main direction is related to the reliability of power electronics.

The efficiency and reliability are essential for power electronics applications. The research proposal of this work - given after the motivation - contains three targets, which are:

- Design optimization of hybrid grids-feeding Smart Transformers for improved efficiency and reduced converter loading,

- Development of thermal digital twin approaches for observation of the thermal behavior of power modules,

- Elaboration on active thermal control methods for hybrid grids-feeding Smart Transformers.

Afterwards, the structure of the work in terms of chapters, sections, and related publications is presented and an overview of the content of the different chapters is given. Finally, the publications associated with this work are listed.

### 1.1. Motivation of hybrid grids-feeding Smart Transformers

The increasing integration of distributed renewable energy sources (RES) and electric vehicle (EV) charging systems into the power grid poses challenges in handling high generation and demand variability [1–3]. Hybrid ac/dc distribution systems are considered as a major possibility in order to facilitate the integration of the needed flexibility in the future distribution grid [4, 5]. The utilization of hybrid distribution systems - which embed dc grids inside the existing ac grid structure - could combine an efficient integration of RES, EV charging stations, and battery energy storage systems (BESS) [6] via dc grids with the established protection mechanisms of ac grids.

The provision of hybrid distribution grids can be realized via power electronics-based transformers [7], which are able to provide connectivity to dc grids as well as to build the joint between ac grids on medium and low voltage levels. Furthermore, the concept of the Smart Transformer (ST) can play an important role for the provision and the management of hybrid distribution grids [8, 9]. This concept of the ST is defined in [10] as:

# The ST is a power electronics-based transformer with advanced control functionalities to allow flexible ac and dc distributions, and the possibility to provide grid services.

One service the ST can provide for the grids is to improve the voltage profile of the medium voltage (MV) grid by injecting reactive power via the converter connected to the MV grid [11]. Herein, using an active power control of the low voltage (LV) grids fed by the ST - utilizing the voltage-dependency of the loads - leads to a lower voltage drop in the MV grid due to the reduced active current, and at the same time more reactive power can be injected via the converter connected to the MV grid. The load control in the LV grids fed by the ST can also be used for primary frequency regulation in the MV grid [12]. Herein, the possibility to decrease or increase the consumption in the LV grids is utilized as a power reserve during frequency variations. Further, the load control in the ST-fed LV grids can be used to reduce the consumption in order to prevent an overload of the ST or to apply a soft load reduction of all consumers to mitigate the execution of load shedding [13].

## 1.2. Motivation of observation of the thermal behavior of power modules

The reliability of power electronics systems is crucial in order to guarantee a high availability of them in failure-critical applications - e.g. more electric aircrafts [14] - and future power electronics-based grids [10]. To guarantee a high availability of power electronics applications, the reliability of power modules is essential, because the power semiconductors are - besides the capacitors - main failure components in power electronics systems [15, 16]. Monitoring the health condition of power modules [15] enables the application of prognostic maintenance [17], which can reduce the downtime of the systems due to power module failure-caused unscheduled maintenance.

Thermo-mechanical stress of power modules due to varying system utilization is a major factor causing their degradation [17]. Furthermore, the thermal behavior of power modules changes with degradation and can be used to monitor their health condition [15]. The observation of the thermal behavior of power modules allows to monitor the temperatures in order to evaluate if the converter is within safe operation conditions or might be damaged by overtemperatures. Detecting over-temperatures is the first step to initiate measures in order to protect the power modules from harm. Another possibility that is enabled by the observation of the thermal behavior of power modules is the provision of the temperature as essential input for lifetime models in order to estimate their state of health and the remaining useful lifetime [18]. The estimation of the state of health and the remaining useful lifetime allows to adjust the maintenance schedule in order to increase the reliability of power modules. An additional way, that could be combined with the estimation made by lifetime models, is to

carry out condition monitoring based on the thermal behavior in order to access the state of health of power modules. Further, observing the thermal behavior of power modules can provide the temperature as a feedback signal for active thermal control algorithms.

## 1.3. Motivation of active thermal control of power electronics converters

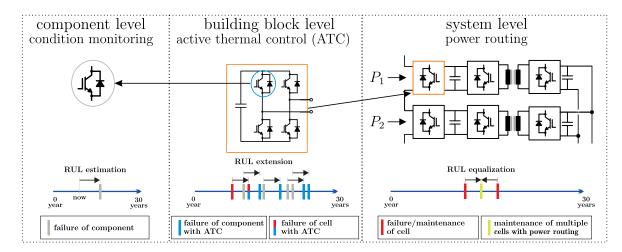

As presented in the motivation of observation of the thermal behavior of power modules, the reliability of power modules is important and thermo-mechanical stress leads to their degradation. Beyond monitoring the health condition of power modules, actively influencing the thermo-mechanical stress that power modules are exposed to by active thermal control of power electronics converters can be desirable. This is especially the case for power electronics systems which are costly to reach for maintenance due to a difficult accessibility, for example subsea applications [19] or offshore wind power farms [20].

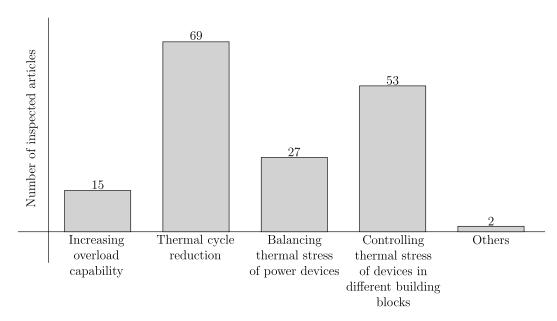

Active thermal control methods approach to increase the reliability of power modules in power electronics converters in different ways [21]. One possibility is to apply active thermal control methods which reduce the losses within power modules while operating close to the thermal limits of the power electronics converters. This can enable a safe operation of power electronics converters close to their limits and increase their overload capability.

Another way of trying to increase the reliability and the lifetime of power modules via active thermal control methods is their application for thermal cycle reduction. Herein, the losses of the power module are reduced for temperatures above the mean temperature and increased for temperatures below the mean temperature. By reducing the temperature swings in this way, the damage done to the power module is lower and their lifetime could be prolonged [17].

Further, active thermal control methods can be implemented in order to balance the thermal stress of power devices in multichip modules, parallel power modules, or in special topologies with redundant switching states such as active neutral point clamped converters. Balancing the thermal stress can benefit a uniform degradation of the power semiconductor devices and relieve degraded devices with high temperatures from thermal stress [22–24].

Another way active thermal control methods can try to improve the reliability of power electronics converter systems is to control the thermal stress of devices in different building blocks. Herein, the thermal stress is relocated from further degraded system parts to less degraded system parts, which attempts to increase the reliability of the power electronics converter system and reduce the required maintenance appointments [25].

#### 1.4. Research proposal

The targets of the research proposal of this work are the following ones:

Target I: Optimization of the design of hybrid grids-feeding Smart Transformers for improved efficiency and reduced converter loading

The first research objective is to optimize the design of ST topologies for the provision of hybrid distribution grids. The design of the ST topologies should consider requirements found for hybrid ac/dc distribution/micro grids. An adjustable configuration of the ST topologies should allow to optimize the ST efficiency according to a given mission profile of the hybrid distribution grid. Adjusting the configuration of the ST topologies should also be able to provide a reduced converter loading for a given mission profile of the hybrid distribution grid. This reduced converter loading could be used to downsize the converter power rating, insert additional failure tolerance for the ST, or combine these two.

Target II: Development of thermal digital twin approaches for observation of the thermal behavior of power modules

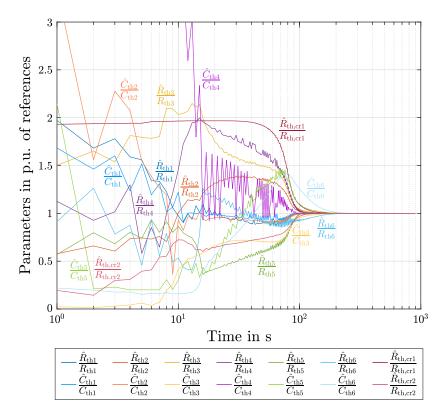

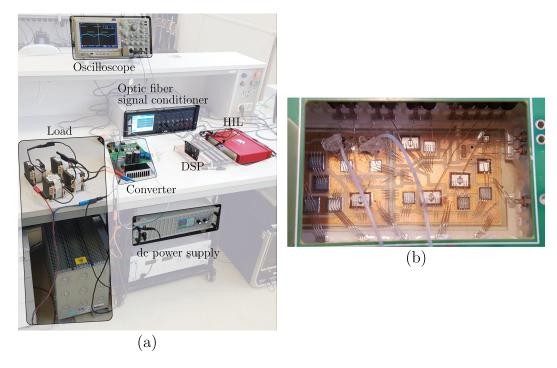

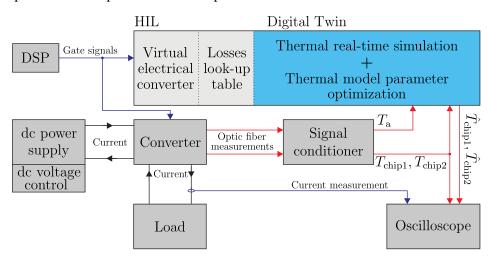

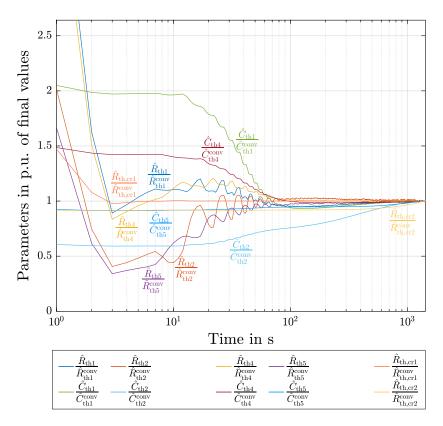

The second research objective is the development of thermal digital twin (DT) approaches of power modules based on different methods. The thermal digital twin approaches should be able to observe the thermal behavior of power modules, which could be checked by identifying the thermal parameters of a digital reference model in a real time simulation without previous knowledge about these parameters. The developed thermal DT approaches should be compared for suitable criteria, which consider possible advantages and disadvantages of their application in the field as well as efforts required for further research on the approaches. The more appropriate thermal DT approach should be extended for the observation of multiple semiconductor chips with thermal cross coupling effects inside a power module. It should be verified that this thermal DT approach for multiple semiconductor chips is able to replicate the temperatures of a real power module in the laboratory.

Target III: Elaboration on active thermal control methods for hybrid grids-feeding Smart Transformers

The third research objective is to elaborate on active thermal control (ATC) methods for hybrid grids-feeding STs. By reviewing ATC methods used for power electronics converters, it should be evaluated which methods are most relevant for the application case ST. Those methods identified should be elaborated to be made suitable for the requirements of the hybrid grids-feeding ST topologies that should be found in the first objective of this work. A simultaneous and independent operation of the methods in the ST should be considered.

Fig. 1.1: Structure of the work with related publications.

#### 1.5. Structure of this work

The structure of this work in terms of chapters, sections, and related publications is illustrated in Fig. 1.1.

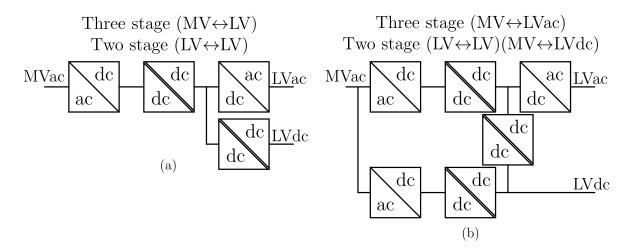

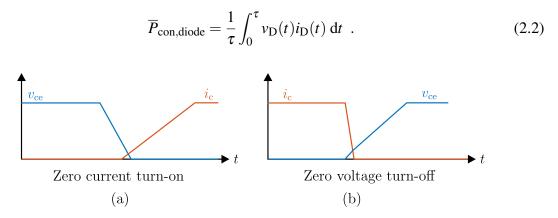

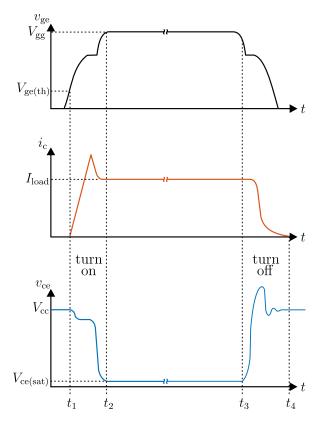

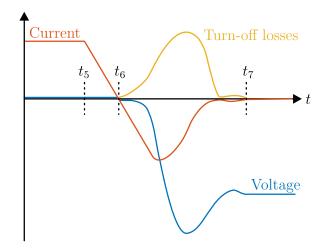

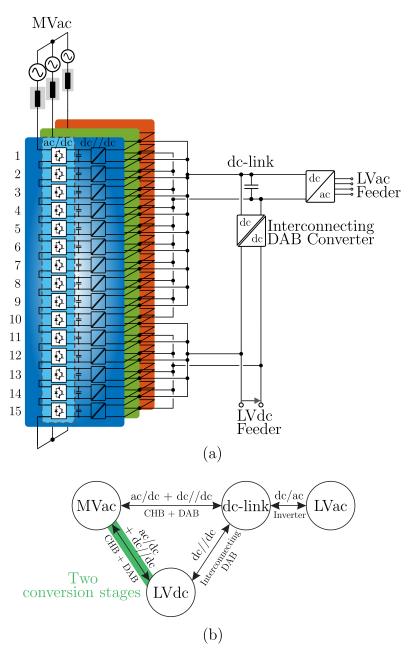

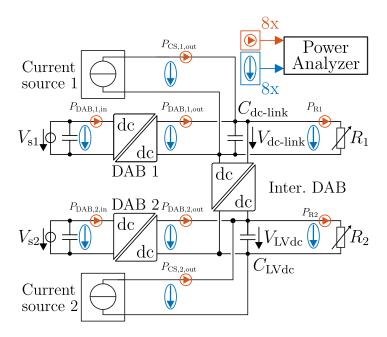

**Chapter 2** is structured as follows: based on [26], advantages and requirements of hybrid grids are presented in Section 2.1. Section 2.2 shows ST architectures and discusses which of them can fulfill the requirements of hybrid grids. The basics of loss calculation and the

power electronics converters used to realize ST topologies from the architectures in this work are introduced in Section 2.3. A summary and the conclusions of Chapter 2 can be found in Section 2.4.

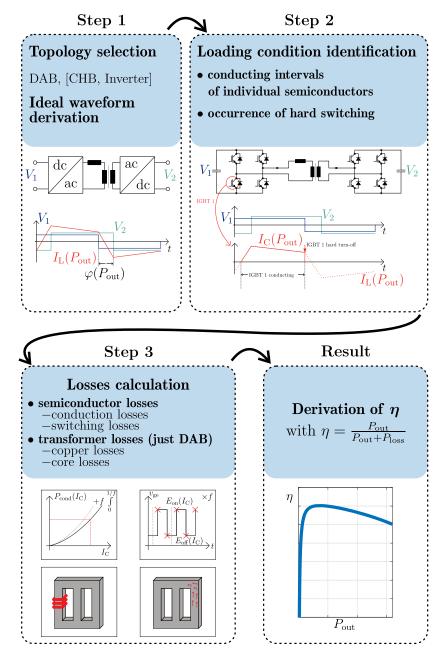

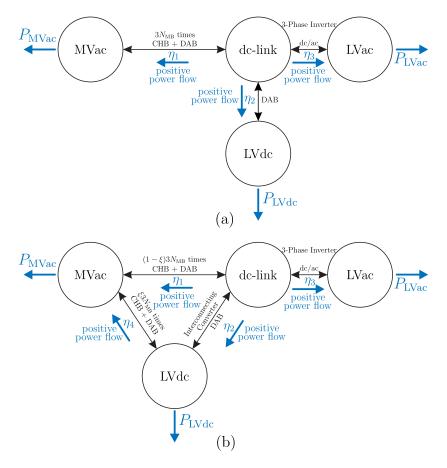

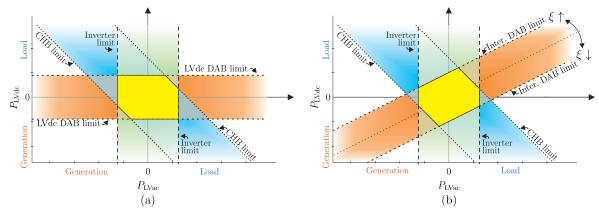

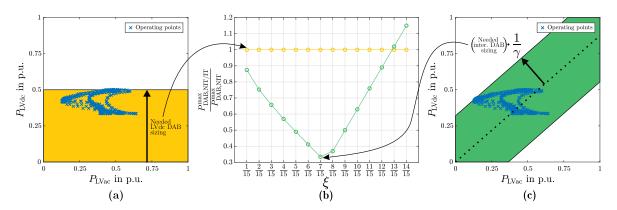

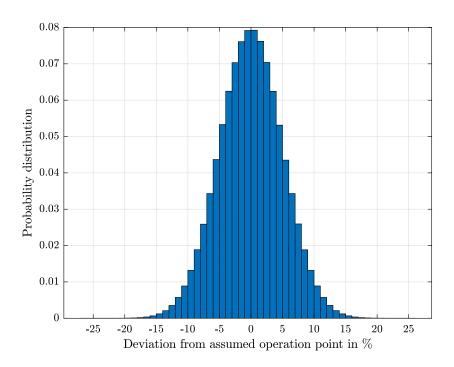

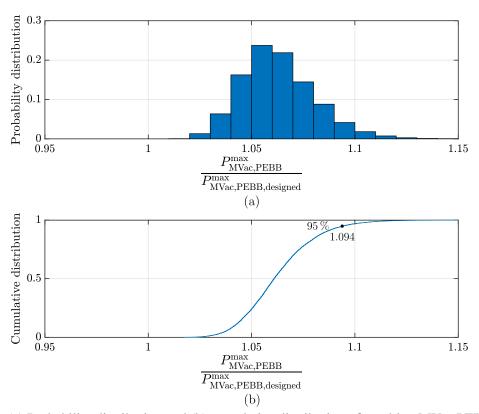

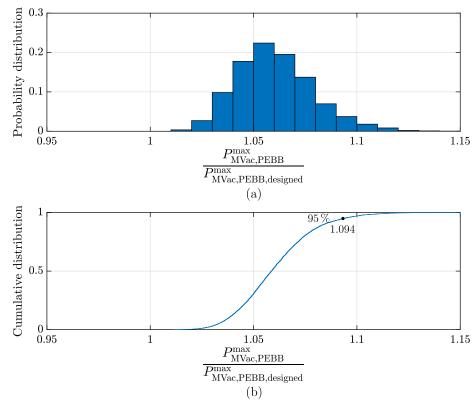

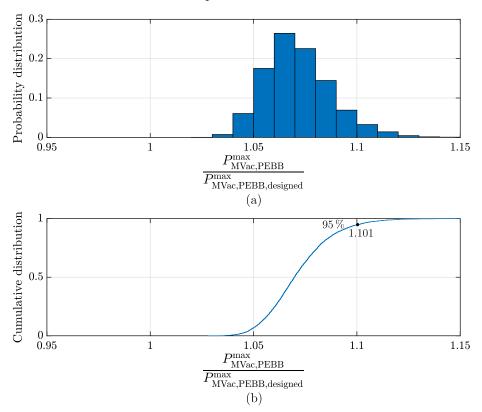

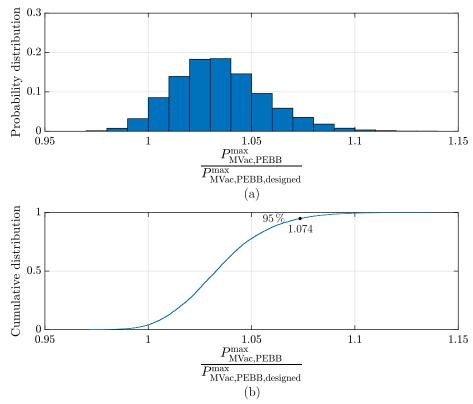

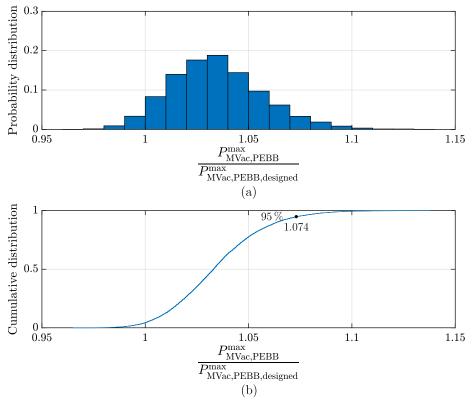

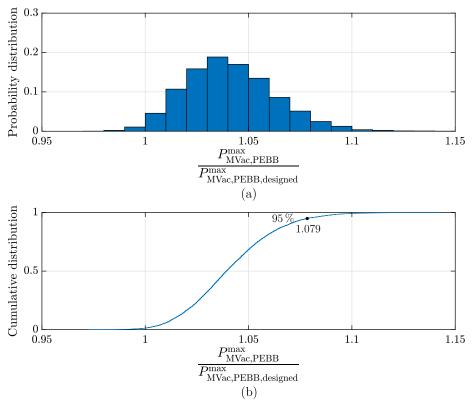

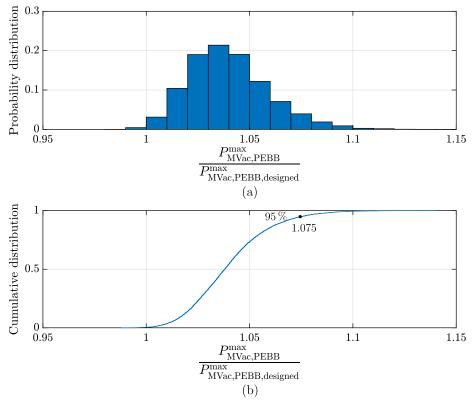

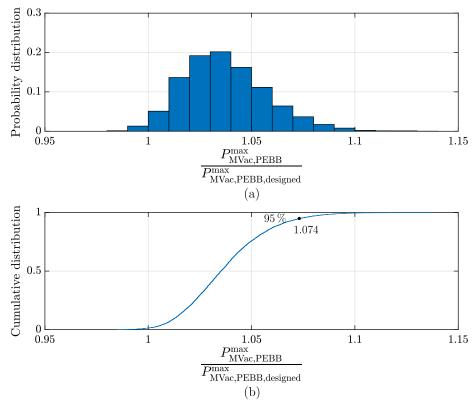

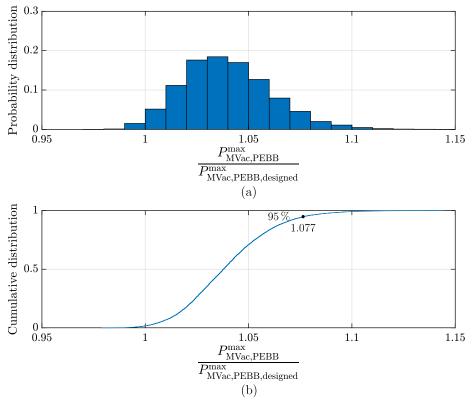

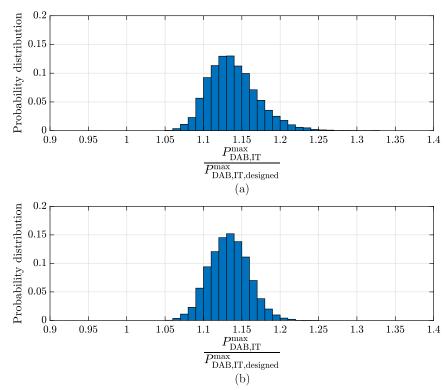

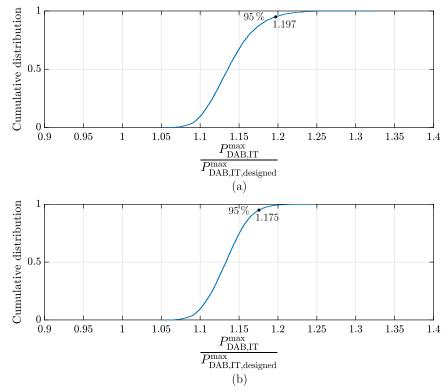

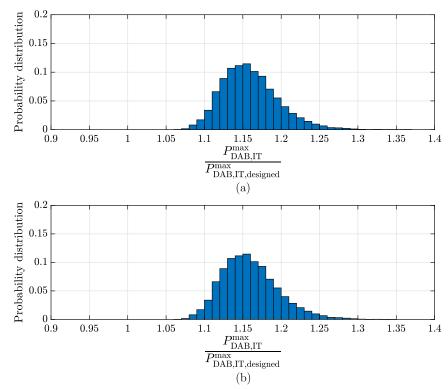

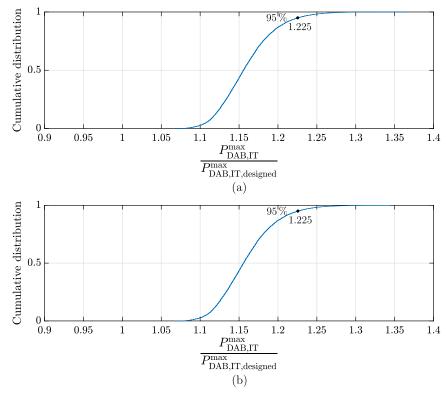

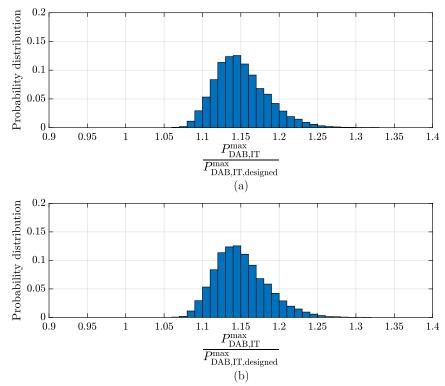

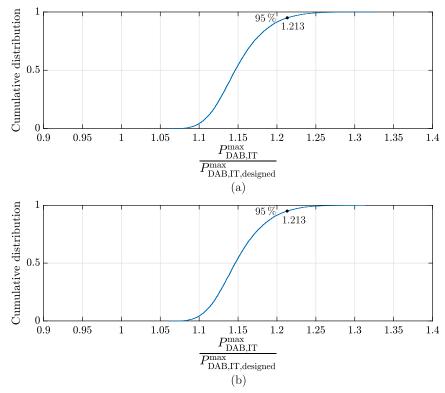

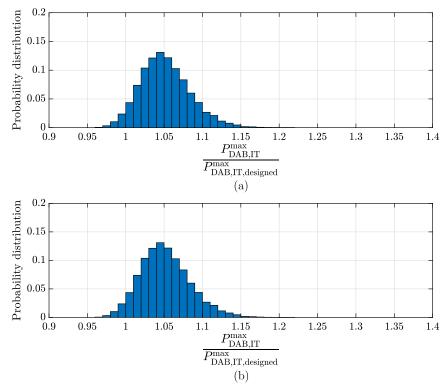

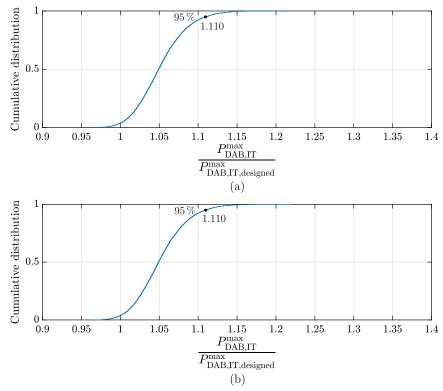

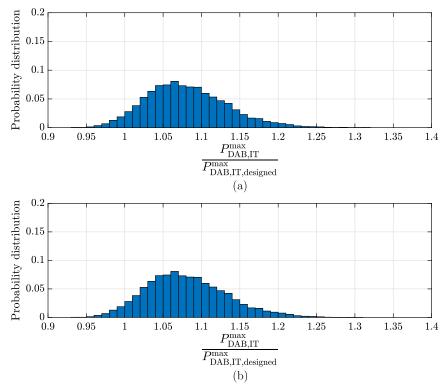

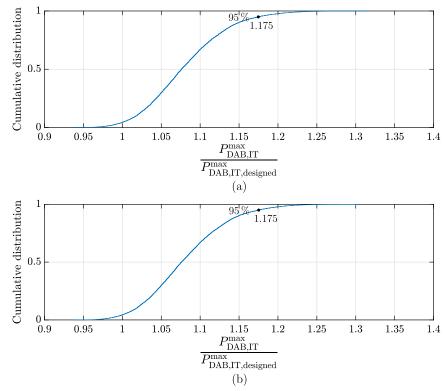

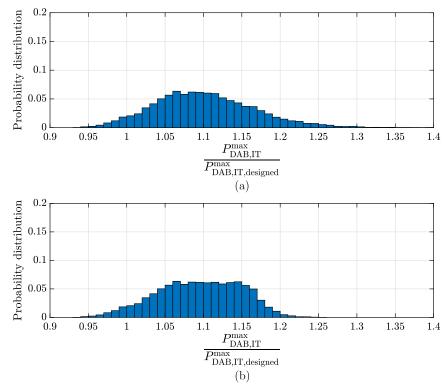

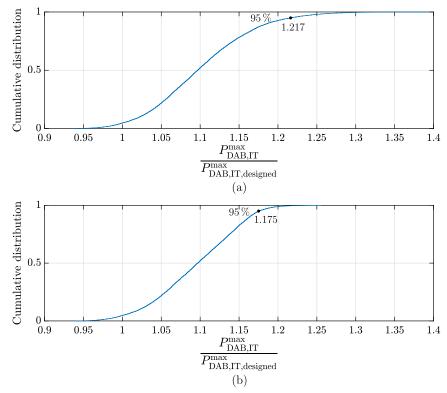

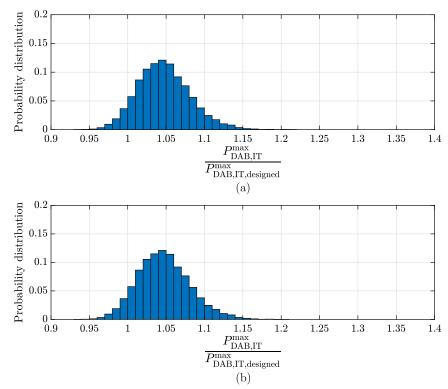

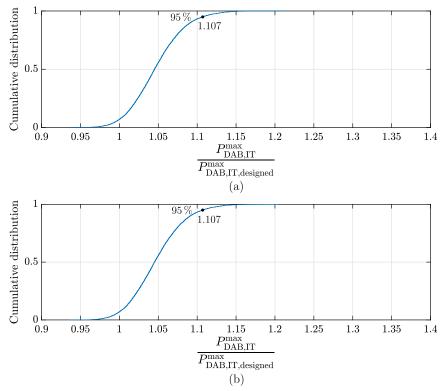

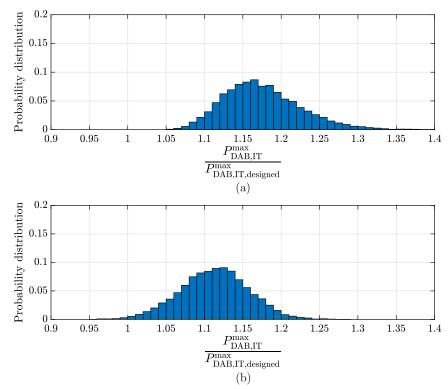

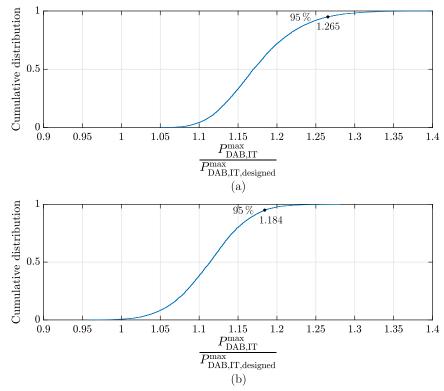

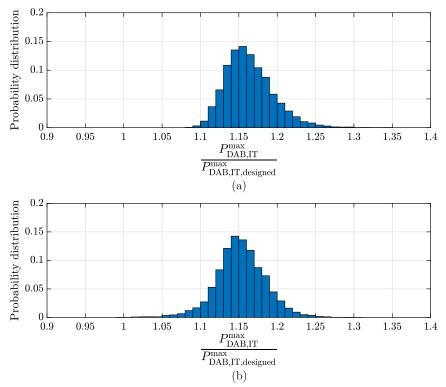

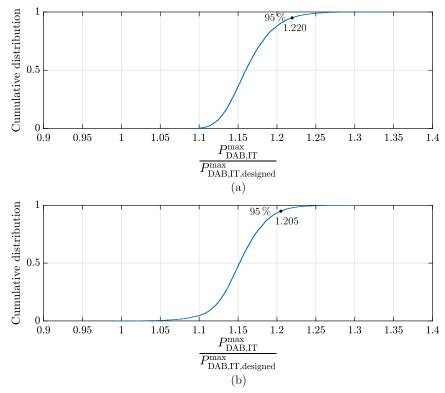

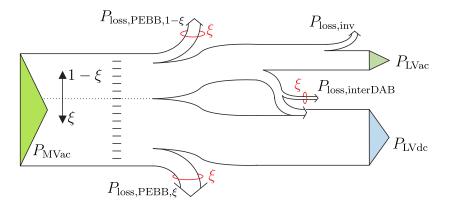

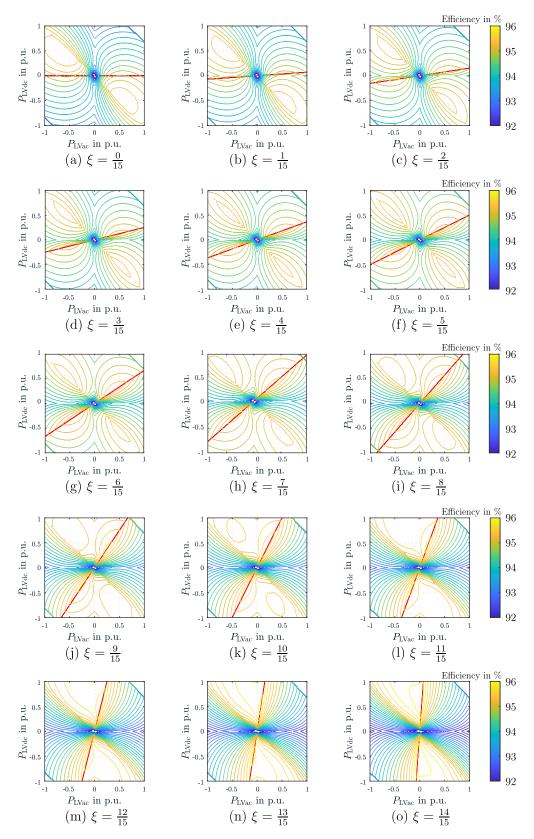

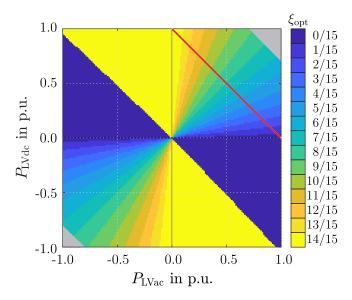

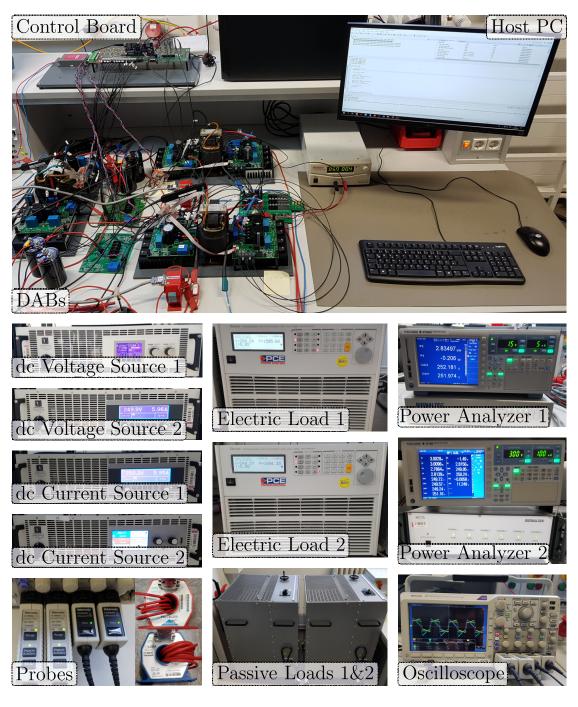

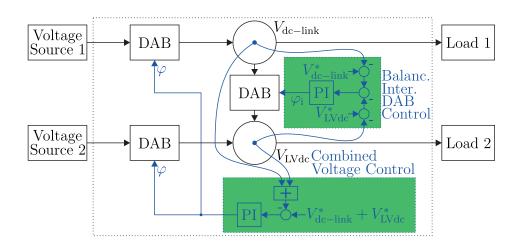

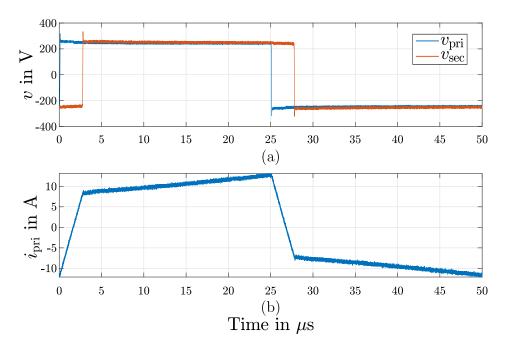

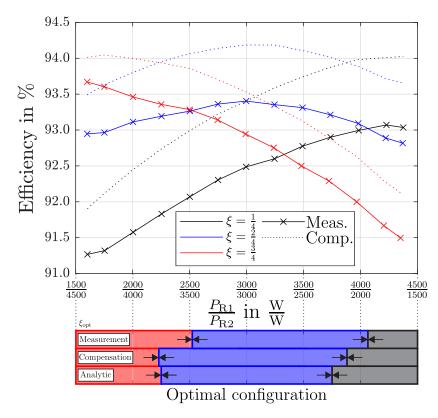

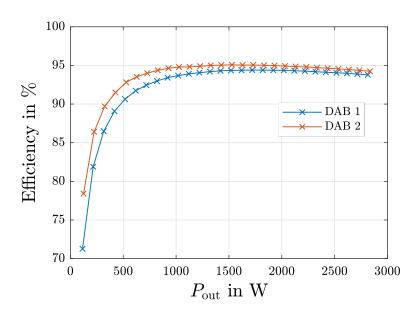

Chapter 3 is structured as follows: the topologies presented in [26–28], which are the base for the optimal configuration of the hybrid grids-feeding ST, are introduced in Section 3.1. Based on [27, 28], Section 3.2 proposes a mission profile-based design procedure for the power rating of all converters in the topologies, examines the opportunity to downsize one specific converter, and a Monte Carlo-based sensitivity analysis of the derived converter power ratings against deviations of the assumed mission profiles is executed. In Section 3.3, the efficiency influence of the configuration in one of the basis topologies is presented, two approaches to derive this configuration for optimal efficiency of mission profiles are proposed according to [29, 30], and a laboratory validation of the efficiency influence of the configuration choice is given. A summary and the conclusions of Chapter 3 can be found in Section 3.4.

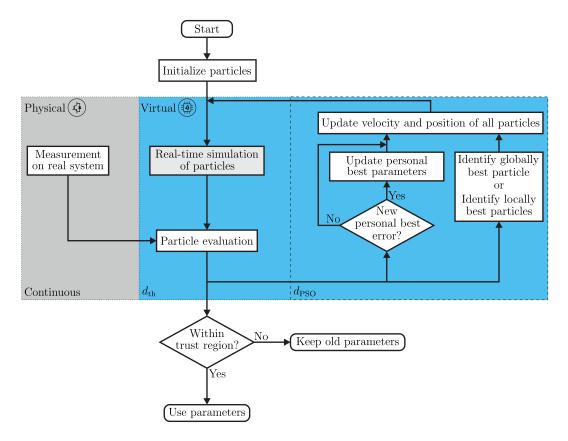

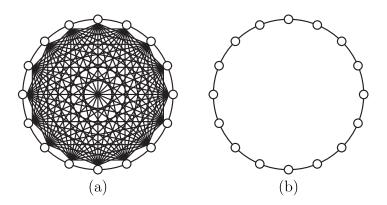

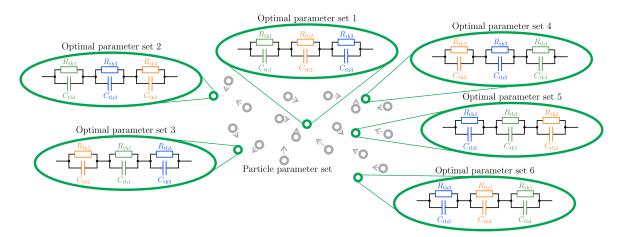

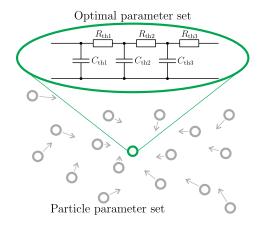

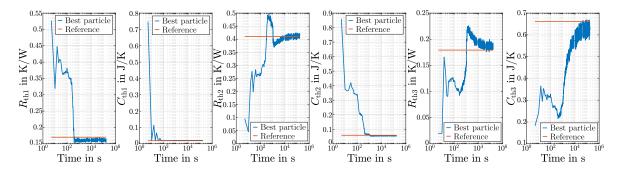

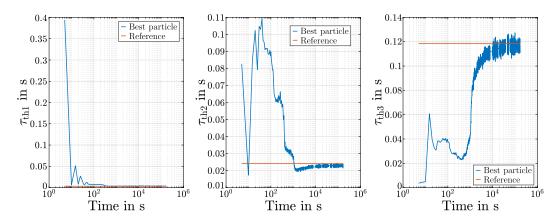

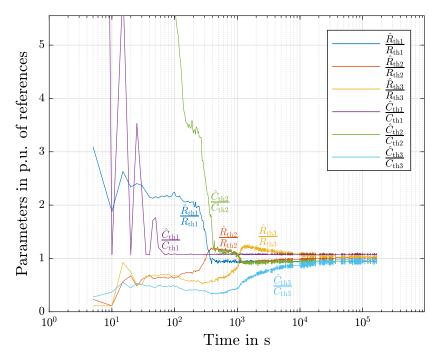

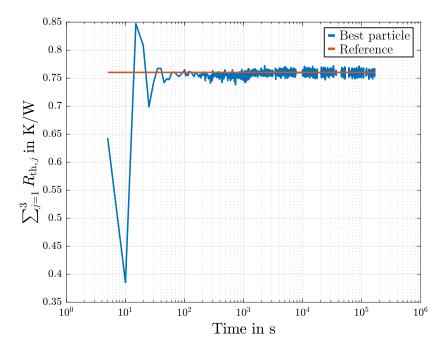

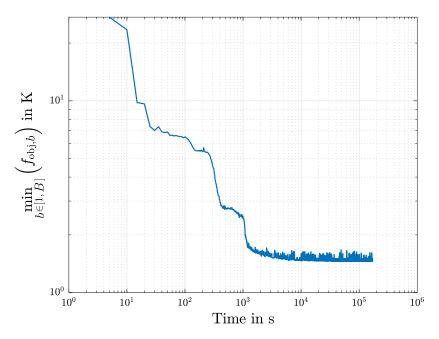

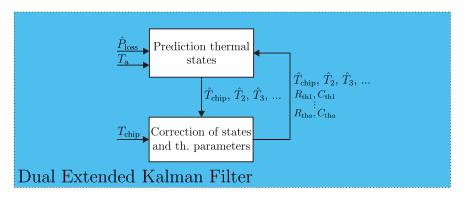

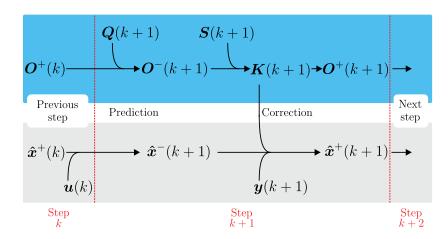

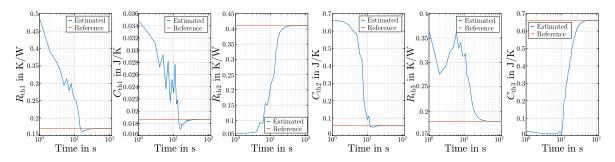

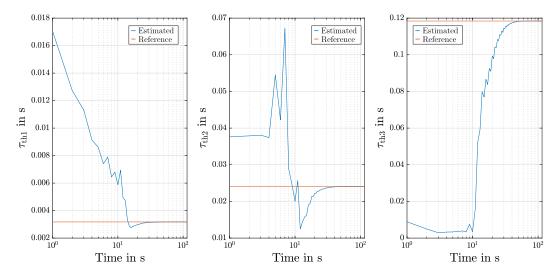

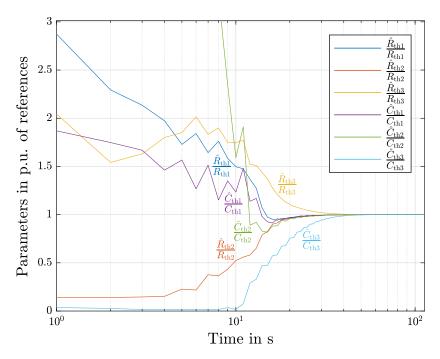

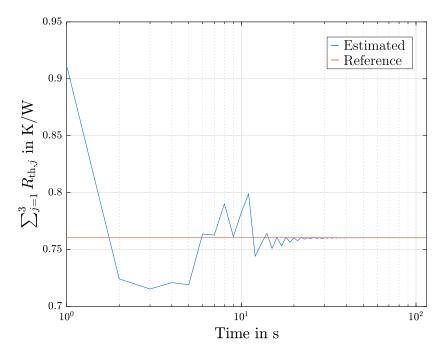

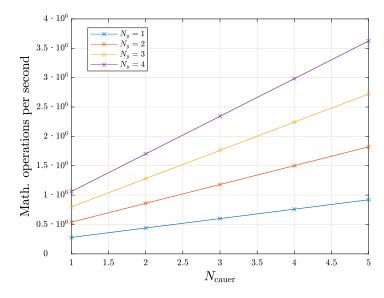

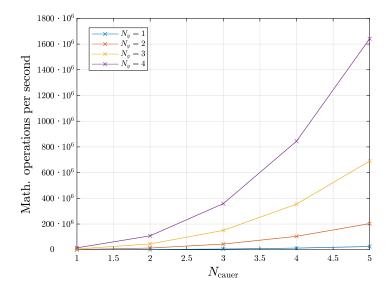

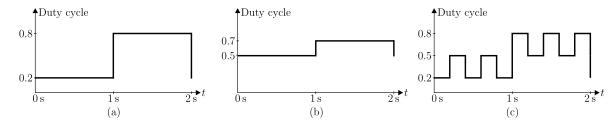

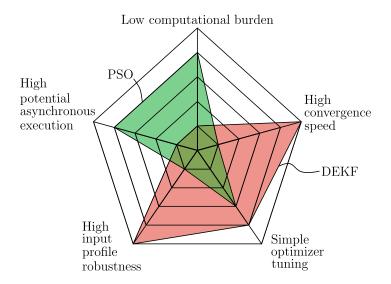

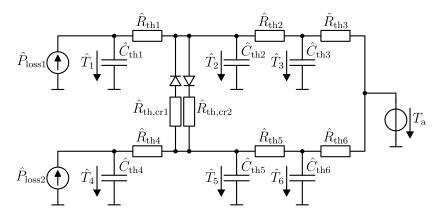

Chapter 4 is structured as follows: The fundamentals of thermal modeling are given in Section 4.1. Section 4.2 describes the thermal influence on power semiconductor module reliability by explaining the degradation mechanism evoked by thermal cycles, showing existing lifetime models and their limitations, and giving a review on condition monitoring methods for power semiconductors via the thermal behavior. Afterwards, Section 4.3 proposes the DT-based observation of the power semiconductor thermal behavior by describing the basic principle of a thermal DT, developing DT approaches based on a particle-swarm-optimization (PSO) - based on [31] - and a dual extended Kalman filter (DEKF), comparing both approaches, and extending the DEKF-based thermal DT to a multichip representation, which considers thermal cross coupling effects. Furthermore, the capability of the DEKF-based multichip thermal DT to represent the thermal behavior in real-time is validated on a laboratory setup. A summary and the conclusions of Chapter 4 can be found in Section 4.4.

Chapter 5 is structured as follows: Based on [21], a review of ATC methods used in power electronics systems as well as an evaluation of these methods for the use in the ST are given in Section 5.1. Section 5.2 elaborates on the graph theory-based modeling used for power routing on basis of [32, 33] by introducing the basics of graph theory-based modeling of power electronics converter systems, describing its application in hybrid grids-feeding STs, as well as revealing and validating a modeling method with higher accuracy for the loss description than the state-of-the-art method. Next, a new third harmonic clamped modulation method - originally presented in [34] - is described, theoretically compared with the first harmonic clamped modulation method, and validated in the laboratory in Section 5.3. Afterwards, Section 5.4 carries out a mission profile-based failure analysis for the hybrid grids-feeding ST topologies and reveals the opportunity for additional failure tolerance in one of the topologies, based on [27, 28]. A summary and the conclusions of Chapter 5 can

be found in Section 5.5.

**Chapter 6** gives a summary and the conclusions of this work. Further, potential topics for future research based on this work are listed.

#### 1.6. List of publications

The scientific publications associated with this work, to which Fig. 1.1 refers, are listed here:

#### **Journal publications**

- J1 **J. Kuprat**, K. Debbadi, J. Schaumburg, M. Liserre and M. Langwasser, "Thermal Digital Twin of Power Electronics Modules for Online Thermal Parameter Identification," in *IEEE Journal of Emerging and Selected Topics in Power Electronics*, doi: 10.1109/JESTPE.2023.3328219.

- J2 **J. Kuprat**, J. Schaumburg, M. Langwasser and M. Liserre, "Mission Profile-Tailored Design and Control of an Interconnected Hybrid Grid Connecting Converter Architecture," in *IEEE Journal of Emerging and Selected Topics in Power Electronics*, doi: 10.1109/JESTPE.2023.3278082.

- J3 J. Schaumburg, **J. Kuprat**, M. Langwasser and M. Liserre, "Efficiency Optimization via Mission Profile-Based Power Routing by Design of Hybrid Grid Connecting Converter Architecture," in *IEEE Open Journal of Power Electronics*, doi: 10.1109/OJPEL.2023.3241778.

- J4 Y. Li, **J. Kuprat**, Y. Li and M. Liserre, "Graph-Theory-Based Derivation, Modeling and Control of Power Converter Systems," in *IEEE Journal of Emerging and Selected Topics in Power Electronics*, doi: 10.1109/JESTPE.2022.3143437.

- J5 Y. Ko, **J. Kuprat**, S. Pugliese and M. Liserre, "Modulation Strategies for Thermal Stress Control of CHB Inverters," in *IEEE Transactions on Power Electronics*, vol. 37, no. 3, pp. 3515-3527, March 2022, doi: 10.1109/TPEL.2021.3117917.

- J6 **J. Kuprat**, C. H. van der Broeck, M. Andresen, S. Kalker, M. Liserre and R. W. De Doncker, "Research on Active Thermal Control: Actual Status and Future Trends," in *IEEE Journal of Emerging and Selected Topics in Power Electronics*, vol. 9, no. 6, pp. 6494-6506, Dec. 2021, doi: 10.1109/JESTPE.2021.3067782.

#### **Conference publications**

- C1 **J. Kuprat**, Y. Pascal and M. Liserre, "Real-Time Thermal Characterization of Power Semiconductors using a PSO-based Digital Twin Approach," 2022 24th European Conference on Power Electronics and Applications (EPE'22 ECCE Europe), 2022, pp. P.1-P.8.

- C2 J. Schaumburg, **J. Kuprat**, M. Langwasser and M. Liserre, "Efficiency Optimization via Mission Profile-Based Design of a Hybrid Grids-Feeding Smart Transformer," 2022 IEEE 13th International Symposium on Power Electronics for Distributed Generation Systems (PEDG), 2022, pp. 1-6, doi: 10.1109/PEDG54999.2022.9923058.

- C3 **J. Kuprat**, J. Schaumburg, M. Langwasser and M. Liserre, "Improved Graph-Theory Based Modeling of the Smart Transformer for Hybrid Grids," 2022 IEEE 16th International Conference on Compatibility, Power Electronics, and Power Engineering (CPE-POWERENG), 2022, pp. 1-6, doi: 10.1109/CPE-POWERENG54966.2022.9880867.

- C4 **J. Kuprat**, J. Schaumburg, M. Langwasser and M. Liserre, "Mission-Profile Based Design of a Hybrid-Grids Feeding Smart Transformer," *2021 6th IEEE Workshop on the Electronic Grid (eGRID)*, 2021, pp. 01-08, doi: 10.1109/eGRID52793.2021. 9662152.

- C5 **J. Kuprat**, M. Andresen, V. Raveendran and M. Liserre, "Modular Smart Transformer Topology for the Interconnection of Multiple Isolated AC and DC Grids," *2020 IEEE Energy Conversion Congress and Exposition (ECCE)*, 2020, pp. 4836-4841, doi: 10.1109/ECCE44975.2020.9236136.

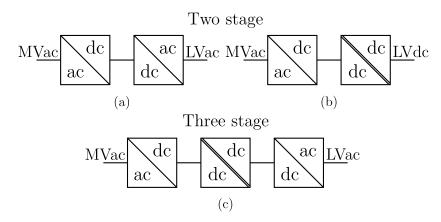

# 2. Fundamentals of hybrid grids-feeding Smart Transformers

This chapter introduces the fundamentals of hybrid grids-feeding Smart Transformers (STs) for optimizing their efficiency and design in Chapter 3. For this purpose, the definition of hybrid grids referred to in this work as well as their advantages and requirements are presented. Further, ST architectures are shown and their ability to fulfill the requirements is discussed. Moreover, the power electronics converters, which are used in this work, to realize topologies from the architectures are introduced.

The chapter is organized as follows: based on [26], advantages and requirements of hybrid grids are presented in Section 2.1. Section 2.2 shows ST architectures and discusses which of them can fulfill the requirements of hybrid grids. The basics of loss calculation and the power electronics converters used to realize ST topologies from the architectures in this work are introduced in Section 2.3. A summary and the conclusions of the chapter can be found in Section 2.4.

# 2.1. Hybrid grids advantages and requirements

This section presents what the term *hybrid grids* refers to in this work. Next, the advantages enabled by the utilization of hybrid grids are shown. Afterwards, the requirements for a safe implementation of hybrid grids, which realizes the shown advantages, are given.

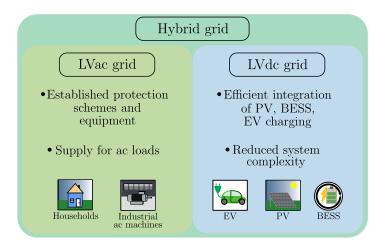

#### 2.1.1. Hybrid grids definition

In this work, the term *hybrid grids* refers to embedding dc grids inside the existing ac grid structure. In particular, the integration of LVdc grids on a low voltage level - up to 750 V dc between power line and neutral conductor - is considered besides the existing LVac grids.

The existing MVac grids are considered as primary distribution grid on a medium voltage level. The STs investigated in this work build a substation to connect an MVac primary distribution grid with a hybrid secondary distribution grid consisting of LVac and LVdc grids.

#### 2.1.2. Hybrid grids advantages

The advantages of hybrid grids are the benefits from LVac as well as LVdc grids, which can be both exploited by using hybrid LV grids [35]. These benefits of LVac grids compared to LVdc grids and vice versa are presented in Fig. 2.1. A main benefit of LVdc grids compared

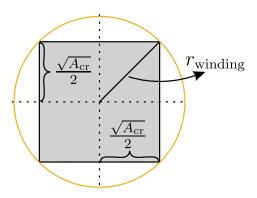

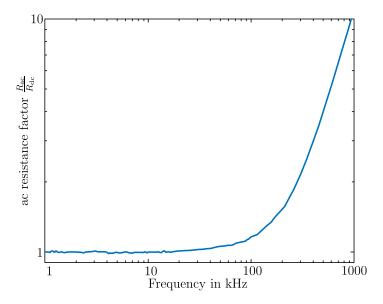

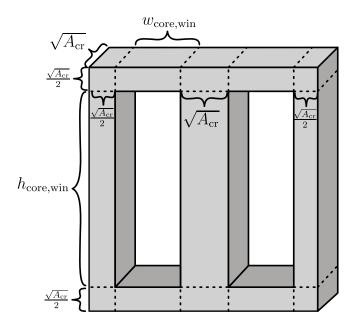

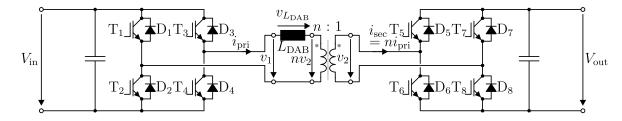

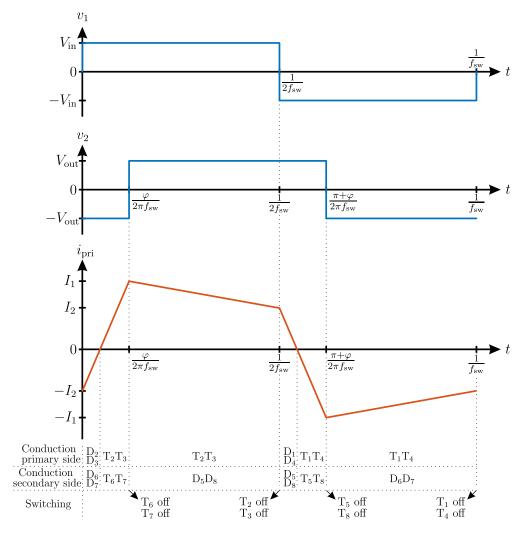

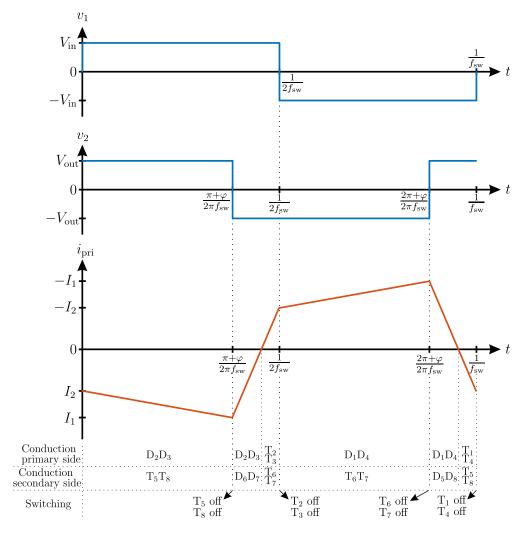

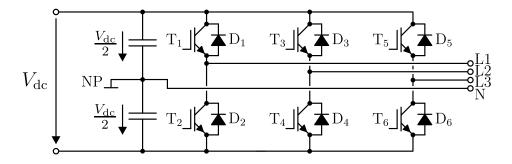

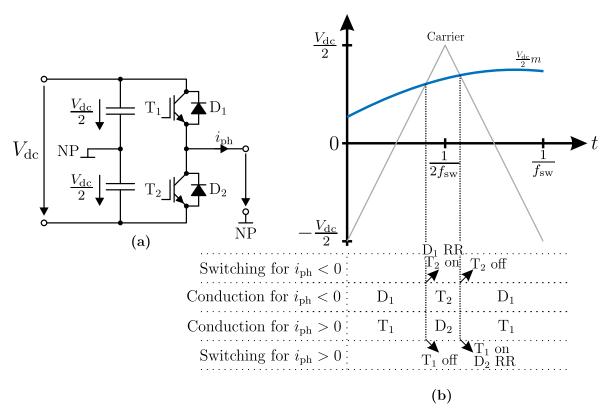

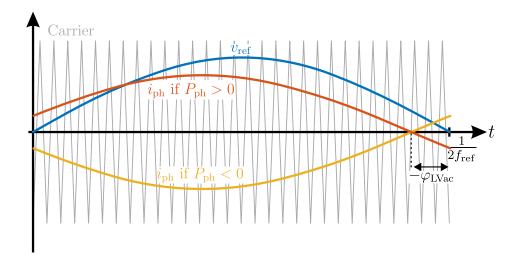

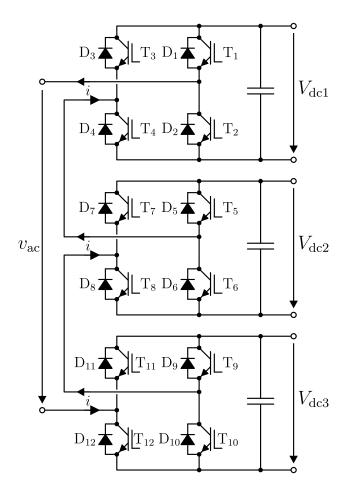

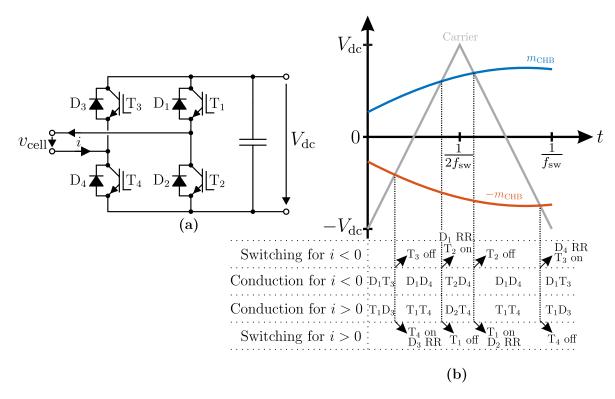

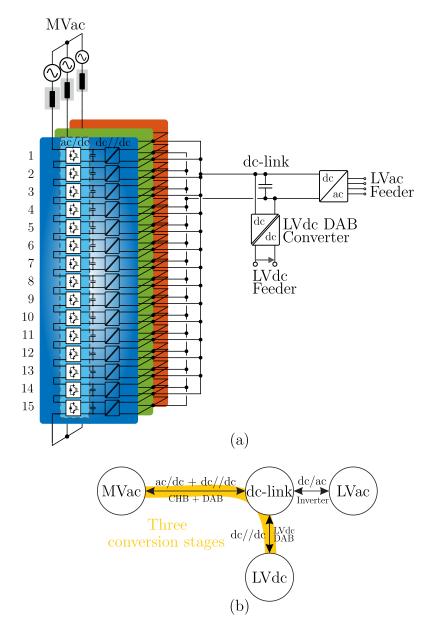

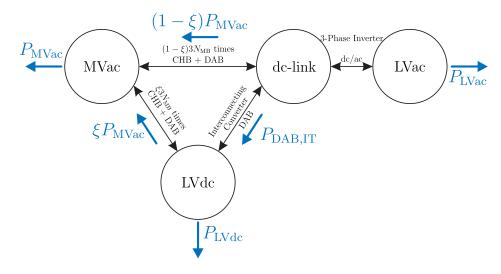

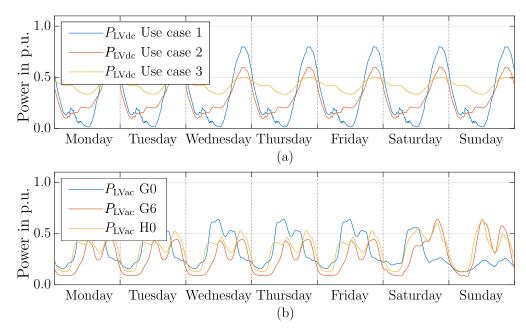

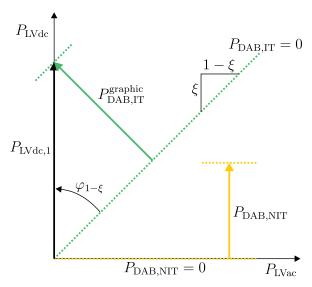

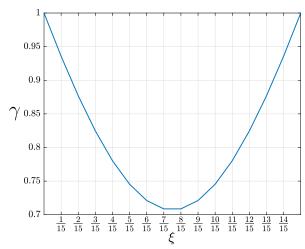

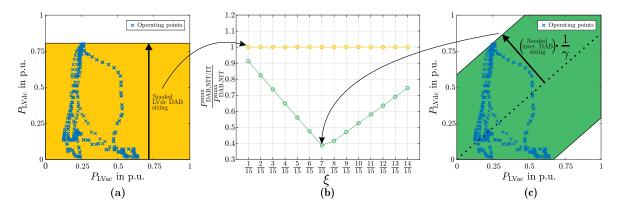

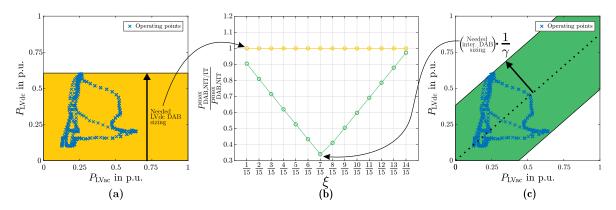

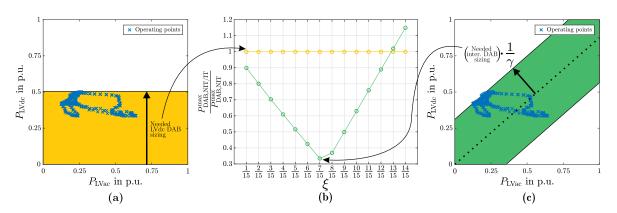

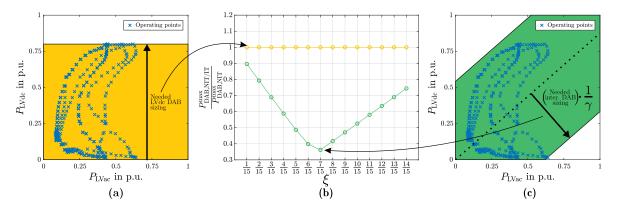

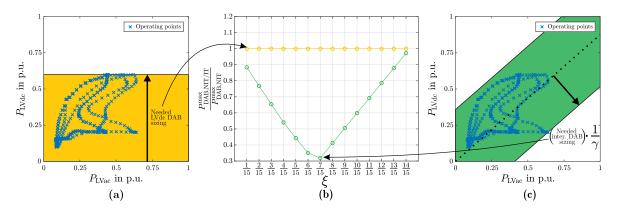

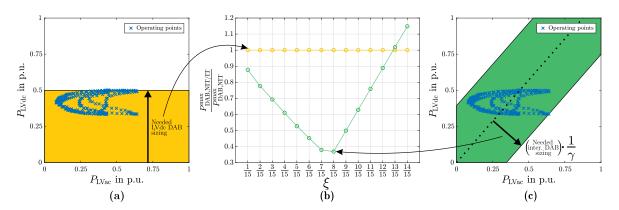

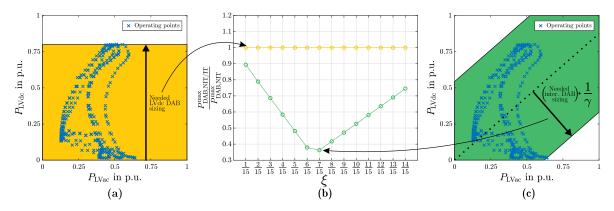

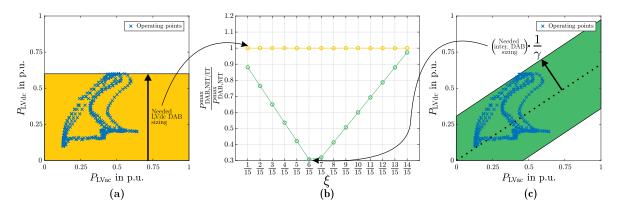

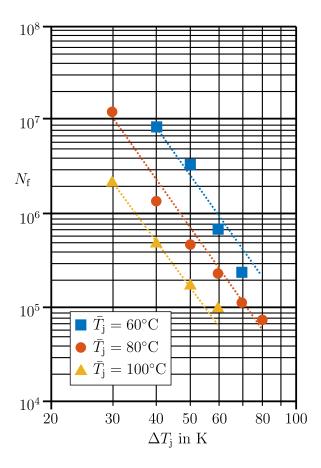

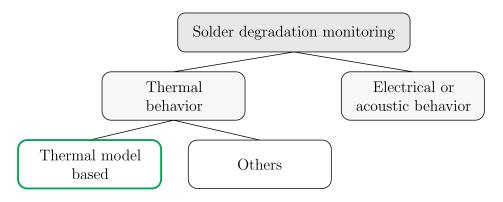

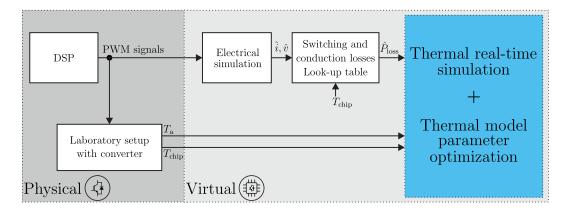

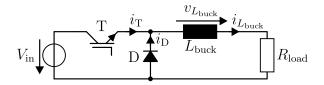

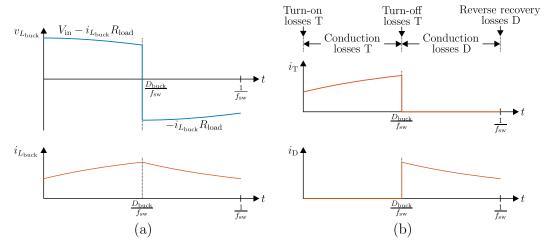

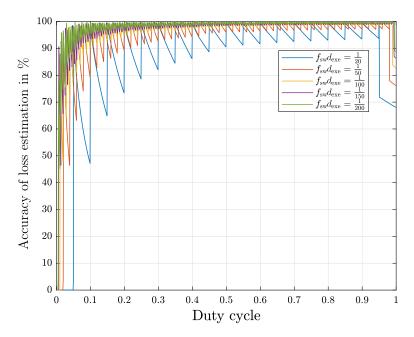

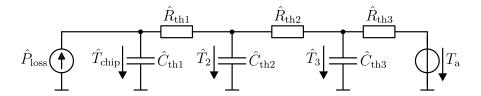

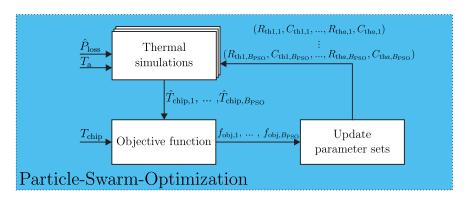

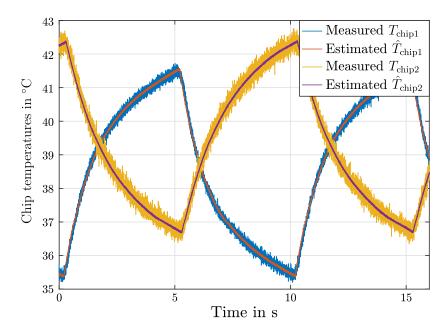

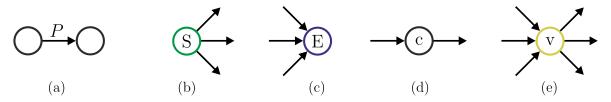

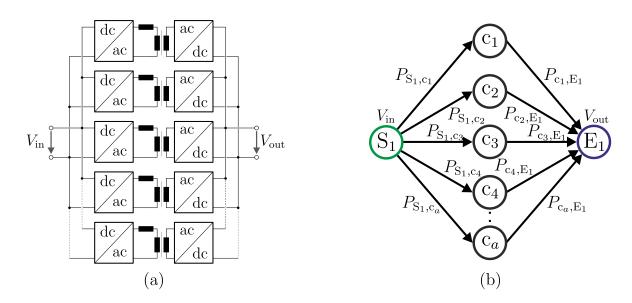

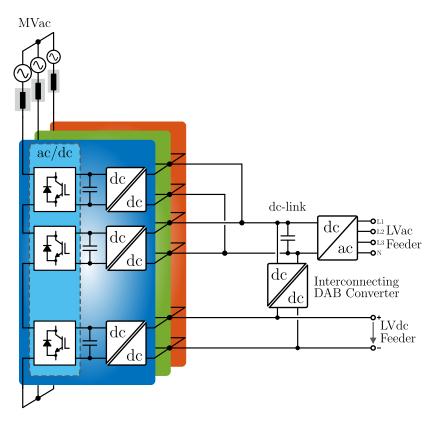

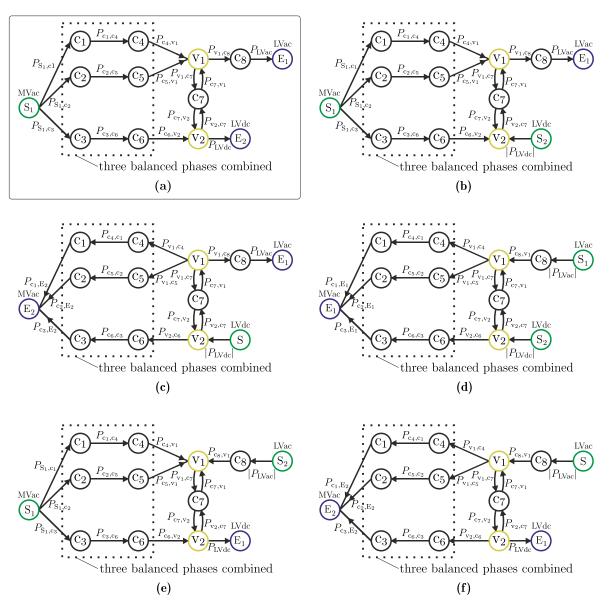

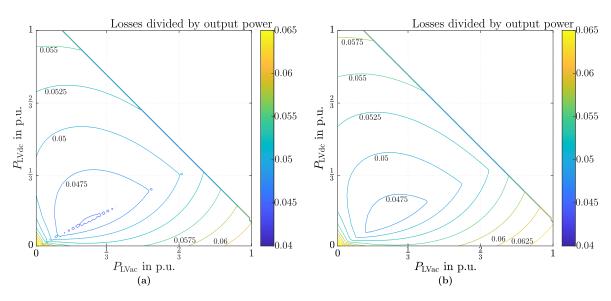

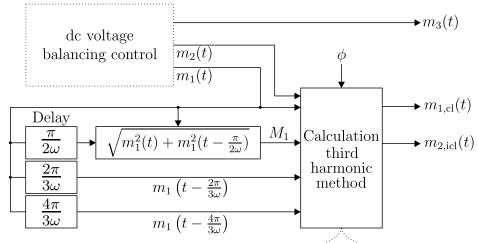

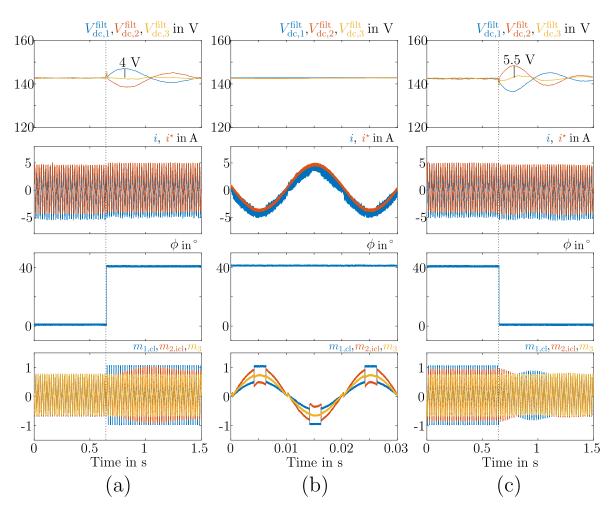

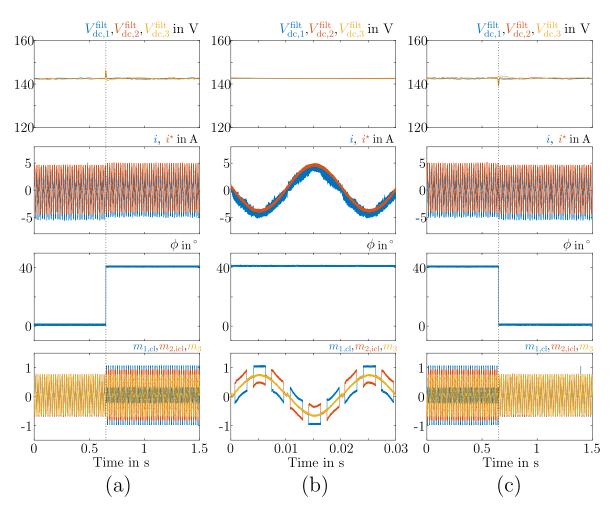

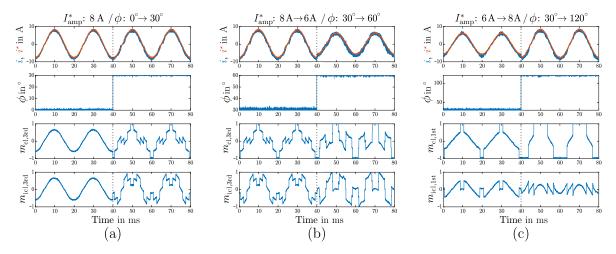

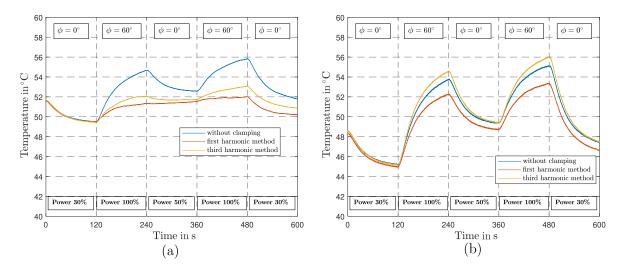

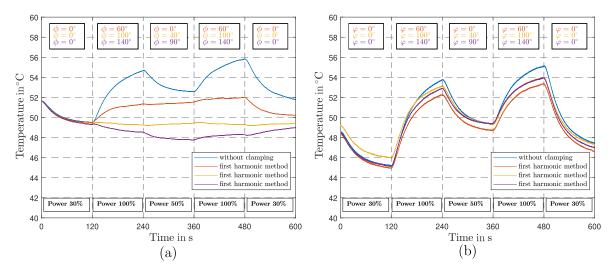

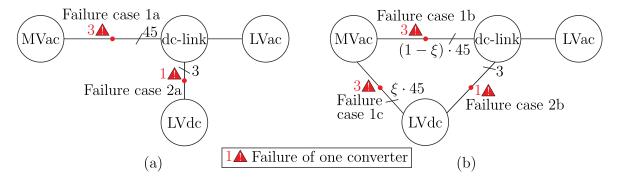

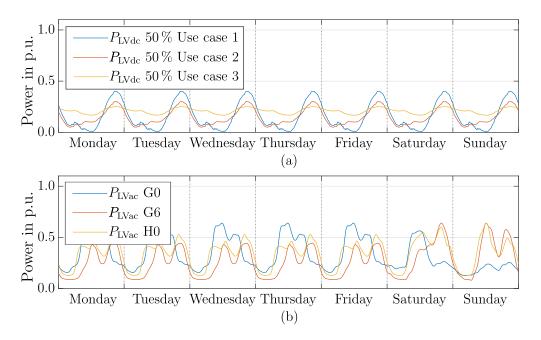

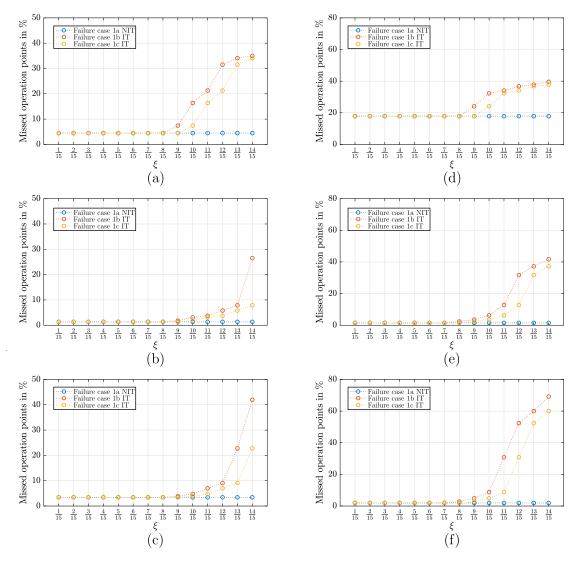

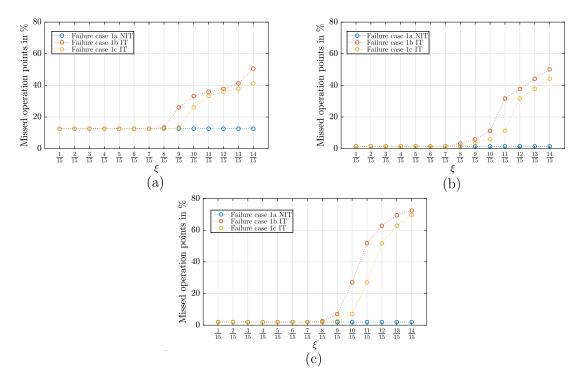

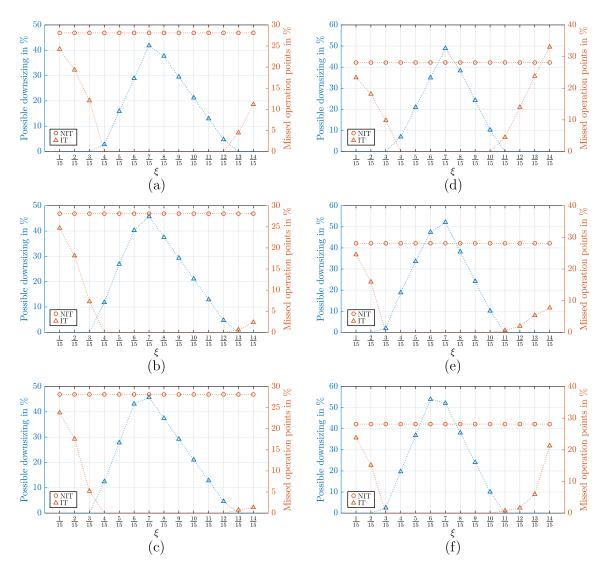

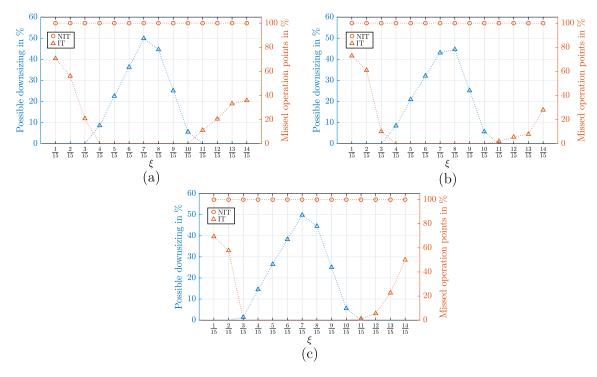

Fig. 2.1: Benefits of LVac and LVdc grids combinable via a hybrid grid.