# A Multi-Port Partial Power Converter for PV based Smart Home Applications

# **Dissertation**

zur Erlangung des akademischen Grades

Doktor der Ingenieurwissenschaften

(Dr.-Ing.)

Technische Fakultät

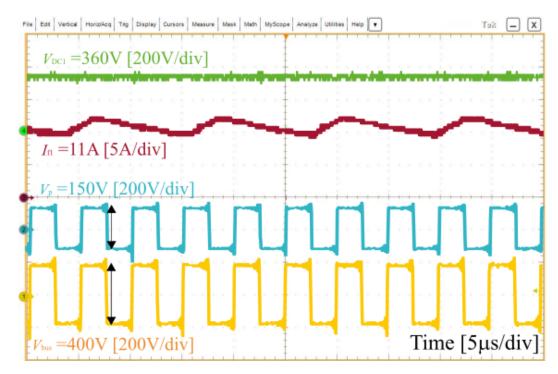

der Christian-Albrechts-Universität zu Kiel

vorgelegt von

M.Sc. Yongdae Kwon

*Kiel* 2025

# Erklärung

Ich erkläre an Eides statt, dass ich die Dissertation zum Thema:

## A Multi-Port Partial Power Converter for PV based Smart Home Applications

abgesehen von der Betreuung durch Herrn Prof. Marco Liserre selbstständig und ohne Hilfe angefertigt habe und bisher weder ganz noch zum Teil an einer anderen Stelle im Rahmen eines Prüfungsverfahrens vorgelegt, veröffentlicht oder zur Veröffentlichung eingereicht habe. Weiterhin versichere ich hiermit, dass ich die vorliegende Arbeit unter Einhaltung der Regeln guter wissenschaftlicher Praxis der Deutschen Forschungsgemeinschaft angefertigt habe und alle von anderen Autoren wörtlich übernommenen Stellen wie auch die sich an die Gedankengänge anderer Autoren eng anlehnenden Ausführungen meiner Arbeit besonders gekennzeichnet und die entsprechenden Quellen angegeben sind. Schlussendlich bestätigeich, dass mir noch kein akademischer Grad entzogen wurde.

Kiel, den 15. 06 2024

Yongdae Kwon

Gutachter: Prof. Marco Liserre

Gutachter: Prof. Marcelo Heldwein

Datum der mündlichen Prüfung: 09.12.2024

# Acknowledgments

This work was carried out during my work at the Chair of Power Electronics of Kiel University and after at Huawei Nuremberg Research Center, Germany. There are many people to whom I owe my thanks, and I would like to express my sincere gratitude to them in this acknowledgment.

First of all, I genuinely appreciate my academic supervisor Prof. Dr.-Ing Marco Liserre, who gave me the opportunity to join the research group and precious support during the journey of my doctoral periods. His guidance and advice significantly improved my quality to finish this work.

I would like to thank Dr. Francisco Freijedo and Mr. Miroljub Bakic for all their supports that helped me to be a better industrial researcher. Dr. Francisco supported me to establish the clear research direction and gave his best support to improve my academic writing skills. Mr. Miroljub Bakic fully supported me in improving the hardware designing skills.

I thank my colleagues in Chair of Power Electronics for the valuable discussions and advice for my works. Specially, Dr. -Ing. Junhyung Jung and Dr.-Ing. Sante Pugliese.

Last but not least, I would like to express my deepest love and heartfelt gratitude to my beloved wife, Seojin Kim. Throughout the long and often challenging journey of my doctoral studies, she has been my greatest source of strength. Her unwavering support, patience, and belief in me have been invaluable. Without her endless love and care, I would not have been able to complete this work. To my beloved Seojin, thank you from the bottom of my heart for believing in me, standing by my side throughout this PhD journey, and giving me the strength not to fall. I love you deeply.

# **Contents**

| Eng | iish s | summary                                                                   | Ш   |

|-----|--------|---------------------------------------------------------------------------|-----|

| Ger | man    | summary                                                                   | IV  |

| Use | d syn  | mbols and abbreviations                                                   | V   |

| 1   | Intr   | oduction                                                                  | 1   |

|     | 1.1    | Motivation of novel multi-port partial power DC-DC converter architecture |     |

|     |        | development                                                               | 1   |

|     | 1.2    | Research proposal                                                         | 2   |

|     | 1.3    | Structure of the thesis                                                   | 3   |

|     | 1.4    | Assignment of publications to the chapters of this thesis                 | 4   |

| 2   | Pow    | ver converters in the smart home application                              | 7   |

|     | 2.1    | DC-AC converter stage control                                             | 8   |

|     |        | 2.1.1 Grid forming mode                                                   | 9   |

|     |        | 2.1.2 Grid following mode                                                 | 9   |

|     | 2.2    | The architectures of DC-DC converter stage                                | 17  |

|     |        | 2.2.1 Full power processing DC-DC converter architecture                  | 17  |

|     |        | 2.2.2 Partial power processing DC-DC converter architectures              | 19  |

|     | 2.3    | Summary                                                                   | 28  |

| 3   | Mul    | ti-port partial power converter architecture development                  | 29  |

|     | 3.1    | Description of the target specification                                   | 32  |

|     | 3.2    | Partial voltage converter topology selection                              | 37  |

|     |        | 3.2.1 Boost type                                                          | 37  |

|     |        | 3.2.2 Buck type                                                           | 40  |

|     |        | 3.2.3 Buck-boost type                                                     | 41  |

|     |        | 3.2.4 Selection of optimal PVC topology options                           | 43  |

|     | 3.3    | DC transformer topology selection                                         | 47  |

|     |        | 3.3.1 DC transformer topology selection: DAB vs DBSRC                     | 48  |

|     |        | 3.3.2 Optimal topology selection of DBSRC                                 | 51  |

|     | 3.4    | Summary                                                                   | 63  |

| 4   |        | atrol and power conversion parameter optimization of multi-port PPC       | 66  |

|     | 4.1    | Operating principle of the multi-port PPC                                 | 66  |

|     | 4.2    | Parameter design of PVC                                                   | 68  |

|     |        | 4.2.1 Small signal model and control of PVC stage                         | 74  |

|     | 4.3    | Parameter design of DC transformer                                        | 77  |

|     |        | 4.3.1 First harmonic approximation model of DHBSRC                        | 79  |

|     |        | 4.3.2 Parameter selection and control of DHBSRC                           | 81  |

|     |        | 4.3.3 Control scheme of DC-transformer stage                              | 83  |

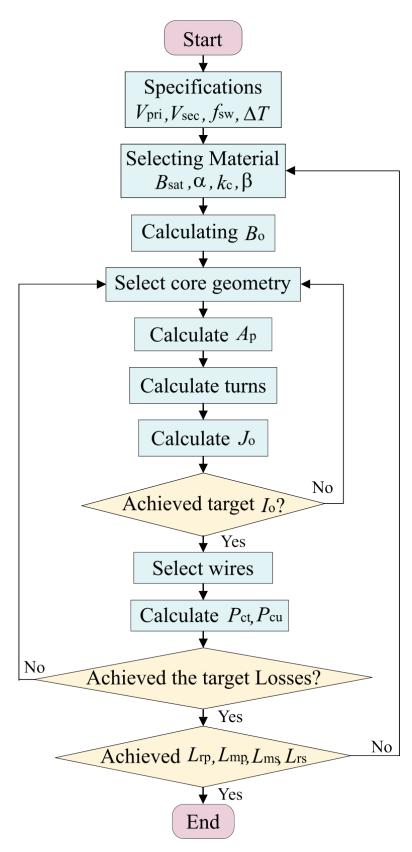

|     |        | 4.3.4 Transformer design                                                  | 85  |

|     | 4.4    | _                                                                         | 94  |

| 5   | Ana    | allysis and design of the multi-port PPC                                  | 97  |

|     |        | Partial power processing characteristics of the multi-port PPC            | 97  |

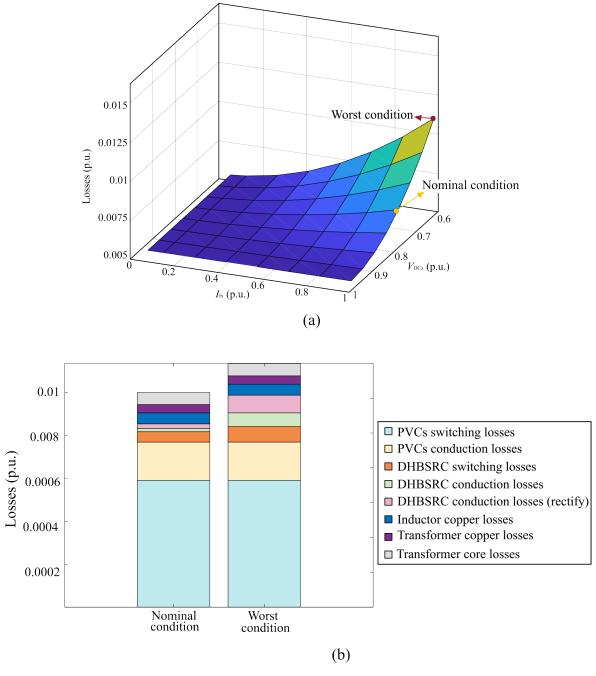

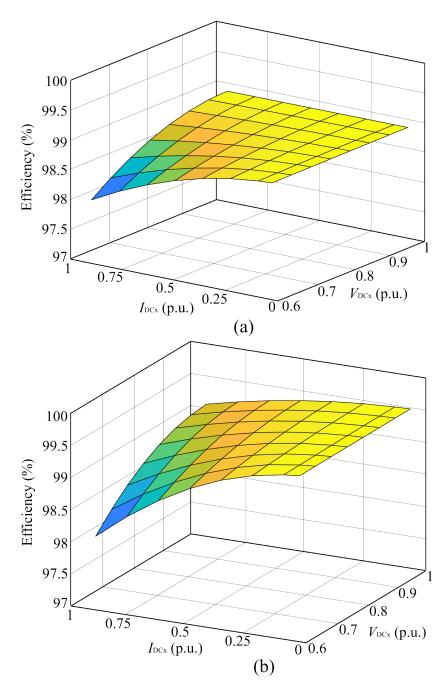

|     | 5.2    | Loss and efficiency analysis of the multi-port PPC                        | 102 |

|     |        |                                                                           |     |

|   | 5.3 Laboratory scale prototype design |                                                    |     |  |  |  |

|---|---------------------------------------|----------------------------------------------------|-----|--|--|--|

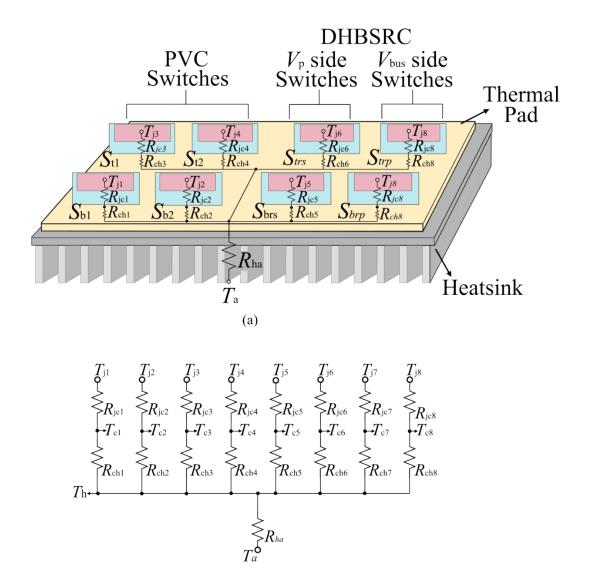

|   |                                       | 5.3.1 Heatsink design of the multi-port PPC        | 108 |  |  |  |

|   |                                       | 5.3.2 Specifications of the prototype              | 111 |  |  |  |

|   | 5.4                                   | Summary                                            | 111 |  |  |  |

| 6 | Vali                                  | dation of the multi-port PPC concept               | 115 |  |  |  |

|   | 6.1                                   | Experimental results of the multi-port PPC concept | 115 |  |  |  |

|   | 6.2                                   | Comparison of benchmark and proposed architecture  | 122 |  |  |  |

|   | 6.3                                   | Summary                                            | 123 |  |  |  |

| 7 | Sun                                   | nmary, conclusion and future research              | 125 |  |  |  |

|   | 7.1                                   | Summary and conclusion                             | 125 |  |  |  |

|   | 7.2                                   | Future research                                    | 127 |  |  |  |

| 8 | Ref                                   | erences                                            | 128 |  |  |  |

# **English Summary**

The world is undergoing a profound transformation with a remarkable increase in the use of renewable energy. This paradigm shift is not limited to large utility-scale projects but is extending into residential applications, electrifying living spaces. Furthermore, advancements in power electronic converters (PEC) play a key role in transforming energy management in home applications. Thanks to PECs, residences have the potential to evolve into intelligent ecosystems capable of optimizing energy consumption through advanced power management, also known as smart home system.

In recent years, the increasing penetration of the renewable energy sources (RES) and the residential-energy storage system (ESS) to the home allow supplying the power to the smart home directly through the RES or residential-ESS by DC-DC power conversion without connecting to AC grid. The utilization of RES and residential-ESS helps to reduce the consumption cost of the electricity, and helps to manage the power supply even during the black-out. In these reasons, DC-DC converter in the smart home architecture became one of the necessary component which makes possible to utilize the power of RESs and residential-ESS.

Conventionally, DC-DC converters have been used full power processing (FPP) architectures, which process the total power from the input. On the other hand, the exploration of partial power processing (PPP) architectures, which process only a portion of the power from the input, offers a way to further reduce costs and losses compared to FPP architectures. Therefore, use of PPP architectures in the smart home application gives higher possibility to achieve better integration, ultimately reducing costs and volume of the PECs.

In this study, a multi-port PPP converter architecture is developed and analyzed for the smart home application. The proposed architecture aims to improve the efficiency achieved by state of the art multi-port PPP technologies. Furthermore, it also aims to reduce the volume and cost of the converter by using partially rated power electronics devices compared to conventional FPP converters. In order to achieve the goals, the topologies should be carried out for the optimal selection. Furthermore, a detailed design guideline for the proposed PPC is provided. Therefore, the converter can be realized and applied to practical solutions. The relationship between the PPP capability of the proposed architecture and the losses are analyzed to validate the PPP on the efficiency improvement. Finally, the prototype of the proposed architecture concept is realized. The steady state operation and the power control capability of the proposed architecture are validated by the experiments. The efficiencies at different load conditions are also measured and the peak efficiency measurement result is provided.

# **German Summary**

Die Welt befindet sich in einem tiefgreifenden Wandel, der durch einen bemerkenswerten Anstieg der Nutzung erneuerbarer Energien gekennzeichnet ist. Dieser Paradigmenwechsel beschränkt sich nicht nur auf große Versorgungsprojekte, sondern erstreckt sich auch auf Anwendungen im Wohnbereich und elektrifiziert Lebensräume. Darüber hinaus spielen Fortschritte bei Leistungselektronik-Wandlern (PEC) eine Schlüsselrolle bei der Transformation des Energiemanagements in Heimanwendungen. Dank PECs haben Wohngebäude das Potenzial, sich zu intelligenten Ökosystemen zu entwickeln, die durch fortschrittliches Energiemanagement, auch bekannt als Smart-Home-System, den Energieverbrauch optimieren können.

In den letzten Jahren ermöglicht die zunehmende Verbreitung erneuerbarer Energiequellen (RES) und Energiespeichersysteme (ESS) für Privathaushalte die direkte Stromversorgung von Smart Homes über RES oder ESS durch Gleichstromwandlung, ohne dass eine Verbindung zum Wechselstromnetz erforderlich ist. Die Nutzung von RES und ESS trägt zur Senkung der Stromkosten bei und hilft, die Stromversorgung auch während eines Stromausfalls aufrechtzuerhalten. Aus diesen Gründen wurde der DC-DC-Wandler in der Smart-Home-Architektur zu einer der notwendigen Komponenten, die die Nutzung der Energie aus RES und ESS ermöglicht

Herkömmlicherweise wurden in DC-DC-Wandlern Vollleistungs-Verarbeitungsarchitekturen (FPP) verwendet, die die gesamte Leistung vom Eingang verarbeiten. Andererseits bietet die Erforschung von Teilleistungs-Verarbeitungsarchitekturen (PPP), die nur einen Teil der Leistung vom Eingang verarbeiten, eine Möglichkeit, Kosten und Verluste im Vergleich zu FPP-Architekturen weiter zu reduzieren. Daher bietet die Verwendung von PPP-Architekturen in Smart-Home-Anwendungen eine höhere Wahrscheinlichkeit, eine bessere Integration zu erreichen, was letztlich zu einer Reduzierung der Kosten und des Volumens der PECs führt.

In dieser Studie wird eine neuartige Multi-Port-PPP-Konverterarchitektur für Smart-Home-Anwendungen entwickelt und analysiert. Die vorgeschlagene Architektur zielt darauf ab, die Effizienz der aktuellen Multi-Port-PPP-Technologien zu verbessern. Darüber hinaus soll durch den Einsatz von teilweise bewerteten passiven und aktiven Leistungselektronikbauteilen im Vergleich zu herkömmlichen FPP-Konvertern das Volumen und die Kosten des Konverters reduziert werden. Um diese Ziele zu erreichen, sollten die Topologien für eine optimale Auswahl durchgeführt werden. Darüber hinaus wird eine detaillierte Konstruktionsrichtlinie für den vorgeschlagenen PPC bereitgestellt. Daher kann der Konverter realisiert und in praktischen Lösungen angewendet werden. Die Beziehung zwischen der PPP-Fähigkeit der vorgeschlagenen Architektur und den Verlusten wird analysiert, um die PPP hinsichtlich der Effizienzsteigerung zu validieren. Schließlich wird der Prototyp des vorgeschlagenen Architekturkonzepts realisiert. Der stationäre Betrieb und die Leistungssteuerungsfähigkeit der vorgeschlagenen Architektur werden durch Experimente validiert. Die Wirkungsgrade bei verschiedenen Lastbedingungen werden ebenfalls gemessen und das Ergebnis der Spitzenwirkungsgradmessung wird angegeben.

# Used symbols and abbreviations

# **General Symbols**

xinstantaneous value $\bar{X}$ Average value $\tilde{x}$ Oscillation value $\Delta x$ Differential valueXRMS value $X_{peak}$ Peak value

# **Superscripts**

\* Reference value

Value without control action

# **Subscripts**

DCx DC input related

bus Inverter side DC bus related

p Partial power related

grid Grid related

$\alpha,\beta$  Stationary reference frame values d,q Synchronous reference frame values

pcc Point of common coupling

SRC Series resonant converter related

DAB Dual active bridge converter related

min Minimum value max Maximum value

s Partial voltage converter switching related

rate Rated value

# Special symbols

$\Delta V_{\rm pp}$  Voltage ripple (peak-to-peak)

*ω* Radial representation of frequency output of synchronization block

$\omega_0$  Radial representation of the fundamental frequency

$\theta$  Phase output of synchronization block

$\theta_0$  Initial phase of the fundamental frequency

L Inverter filter inductanceC Inverter filter capacitance

$L_{\text{grid}}$  Grid inductance

I Inverter filter current  $V_n$  Inverter leg voltage

$V_{\text{grid}}$  Grid voltage  $Y_{\text{PLL}}$  PLL Admittance  $Y_{1}$  Inverter Admittance

*Y*<sub>2</sub> Self-Synchronization Admittance

$Y_{\rm grid}$  Grid Admittance

$I_{\rm m}$  Current reference amplitude  $f_{\rm BW}$  Grid Synchronization bandwidth  $f_{\rm inv}$  Inverter switching frequency  $P_{\rm LF}$  Full power processing losses  $P_{\rm LP}$  Partial power processing losses

$P_{\rm dir}$  Direct power

$C_{\rm pi}$   $i^{th}$  partial capacitor of DPC

$V_{\rm pi}$  Partial voltage on  $i^{th}$  partial capacitor of DPC  $I_{\rm pi}$  Partial current through  $i^{th}$  partial capacitor of DPC

$I_{\text{dpc}_i}$  Current of  $i^{th}$  DPC  $D_i$  Duty cycle of  $i^{th}$  DPC

$P_{\text{dfi}}$  Differential power processed on  $i^{th}$  differential power converter

V<sub>aux</sub> Auxiliary DC source voltage

$I_{\text{frx}}$  Output current of  $x^{th}|_{x=1,\dots,n}$  fractional power converter  $I_{\text{Ox}}$  Output current of  $x^{th}|_{x=1,\dots,n}$  partial power converter

$\eta$  Efficiency

$D_{\rm X}$  Duty cycle of  $x^{th}$  partial voltage converter  $V_{\rm mpp}$  Maximum power point voltage of PV panel

$V_{\rm oc}$  Open circuit voltage of PV panel

$I_{\text{mpp}}$  Maximum power point current of PV panel

$P_{\text{rate}}$  Rated power  $I_{\text{rate}}$  Rated current

$V_{\rm B}$  Break down voltage  $I_{\rm d_{rate}}$  Rated drain current  $R_{{

m DS}_{on}}$  On state resistance

$Q_{\rm g}$  Gate charge  $I_{{\rm D}_{pulse}}$  Pulse current

di/dt Commutation speed  $Q_{rr}$  Reverse recovery charge  $t_{rr}$  Reverse recovery time

$i_{\rm fx}$  Filter current of  $x^{th}$  partial voltage converter

$S_{tx}$ ,  $S'_{tx}$ ,  $S_{bx}$ ,  $S'_{bx}$  Switch sets of the PVC legs

$i_{\rm d}$  Drain current of the switching device  $P_{\rm con}$  Conduction losses of the semiconductor  $P_{\rm sw}$  Switching losses of the semiconductor

$V_{

m dr}$  Gate driver output voltage  $V_{

m dd}$  Voltage applied to drain  $V_{

m ds}$  Drain-Source voltage  $V_{

m gs}$  Gate-Source voltage

$R_{\rm g}$  Gate resistor  $i_{\rm g}$  Gate current

$C_{

m gs}$  Gate-Sources capacitor  $C_{

m gd}$  Gate-Drain capacitor  $C_{

m ds}$  Drain-Sources capacitor  $V_{

m g(th)}$  Gate threshold voltage  $V_{

m g(plt)}$  Gate plateau voltage  $V_{

m gen}$  Switch voltage rising times

$t_{ru}$  Switch voltage rising time  $t_{fu}$  Switch voltage falling time  $t_{r}$  Drain current rising time  $t_{f}$  Drain current falling time

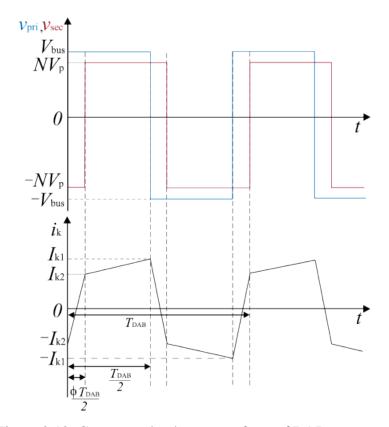

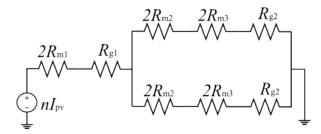

$P_{\text{DCT}}$  Processed power on DC transformer  $V_{\text{pri}}$  Primary side voltage of DC transformer  $V_{\text{sec}}$  Secondary side voltage of DC transformer

$i_{\rm k}$  DAB converter current

$i_{k1}$  First peak of DAB converter current  $i_{k2}$  Second peak of DAB converter current  $L_k$  DAB converter leakage inductance

N Transformer turns ratio

$\phi$  Phase shift angle of DAB converter

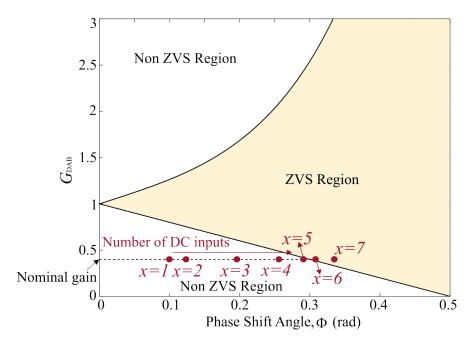

n Number of DC input ports  $G_{DAB}$  Number of DC inputs

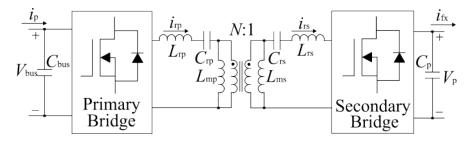

Inverter side resonant current  $i_{\rm rp}$ Inverter side resonant inductance  $L_{\rm rp}$ Inverter side resonant capacitance  $C_{\rm rp}$ Inverter side magnetizing inductance  $L_{\rm mp}$ Partial voltage side resonant current  $i_{\rm rs}$  $L_{\rm rs}$ Partial voltage side resonant inductance Partial voltage side resonant capacitance  $C_{\rm rs}$ Partial voltage side magnetizing inductance  $L_{\rm ms}$

f<sub>r</sub> Resonant current

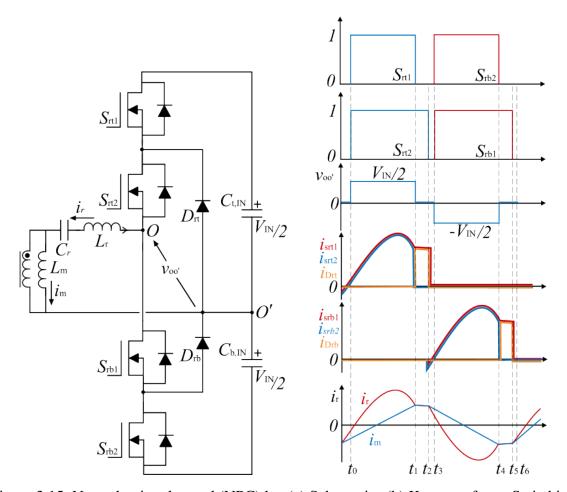

$S_{\text{rtx}}$ ,  $S_{\text{rbx}}$  Switch sets of DBSRC legs

$V_{oo}$  Voltage between neutral points of DBSRC legs

$V_{\rm IN}$  General representation of DC input voltage representation of DBSRC legs

$C_{\text{IN}}$  General representation of DC input capacitor of DBSRC legs

$C_{t_{\text{IN}}}$ ,  $C_{t_{\text{IN}}}$  General representation of top-bottom split DC input capacitor of DBSRC legs

$i_{\rm r}$  General representation of resonant current of DBSRC legs  $L_{\rm r}$  General representation of resonant inductance of DBSRC legs  $C_{\rm r}$  General representation of resonant capacitance of DBSRC legs  $L_{\rm m}$  General representation of magnetizing inductance of DBSRC legs  $i_{\rm m}$  General representation of magnetizing current of DBSRC legs

dV/dt Transformer voltage step  $C_{\rm tp}$  Top side partial capacitor  $C_{\rm bp}$  Bottom side partial capacitor

$\Lambda_{L}$  Volume of inductor

*K*<sub>L</sub> Inductor volume coefficient

$\Lambda_{\rm C}$  Volume of capacitor

*K*<sub>C</sub> Capacitor volume coefficient

$P_{\text{core}}$  Inductor core losses  $K_{\text{core}}$ ,  $\alpha$ ,  $\beta$  Stein-Metz coefficient

B Flux density

$R_{\rm Lfx}$ Inductor winding resistance $\sigma$ dielectric bulk conductivity $\varepsilon$ Permittivity of dielectric

*I*<sub>sat</sub> Saturation current

l Lengthw Widthh Height

$G_{cc}$  Current control transfer function

$G_{\rm HBx}$  PVC transfer function

$T_{\rm i}$  Integral time  $\tau$  LC time constant

$H_{I_{fx}}$  Close loop transfer function of PVC

$\zeta$  Damping constant

$\omega_c$  Bandwidth  $T_{\rm set}$  Settling time

$N_1$  Inverter side transformer turns

$A_{\rm c}$  Core area

$\Lambda_T$  Transformer volume  $\Lambda_{co}$  Transformer core volume

$l_{\rm c}$  Core length

$P_{\rm V}$  Transformer core losses per unit volume  $V_{\rm rp}$  First harmonic approximation voltage input  $V_{\rm rs}$  First harmonic approximation voltage output

$\phi_{o}$  Phase angle between  $v_{rp}$  and  $v_{rs}$   $R_{e}$  Equivalent AC load of DHBSRC

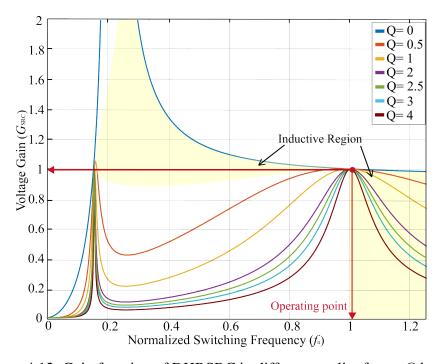

$G_{SRC}$  Gain function of DHBSRC

*X* Reactance

h Inductor turns ratio

Q Quality factor

$\omega_{\rm n}$  Normalized radial DHBSRC switching frequency  $I_{\rm mp}$  Inverter side magnetizing current of DHBSRC

$B_{\rm o}$  Optimal flux density  $\rho_{\rm w}$  resistivity of copper  $\Delta T$  Temperature rise

$k_{\rm a}, k_{\rm c}, k_{\rm w}$  Dimensionless constant coefficient  $k_{\rm u}$  winding window utilization factor

$K_{\rm v}$  Voltage waveform factor

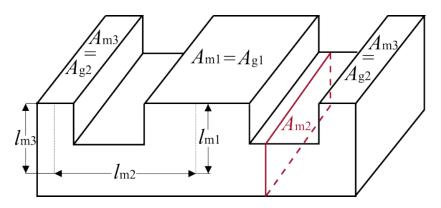

$l_{\rm e}$  Effective length  $A_{\rm e}$  Effective area  $\Lambda_{\rm e}$  Effective volume m Mass of core  $A_{\rm p}$  Area product  $A_{\rm w}$  Wire area  $J_{\rm o}$  Current density

$P_{\rm ct}$  Transformer core losses

$R_{\rm dcp}$  Inverter side DC resistance of transformer

$R_{\rm dcs}$  Partial voltage side DC resistance of transformer

$MLT_{\rm p}$  Mean length of turn on inverter side

$MLT_s$  Mean length of turn on partial voltage side

$\delta$  Skin depth

$R_{\rm acp}$  Inverter side AC resistance of transformer

$R_{\rm acs}$  Partial voltage side AC resistance of transformer

$r_{\rm w}$  Radius of wire

$P_{\text{cu}}$  Copper losses of the transformer  $L_{\text{sfp}}$  Inverter side self inductance

$L_{\rm sfs}$  Partial voltage side self inductance

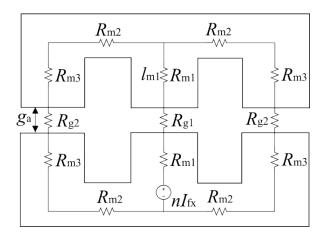

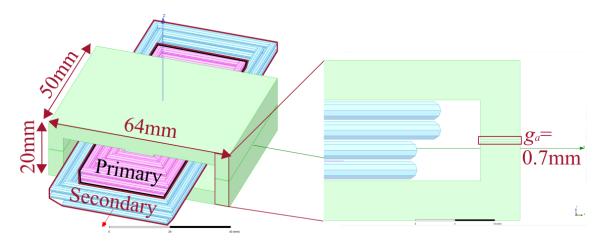

g<sub>a</sub> Airgap

$R_{\rm mk}$  Transformer core reluctance

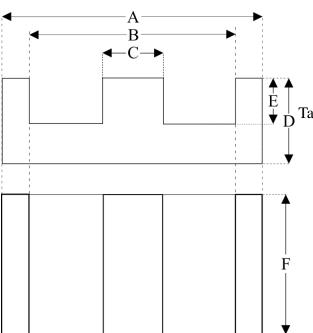

$l_{\rm mk}$  Distance of core geometry (Fig. 4.20)  $A_{\rm mk}$  Area of core geometry (Fig. 4.20)

$A_{\rm gv}$  Area of airgap (Fig. 4.20)

$R_{\rm me}$  Equivalent total reluctance of transformer  $\mu_0$  vacuum permeability (=4 $\pi$ 10e - 7 H/m)  $b_1$  Average width of inverter side turns

$b_2$  Average width of partial voltage side turns

$b_{\rm g}$  gap between wires  $h_{\rm i}$  height of the wires

$\varepsilon_{\rm cc}$  Transformer coupling coefficient

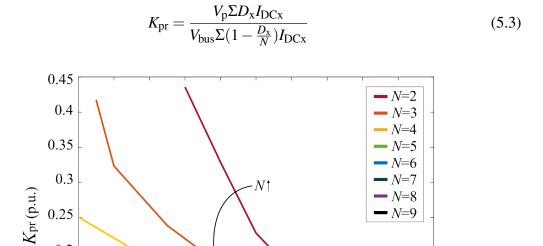

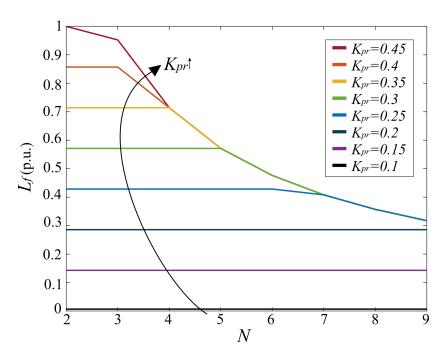

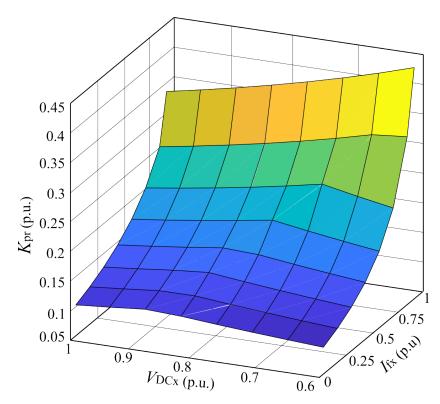

$K_{pr}$  Partial power ratio  $T_{jm}$  Junction temperature

$R_{\rm jcm}$  Junction to case thermal resistance

$T_{\rm cm}$  Case temperature

$R_{\rm chm}$  Case to heatsink thermal resistance

$T_{\rm h}$  Heatsink temperature  $R_{\rm ha}$  Heatsink to ambient losses  $T_{\rm a}$  Ambient temperature  $\Lambda_{\rm hs}$  Heatsink volume  $W_{\rm g}$  Heatsink weight  $\Lambda_{\rm s}$  Switch volume

# **Abbreviations**

RES Renewable Energy Sources

PEC Power Electronic Converter

PV Photo-Voltaic EV Electric Vehicle

ESS Energy Storage System

LED Light Emitting Diode

FPC Full Power Converter

HFT High Frequency Transformer

PPP Partial Power Processing

PD Power Density

PPC Partial Power Converter

PWM Phase Width Modulation

PI Proportional-Integral

PLL Phase Locked Loop

p.u. per unit

FPP Full Power Processing

VA Volt-Ampere

DPC Differential Power Converter

FRPC Fractional Power Converter

KCL Kirchhoff's Current Law

IPOS Input Parallel-Output Series

ISOP Input Series-Output Parallel

PVC Partial Voltage Converter

DAB Dual Active Bridge

SRC Series Resonant Converter MPP Maximum Power Point

MPPT Maximum Power Point Tracking

HB Half-Bridge

ZVS Zero voltage switching

DBSRC Dual bridge series resonant converter

NPC Neutral Point Clamped

DHBSRC Dual half-bridge series resonant converter

FHA First Harmonic Approximation

ESR Equivalent series resistance

CSF Component stress factor

UF Utilization factor

1 Introduction 1

# 1 Introduction

This chapter presents the motivations of the the novel partial power DC-DC converter architecture development. The targets of the development are to improve the efficiency and volume reduction compared to the conventional DC-DC converter architectures. After the motivation of work, a research proposal for the thesis is explained. Finally, the structure of the thesis is described. In addition, the related publications corresponding to each chapter are highlighted.

# 1.1 Motivation of novel multi-port partial power DC-DC converter architecture development

The modern world is witnessing a change in the living spaces. Smart homes have emerged as a solution that integrates intelligent control devices, residential-energy storage systems (ESSs), and various loads to enable a more efficient and sustainable lifestyle. The power electronics converter (PEC), as the power conversion interface of the smart home, is the key player in shaping the future of modern power grids.

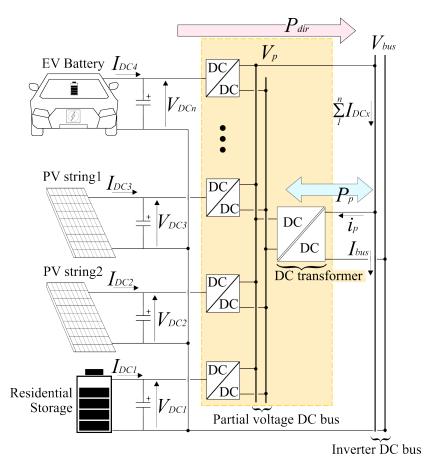

DC power conversion has recently become one of the important requirement for smart homes due to the increasing penetration of DC sources and DC loads, such as solar photovoltaic (PV) systems, residential-energy storage systems (ESSs), DC heatpumps, and LED lights. Since different types and numbers of DC sources and DC loads are connected to DC-DC converters, which provide power conversion between renewable energy sources (RESs) and DC loads, a multi-port architecture is required for the DC-DC converter in smart homes.

The key challenges for multi-port DC-DC converters are to increase efficiency and reduce the size, weight and cost of the PEC interfaces. Achieving these goals will not only improve the performance of smart homes, but also contribute to the wider adoption of renewable energy and sustainable living. The PEC interfaces have traditionally used a full power processing (FPP) DC-DC converter architectures that process the full voltage and full current of the input sources. However, the recent researches show that the partial power processing (PPP) architectures can further reduce the aforementioned challenges of the conventional FPP architectures. The PPP architectures allow the DC-DC converters to process only a part of the power, hence reducing the losses on the PEC interfaces. In addition, the volume and costs of the active and passive components also can be reduced by utilizing lower power ratings in the DC-DC converters compared to FPP. Therefore, the use of PPP DC-DC converters can increase efficiency by reducing the power processing, and achieve volume and costs reduction by using the lower power rating devices respect to non-partial power processing DC-DC converters (or FPP).

The main focus of this thesis is to reduce the losses, volume, and costs of the conventional FPPs. In order to achieve the objective of the study, a novel multi-port partial power converter (PPC) architecture is proposed. The topology of the proposed architecture is optimally

selected through the analytical investigation. The control of the proposed multi-port PPC is introduced and the parameter selection of the control is provided. The parameters of the hardware are also optimally designed based on the parameter design guide provided in the thesis. Finally, the proposed architecture is realized with the laboratory scale prototype. In addition, the operating principle and power processing concept of the proposed architecture is validated with the prototype..

# 1.2 Research proposal

This thesis aims to develop a novel DC-DC multi-port PPC architecture for the smart home application, which targets on enhancing the efficiency of the DC-DC converter stage and reduce the volume of the converter. The thesis focuses on the development of operation solutions in three different aspects:

Target I: A novel PPC architecture and its optimization respect to all the different stages

The first research target is to propose a novel PPC architecture and optimize its topology in order to find the best trade off between the losses and volume of the DC-DC converters. The operating point and the ratings of the proposed PPC will be specified based on the market analysis. Several DC-DC converter topologies are investigated for the multi-port PPC architecture. Since, the aim of the proposed multi-port PPC architecture is to achieve high efficiency, the most optimal topology for the proposed PPC should be selected by comparing the losses of all possible topology combinations.

Target II: Design and optimization of the control and power conversion parameters

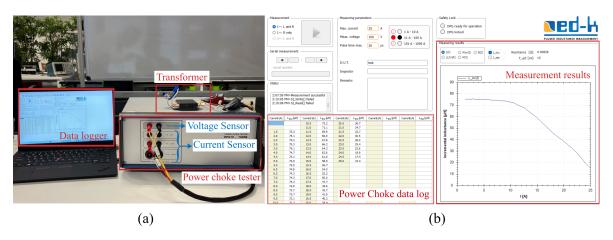

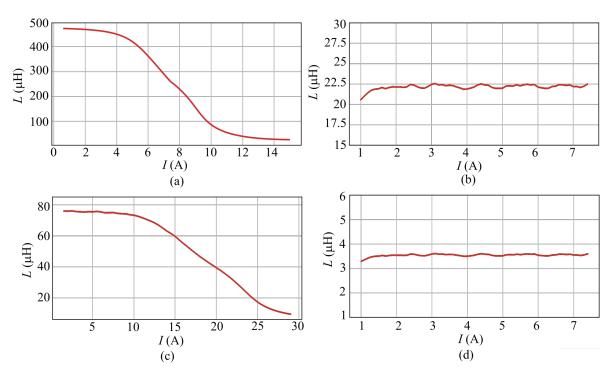

The second research target is to provide guidance on the parameter determination for the novel PPC architecture. Firstly, the control method of the proposed architecture is provided to clarify the operating principle of the converter. The control parameters of the proposed architecture should be designed based on the model of the proposed multi-port PPC. The hardware parameters are also optimally selected to achieve the target current and voltage ripple by using optimal inductance and capacitance. Based on the designed parameters, the optimal commercial element selection method is discussed. Furthermore, the transformer of the proposed PPC is precisely designed to achieve the expected behavior as the theoretical model. The designed parameters, simulation results and actual parameter values are compared to prove the accuracy of the transformer design.

#### Target III: Validation of the proposed PPC architecture

The third research target is to validate the novel PPC architecture. The relationship between the processed power on the proposed multi-port PPC and the losses will be analyzed. Based on the loss analysis, the efficiency of the proposed PPC will be estimated. The total volume and weight will be measured to obtain the power density of the prototype. The operating concept of the proposed PPC will be validated by the experimental results with the lab scale prototype. Finally, the efficiency will be measured using the power analyzer and compared with the estimated efficiency.

# 1.3 Structure of the thesis

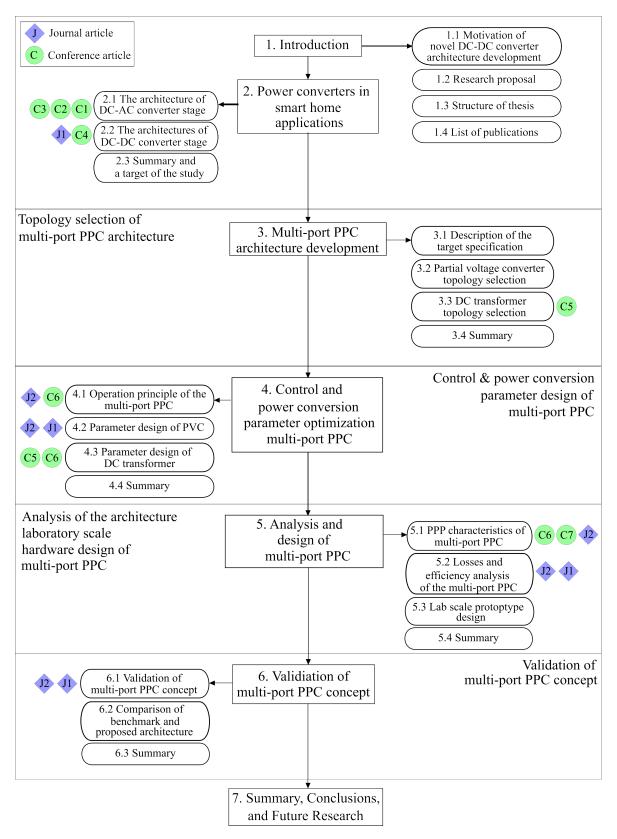

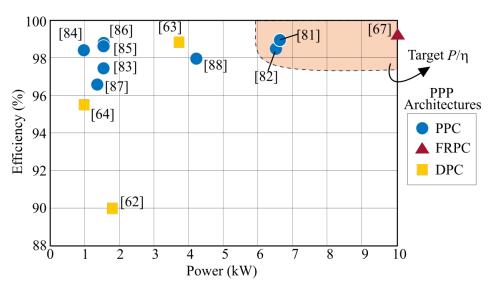

The structure of this thesis is shown in Fig. 1.1. An introduction to smart home applications and their structure is given in Chapter 2. An DC-AC power conversion interface between the AC grid and a DC grids in the smart home is one of the necessary function that required for a smart home architecture. Therefore, an inverter, which performs the DC-AC power conversion, is briefly explained to give a short introduction about its control method of each off-grid and grid-connected modes. Furthermore, two different grid synchronization methods for the grid connected modes are compared in order to analyze the effect of the grid synchronization block on the stability of the inverter control. As discussed earlier, a DC-DC power conversion stage is the main focus of the thesis that targets the efficiency and volume optimization. The DC-DC converter architectures are categorized according to their power processing characteristics. The conventional full power DC-DC converter architectures in the smart homes are described. The different state of the art DC-DC converter architectures and their power processing principles are also analyzed. The efficiencies of the most related articles are also compared to benchmark the peak efficiencies achieved by the state of the art technology.

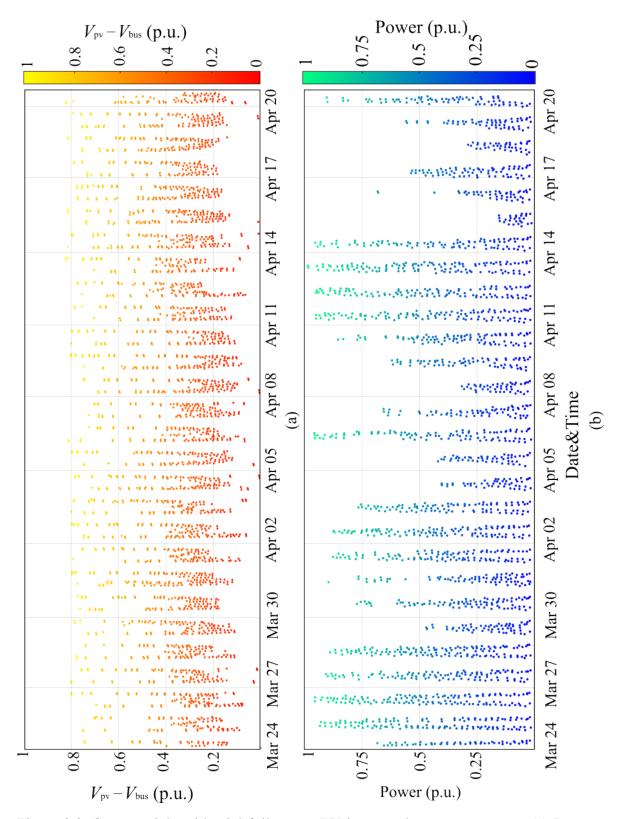

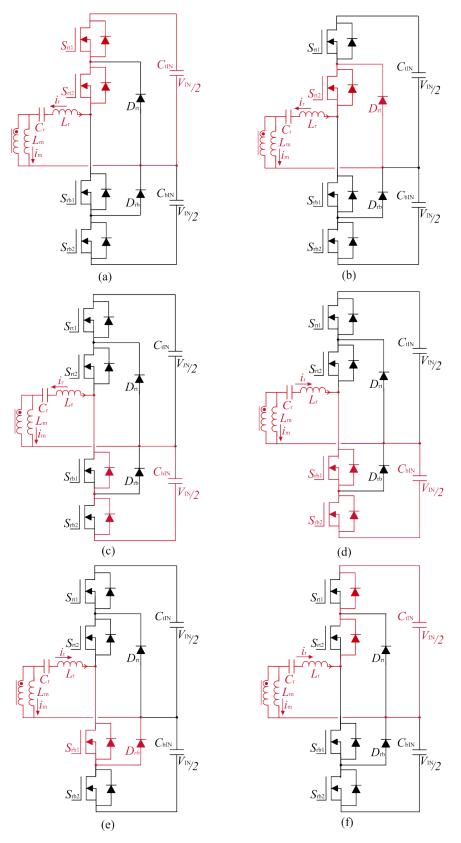

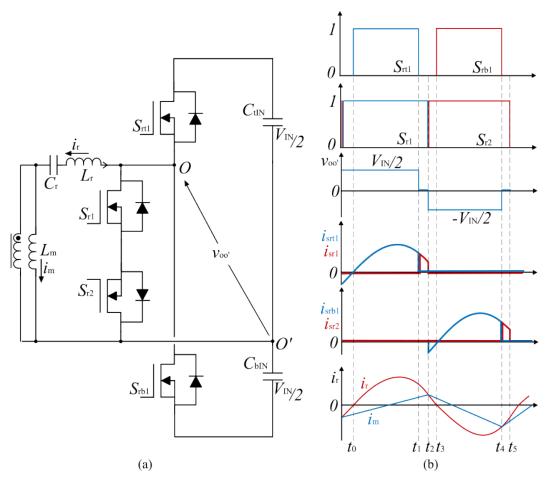

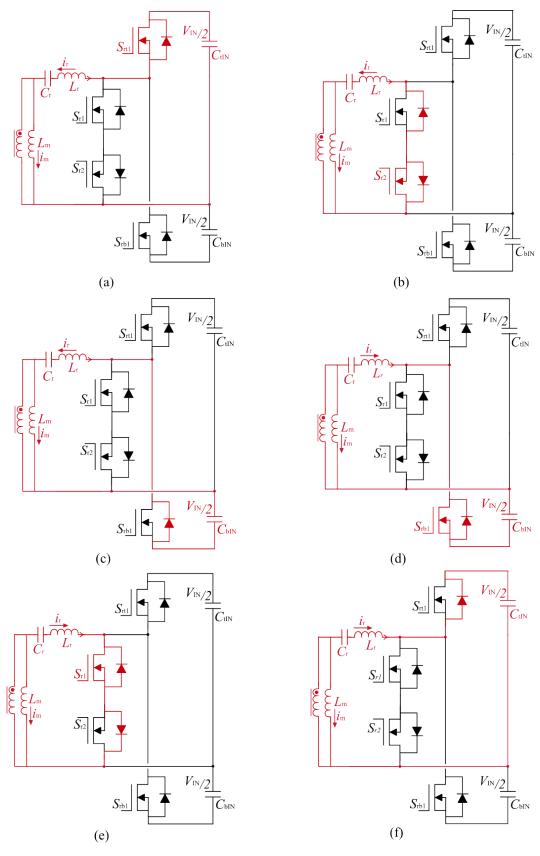

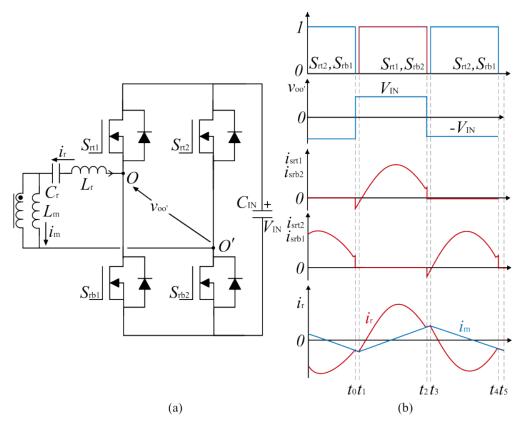

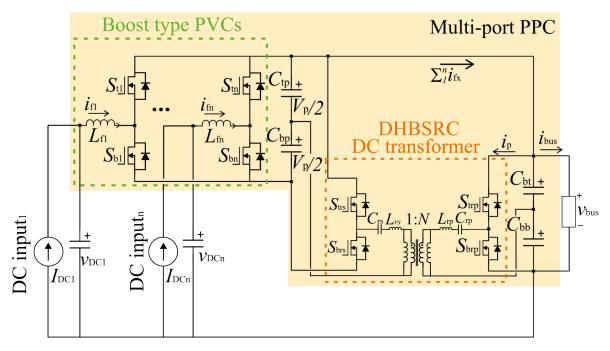

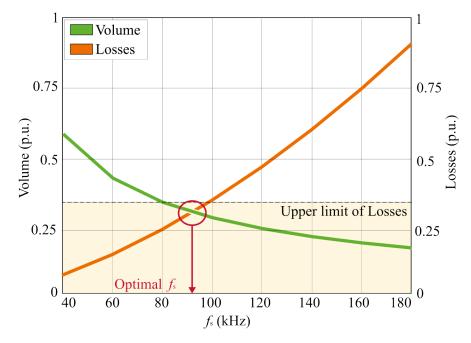

Chapter 3 describes a proposed multi-port PPC architecture with the topology selection. Before going into the detailed topology selection, the target operating range and power ratings of the proposed architecture are decided based on the market research. The topology of the first stage, which is called the partial voltage converter stage, of the proposed architecture is selected by finding an optimal trade of point between losses and volume of it. In addition, the switching states and operating modes of different topology options for the PVCs are provided. The DC transformer is the other stage whose topology needs to be selected. The isolated converters with bidirectional power control capability are considered for the topology options. For the smart home applications, a wide load condition should be considered due to the different DC interfaces (PV, EV and home storage). Therefore, the isolated converter with wide load ZVS capability is considered for the DC transformer stage. Furthermore, after selecting the topology, the primary and secondary bridges of the DC transformer are also selected by finding an optimal trade off point between the losses and volume.

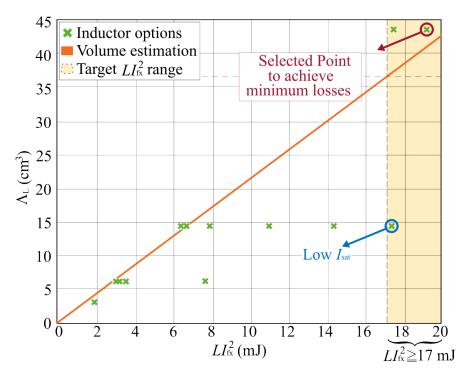

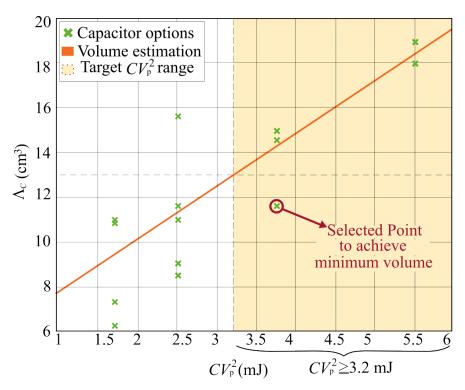

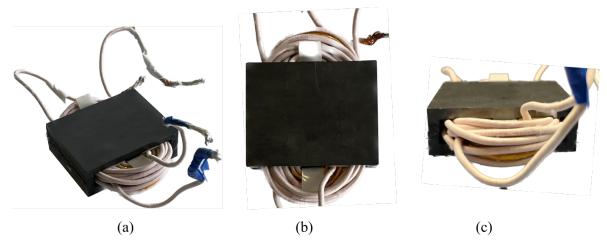

Chapter 4 presents the control scheme of the proposed multi-port PPC and its parameter design. The control and operating principle of the proposed architecture is given with the block diagram. The power conversion parameters of the PPC are selected to achieve the target current and voltage ripple. The commercial inductor and capacitor selection guide is also provided. The parameters of the DC transformer are also designed to achieve the target gain. Based on the selected parameters, the transformer is modeled and realized to obtain the close matching parameters between the theoretical design. The target parameters, the theoretical model and those of the realized transformer are compared to check the accuracy of the transformer model.

The analysis of the proposed PPC and the construction of the laboratory prototype hardware, including heatsink, is carried out in Chapter 5. The partial power processing has a significant impact on the losses of the converter. Therefore, the power processing characteristics of

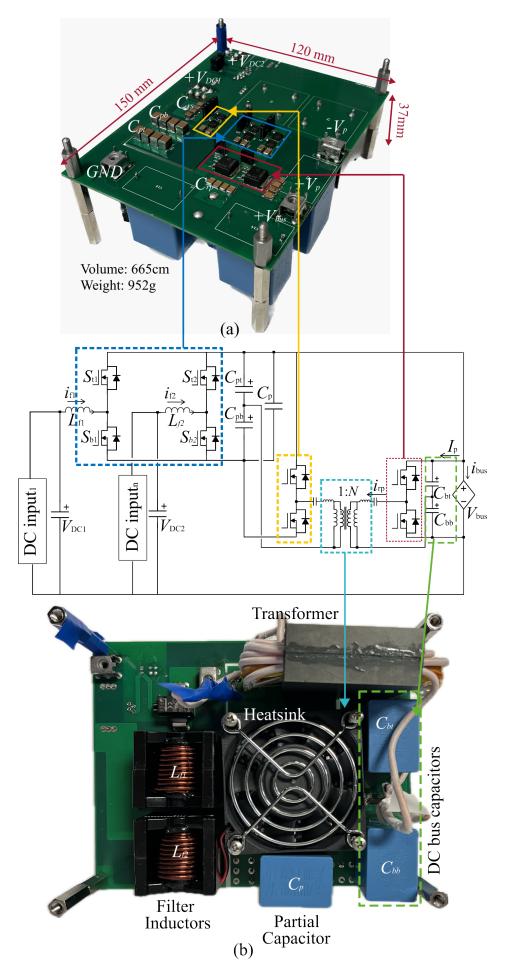

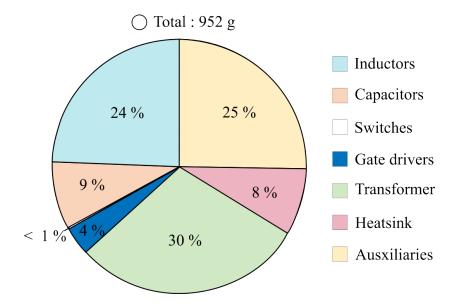

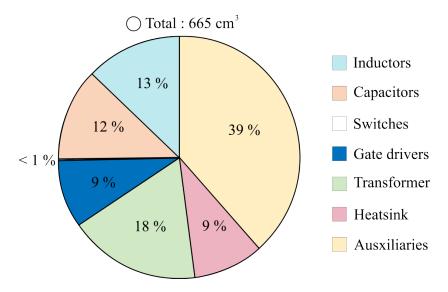

the proposed multi-port PPC are analyzed using the utilization factor and the partial power processing ratio, which are the indicators to show the amount of power processing. Then, the efficiency and losses of the multi-port PPC are analyzed to validate the relationship between the PPP characteristics of the proposed architecture. The lab scale prototype is built based on the selected parameters and the heatsink selection for the prototype is also performed. The volume and weight of the prototype are measured to verify the power density.

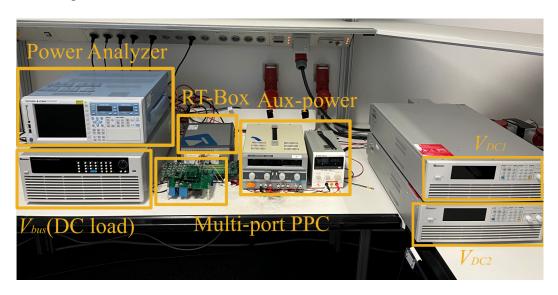

In Chapter 6, the concept and performance of the proposed multi-port PPC are validated by the experiments. Finally, the benchmark and proposed architectures are compared to highlight the improvements of the proposed solution.

Chapter 7 summarizes the results and provides the conclusions. The performance of the proposed multi-port PPC is concluded. Finally, an outlook on future work is given.

# 1.4 Assignment of publications to the chapters of this thesis

## Journal papers

- J1 Y. D. Kwon, F. Freijedo, T. Wijekoon, and M. Liserre, "Series Resonant Converter Based Full-Bridge DC-DC Partial Power Converter for Solar PV," *in IEEE Journal of Emerging and Selected Topics in Power Electronics*, vol. 12, no. 2, pp. 1719-1729, April 2024.

- J2 Y. D. Kwon, F. Freijedo, T. Wijekoon, and M. Liserre, "A multi port partial power converter for smart home applications," *in IEEE Transactions on Power Electronics*, vol. 39, no. 7, pp. 8824-8833, July 2024.

#### **Conference Proceedings**

- C1 Y. D. Kwon, R. Zhu, M. Liserre, B. McGrath, A. A. Nazib, D. G. Holmes, P. Mu, "Impedance-based Stability Assessment of Self-Synchronising Power Electronics Converter," *in 2020 International Power Electronics Motion Control Conference (IPEMC-2020-ECCE Asia)*, 2020, pp. 2116-2121.

- C2 R. Zhu, Y.D. Kwon, M. Liserre, A. A. Nazib, D. G. Holmes, B. McGrath, "Phase Angle Compensation-based Highly Accurate Self-Synchronising Inverter," *in 2020 International Power Electronics Motion Control Conference (IPEMC2020-ECCE Asia)*, 2020, pp. 2088-2092.

- C3 S.Pugliese, Y. D. Kwon, and M. Liserre, "Positive-Negative Sequence SRF-PLL Model for Accurate Stability Analysis in Grid-Tied Converters," *in 2020 IEEE Energy Conversion Congress and Exposition (ECCE)*, 2020, pp. 3593-3600.

- C4 Y. D. Kwon, F. Freijedo, T. Wijekoon, and M. Liserre, "Partial Power Processing DC/DC MPPT Converters in Solar PV Applications: Overview of Architectures," in 2022 IEEE International Symposium on Power Electronics for Distributed Generation Systems (PEDG), 2022, pp. 1-6.

- C5 Y. D. Kwon, T. Wijekoon, F. Freijedo, and M. Liserre, "Bidirectional Multi-Port Partial Power Converter for Solar PV Applications," in PCIM2023; International Exhibition and Conference for Power Electronics, Intelligent Motion, Renewable Energy and Energy Management, 2023, pp. 1-7.

- C6 Y. D. Kwon, F. Freijedo, J. Olschewski, T. Wijekoon, and M. Liserre, "Design and Optimization of CLLC Converter Enabling Highly-Efficient Partial Power Processing for Solar PV Applications," in PCIM2023; International Exhibition and Conference for Power Electronics, Intelligent Motion, Renewable Energy and Energy Management, 2023, pp. 1-8.

- C7 Y. D. Kwon, F. Freijedo, T. Wijekoon, and M. Liserre, "Combined Partial Voltage and Current Power Processing DC/DC Converters for Solar PV applications," *in 2023 International Conference on Power Electronics and ECCE Asia (ICPE 2023 ECCE Asia)*, 2023, pp. 492-497.

Figure 1.1: Structure of the thesis and related publications.

# PV string2 DC-DC Converter PV string Inverter Grid DC DC AC $V_{bu}$ AC DC Residential Storage LED ligths AC Loads EV Battery DC heatpump

# 2 Power converters in the smart home application

Figure 2.1: Smart home applications and architecture.

The demand for clean and sustainable electrical energy has grown rapidly in recent years, with renewable energy powered smart home technologies becoming mainstream and cost-effective for self-sufficient domestic needs [1,2]. To transfer power between various sources and loads connected to the smart home, power electronic converters (PECs) are the core technology for such smart home technologies [3]. As shown in Fig. 2.1, the smart home architecture has two power conversion stages: i) the DC-AC power conversion stage to supply the power to the loads and the grid connection, and ii) the DC-DC power conversion stage, which has the multi-port DC inputs to connect the DC loads and DC sources.

The inverter, which is the PEC for the DC-AC power conversion, can operate in two modes. If there is no grid connection, the inverter supports the power supply to the AC loads. In this mode, the power for the home appliances can be supported by the energy from renewable energy sources (RESs). On the other hand, if there is more power available than the AC loads require, the inverter can feed the power directly into the grid. In addition, if there is no power generation from the RESs, the inverter should control the DC bus voltage to supply the power to the DC loads through the grid connection.

On the DC side of the smart home, there are devices such as renewable energy sources, energy storage devices such as batteries and electric vehicles (EVs), and different types of loads such as DC pumps or LED lighting. In a given smart home layout, multiple modes of energy exchange between renewable sources, storage elements and loads can coexist [4]. For example, during a day, photovoltaic (PV) panels can directly power household appliances,

and any excess energy can be used to charge the residential-ESSs or electric vehicles (EVs). In the absence of solar, the residential-ESSs can support the necessary loads in the home appliances to increase self-consumption, while also providing a backup source in the event of a grid blackout [5–7]. The multiple DC sources and DC loads can be considered as a DC micro-grid connected to the common DC bus on the inverter side [8–10].

To handle the power from multiple DC sources and to DC loads, a multi-port converter architecture is required [11–15]. The multi-port converter architectures can be categorized according to their power processing characteristics: full power processing converters and partial power processing converters. The detailed categorization of the multi-port DC-DC converter architecture that has been studied recently should be reviewed and compared.

This chapter provides a brief introduction to the DC-AC power conversion strategy in grid forming mode and grid following mode. In addition, the effect of the grid synchronization methods, which is one of the key technologies for the grid following mode, on the control stability is presented. Next, the multi-port DC-DC converter architectures are categorized according to their power processing characteristics. The power processing of each architecture is visualized using a volt-ampere (VA) area model. A review of the state of the art multi-port architectures are compared by the table. Finally, the benchmarks and targets of the study is specified based on the comparisons of the state of art multi-port architectures.

# 2.1 DC-AC converter stage control

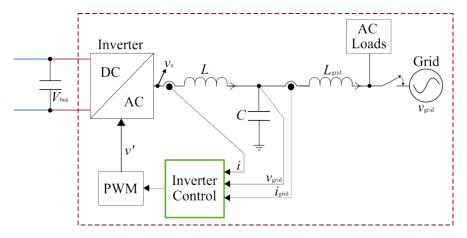

Figure 2.2: inverter configuration for smart home and its control block diagram.

DC-AC power conversion is required to drive the AC loads and to make the connection to the grid. A general smart home inverter configuration and its control block diagram is shown in Fig. 2.2. The inverter can be connected either to AC loads or to the grid. Depending on its connection, the inverter can be operated in two modes: grid forming mode and grid following mode.

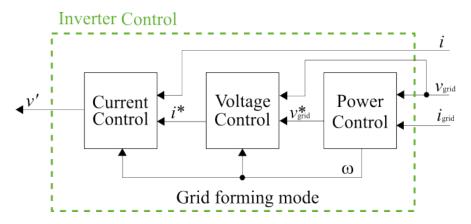

Figure 2.3: Control block diagram of grid forming mode.

# 2.1.1 Grid forming mode

If the smart home provides the power to the AC loads without being connected to the grid, the inverter should be operated in grid forming mode, where the inverter forms the grid to drive the AC loads [16–18]. As shown in the block diagram in Fig. 2.3, the grid forming mode consists of three loops [19–21]. The first loop is the external power control loop, which derives the voltage amplitude and frequency information for the voltage control [22–25]. This can be done by following the droop characteristics of the active and reactive power. The second loop is for the voltage control of the grid voltage and its frequency, which controls the grid voltage and its frequency [26–28]. The third loop is the current loop, which controls the current by following the frequency and phase of the grid voltage. Finally, the inverter can form the grid with the optimum voltage derived from the grid forming mode control.

#### 2.1.2 Grid following mode

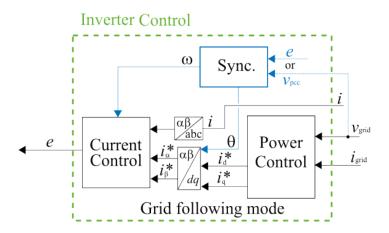

Figure 2.4: Control block diagram of grid following mode.

If the RESs generates more power than the AC load demands, the inverter can connect to the grid and the redundant power from RESs can be supplied to the grid [29–32]. The grid following mode control block is shown in Fig. 2.4. The external power control loop provides the dq current references on the synchronous axis. The dq axis current is converted to the

$\alpha\beta$  current and applied to the current control. In grid following mode, the inverter should be able to track the grid angle and magnitude to inject or absorb the active and reactive power to the grid in order to comply with the grid codes. A grid synchronization technique is required to meet the grid code requirements and also to synchronize with the frequency and phase of the grid. One method of the grid synchronization is using a phase locked loop (PLL) by directly measuring the grid voltage ( $v_{pcc}$ ). Another method is using a self-synchronization by obtaining the grid voltage information (e) indirectly from the internal current control.

## **Grid synchronization methods**

The synchronization block can provide the frequency and phase angle information for the current control. There are two ways of synchronization with the grids. The first is to measure the grid voltage directly and to calculate the frequency and phase information using the phase locked loop (PLL) [33–36]. The second method is to use the indirect phase information from the control and calculate the phase information. This method is called self-synchronization method [37–39].

#### A. Phased locked loop

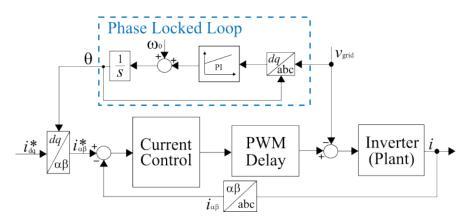

Figure 2.5: Control block diagram of phase locked loop (PLL).

The control block of the PLL is shown in Fig. 2.5. The PLL tracks the phase angle of the grid by the measured grid voltage. The block diagram shows that the direct grid voltage measurement creates a closed loop between the grid voltage ( $v_{\rm grid}$ ) and the input reference currents ( $i_{\rm dq}^*$ ). This loop has an effect not only on the stability of the current control, but also on the stability of the inverter. This means that the PLL based on measuring the grid voltage can degrade the stability of the inverters because the PLL provides an additional path for the harmonics to propagate through the control loop of the inverters [40,41].

#### **B. Self-Synchronization**

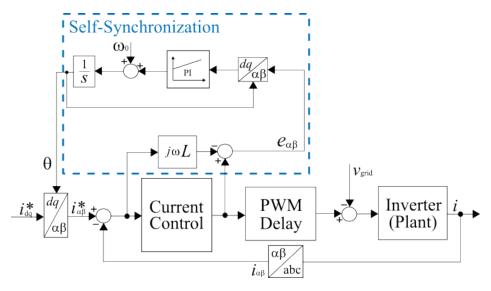

The self-synchronization is an alternative synchronization method for grid connected inverters which control block is depicted in the Fig. 2.6. In the self synchronizing inverters, the grid voltage measurement is no longer required. The phase information of the grid is obtained by using the internal signals from the current control of the inverters. Let the vector

Figure 2.6: Control block diagram of self synchronization.

$\vec{Z} = Ze^{j\omega_0 t}$ , then the relationships of the voltages on the stationary frame in Fig. 2.2 can be written as follows:

$$\vec{v_{\rm n}} = L \frac{d\vec{i}}{dt} + \vec{v}_{\rm grid} = j\omega_0 L \vec{i}$$

(2.1)

where L is the filter inductance of the inverter,  $\vec{v_n}$  (c.f. Fig. 2.2),  $\vec{v_{grid}}$ ,  $\vec{i}$  are the vectors of the inverter leg voltage, the grid voltage, and the inverter filter current respectively.

In order to control the stationary frame currents  $(i_{\alpha\beta})$ , the resonant control should be employed for the inverter. The  $\vec{v_n}$  of the resonant control applied system can be obtained as:

$$\vec{v_{\rm n}}(s) = \left(k_{\rm p} + \frac{k_{\rm r}s}{s^2 + \omega_0^2}\right) (\vec{i}_{\alpha\beta}^* - \vec{i}_{\alpha\beta}) \approx \frac{k_{\rm r}s}{s^2 + \omega_0^2} (\vec{i}_{\alpha\beta}^* - \vec{i}_{\alpha\beta})$$

(2.2)

where  $k_{\rm p}$  and  $k_{\rm r}$  are the proportional and resonant gains,  $\omega$  is the resonant frequency,  $i_{\alpha\beta}^*$  is the reference stationary frame currents.

Put (2.2) in (2.1),  $v_{grid}$  can be derived as follows:

$$\vec{v}_{\text{grid}}(s) \approx e_{\alpha\beta} = \frac{k_r s}{s^2 + \omega_0^2} (\vec{i}_{\alpha\beta}^* - \vec{i}_{\alpha\beta}) - j\omega_0 L_f \vec{i}$$

(2.3)

(2.3) shows that the grid voltage information can be indirectly derived from the resonant controller in the self-synchronization applied inverters instead of direct measurement of ac grid voltages by voltage sensors as the PLL applied inverters. Therefore, unlike the control loops of the PLL applied inverters, self-synchronization does not have closed loop from grid voltage to current reference. This means that the synchronization does not affect the system stability.

## Impedance based stability analysis

Since the impedance of the inverter is influenced by the synchronization unit, the impedance-based stability approach is used. An impedance-based stability criterion is the stability analysis method which based on the ratio of input to output impedance and the phase difference between two connected systems. The analysis can characterize the frequency response of the inverter output impedance and intuitively show the impacts caused by the synchronization unit [42]. Therefore, the stability of the synchronization methods can be systematically studied taking into account the bandwidth variation of the grid synchronization, the variation of inverter impedance, and the operating point.

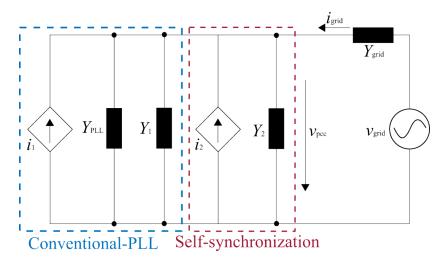

Figure 2.7: Interaction caused by grid impedance and inverter impedance.

The impedance-based model of the conventional PLL based inverter and the self-synchronizing inverter are compared in Fig. 2.7. In the figure,  $Y_1$  is the admittance from  $v_{\rm grid}$  to i without considering the PLL unit, and  $Y_{\rm PLL}$  is the impedance that only caused by the PLL (the loop from  $v_{\rm grid}$  to PLL and then to i, as shown in Fig. 2.5) in the conventional PLL based inverter.  $Y_1$  and  $Y_{\rm PLL}$  are denoted as the inverter admittance and PLL admittance respectively.  $Y_2$  is the output admittance of the self-synchronizing inverter.  $Y_{\rm grid}$  is the grid admittance. As discussed earlier, the total output impedance of the conventional PLL based inverter is equal to parallel admittance of  $Y_1$  and  $Y_{\rm PLL}$ . Based on Fig. 2.7, the interaction caused by impedance can be expressed as:

$$v_{\text{pcc}}(s) = (i_{\text{grid}} - i_1 - i_2)(Y_1 + Y_2 + Y_{\text{PLL}} + Y_{\text{grid}}) + \frac{Y_{\text{grid}}}{Y_1 + Y_2 + Y_{\text{PLL}} + Y_{\text{grid}}} v_{\text{grid}}$$

(2.4)

The equation shows that the interaction between the inverter and grid can be caused by the impedance.

The total admittance of the conventional PLL and the self-synchronizing inverter can be obtained as follows:

$$Y_{\text{tot}_{PLL}} = Y_1 + Y_{\text{PLL}}$$

$$Y_{\text{tot}_{self}} = Y_2$$

(2.5)

As explained earlier, the admittance of the PLL which is  $Y_{PLL}$  is derived from the loop between  $v_g$  and  $\theta$ . Hence, based on (2.3), the parameter of the grid side filter inductance can impact on the stability of conventional PLL based inverter. On the other hand, stability of the self-synchronizing inverter does not have the loop between the grid synchronization. Hence the stability is only determined by the admittance of inverter  $Y_2$ .

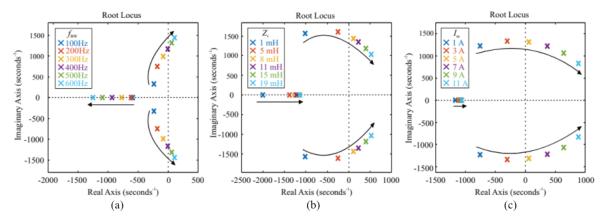

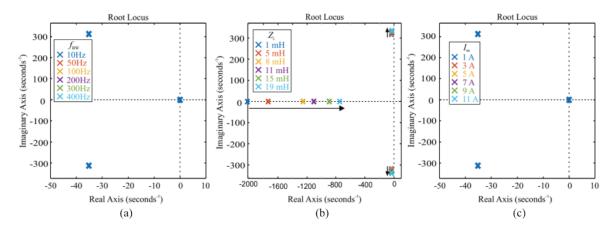

A root locus can be plotted based on the admittance model in order to analyze the stability of the conventional PLL and the self-synchronization inverters. The root locus of the PLL based is shown in Fig. 2.8. Fig. 2.8 (a) shows that the impact of the PLL bandwidth on the behavior of roots of the conventional PLL based inverter when filter inductance L=8mH and the current amplitude  $I_{\rm m}=5$  A. The system poles move to the right half plane and cross the imaginary axis by increasing the PLL bandwidth  $f_{\rm BW}$ , from 100 Hz to 600 Hz. As a result, the PLL bandwidth is limited by the system stability concern. In Fig. 2.8 (b), the impact of L variation on the roots of the conventional PLL based inverter is plotted. To see the impact of L change, the PLL bandwidth  $f_{\rm BW} = 600$  Hz and the amplitude of the current reference  $I_m = 5$  A. The system poles move to the right half plane as well by increasing L from 1 mH to 19 mH. This diagram indicates that the parameter of L can impact on the stability of the conventional PLL based PECs. Fig. 2.8 (c) shows the impacts of current reference in the conventional PLL-based PECs, when the PLL bandwidth  $f_{\rm BW}=600$  Hz, the filter inductance L=8 mH. The  $I_{\rm m}$  is increased from 1 A to 11 A and it is shown that the  $I_m$  makes the system unstable. The analysis shows that the grid voltage measurement PLL on the system stability of inverters. The results show that a high bandwidth of the PLL and a high amplitude of the injected current will both challenge the stability of grid-connected inverters. Therefore, in order to ensure stability of the conventional PLL-based inverter, all of these three constraints of  $f_{BW}$ , L, and  $I_{m}$  must be considered for the system stability.

Figure 2.8: Root Locus of the conventional PLL based system under (a) PLL bandwidth variation (L=8 mH and  $I_m=5$  A), (b) filter inductance variation ( $f_{\rm BW}=600$  Hz and  $I_{\rm m}=5$  A), and (c) current reference variation ( $f_{\rm BW}=600$  Hz and L=8 mH).

Figure 2.9: Root Locus of the self-synchronization system under (a) PLL bandwidth variation (L=8 mH and  $I_{\rm m}=5$  A), (b) filter inductance variation ( $f_{\rm BW}=600$  Hz and  $I_{\rm m}=5$  A), and (c) current reference variation ( $f_{\rm BW}=600$  Hz and L=8 mH).

In contrast, the impacts of these three constraints on the stability of the self-synchronizing inverters are shown in Fig. 2.9. Fig. 2.9 (a) shows  $f_{\rm BW}$  of the self-synchronizing inverter does not change the roots of the inverter. This validates that the self-synchronization does not impact on the inverter impedance. In Fig. 2.9 (b) shows that the impact of L variation on roots of the self-synchronizing inverter. The change of roots are also smaller as compared to the conventional PLL based inverter that shown in Fig. 2.8 (b). Finally,  $I_{\rm m}$  neither affect to the output impedance of self-synchronization inverter, as shown in Fig. 2.9 (c). The Fig. 2.8 and Fig. 2.9 validates that the self-synchronizing inverters are more robust and stable than the conventional PLL-based inverters.

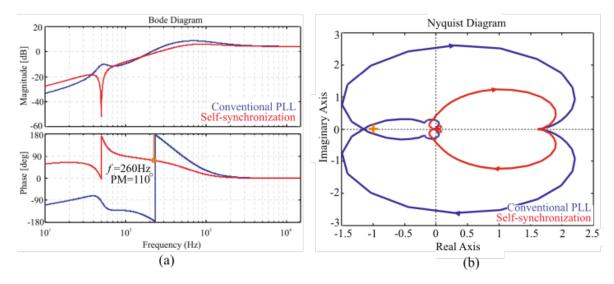

In order to evaluate the impact of synchronization units bandwidth on the inverters, the impedance based stability analysis is used, based on the admittance model as shown in Fig. 2.7. Fig. 2.7 (a) shows the bode diagram of the conventional PLL and self-synchronizing inverter. The figure shows that the conventional PLL based inverters does not have any phase margin. Hence, the PLL based inverter can be unstable when  $f_{\rm BW} = 600$  Hz, L = 8 mH and  $I_{\rm m} = 8$  A. On the other hand, the self-synchronizing inverter has enough stable margin.

The Nyquist diagram also presents the clear results as shown in Fig. 2.10 (b). The conventional PLL-based inverters are unstable while it encircle the critical point (-1,0). On the other hand, the self-synchronizing inverters do not encircle the critical point. All of the aforementioned analysis validate that the self-synchronizing inverters is more stable and robust against the  $f_{\rm BW}$ , L, and  $I_{\rm m}$  changes.

## Simulation and experimental results

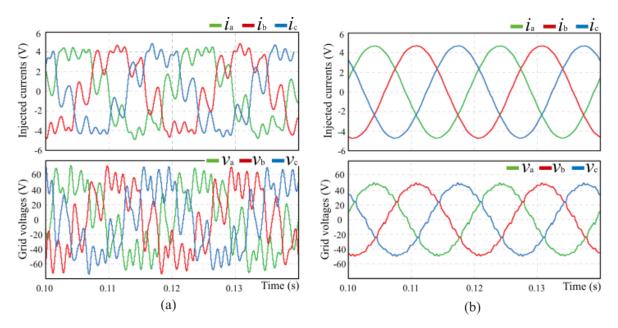

The simulation and experiments are carried out in order to validate the theoretical analysis with a 4 kW inverter. The electrical and control parameters of the system are organized in Table. 2.1.

The simulation results of three phase grid currents and voltages of PLL based and self-synchronizing based inverters are shown in Fig. 2.11 (a) and Fig. 2.11 (b), respectively. Fig.

Figure 2.10: (a) Bode diagram of impedance based model and (b) Nyquist diagram of impedance based model.

Table 2.1: Simulations and experimental parameters

| Parameters                   | Symbol           | Value | Unit |

|------------------------------|------------------|-------|------|

| Grid voltage amplitude       | $V_{ m grid}$    | 50    | V    |

| Grid frequency               | $f_{ m grid}$    | 50    | Hz   |

| Grid inductance              | $L_{ m grid}$    | 5.6   | mH   |

| Rated power                  | Prated           | 4     | kW   |

| Switching frequency          | $f_{ m inv}$     | 10    | kHz  |

| Filter inductance            | L                | 8     | mH   |

| Filter capacitance           | C                | 5     | μF   |

| PLL Bandwidth                | $f_{ m BW}$      | 600   | Hz   |

| Proportional gain of current | $k_{\mathrm{p}}$ | 15    | -    |

| Resonant gain of current     | $k_{\rm r}$      | 1550  | -    |

Figure 2.11: Simulation results of injected currents and grid voltages: (a) conventional PLL based inverter and (b) self-synchronizing inverter (parameters in Table. 2.1).

2.11 (a) shows that the three phase currents and grid voltages are seriously distorted because of the combination on the high  $f_{\rm BW}$  and  $Z_{\rm L}$ . In contrast, three phase current and the grid voltages are stable with the self-synchronization as shown in Fig. 2.11 (b). Therefore, the simulation results in Fig. Fig. 2.11 (a) and Fig. 2.11 (b) show that the theoretical analysis are valid.

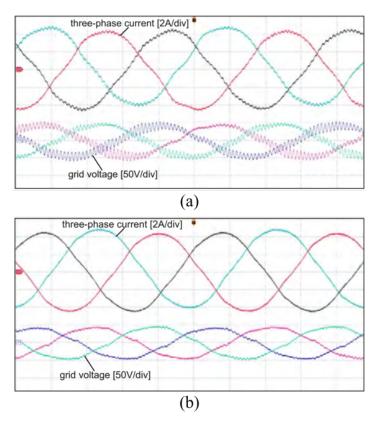

The experimental results in Fig. 2.12 (a) show the injected current and grid voltage of the inverter with the conventional PLL when  $f_{\rm BW}=600$  Hz. The experimental results show that the injected grid currents and voltages are distorted at high  $f_{\rm BW}$ . The stability of PLL can be degraded by the PLL impedance as the analysis in Fig. 2.8. In the experiment parasitic parameters of ac filter, converter and isolated transformer are existed, hence the amplitude of resonance in the injected currents is slightly different from the simulation results in Fig. 2.11 (a).

The three phase currents and grid voltages of the self-synchronizing inverter are measured as shown in Fig. 2.12 (b) which experiment has been conducted under the same condition as in Fig. 2.12 (a). As discussed before in the impedance based stability analysis,  $f_{\rm BW}$  change of the self-synchronization does not impact on the stability of PEC. The self-synchronizing inverter shows less distortion with higher current and voltage quality, in contrast to the conventional PLL based inverter even with the  $f_{\rm BW}=600$  Hz. The experimental results also proves that the stability of self-synchronizing inverter is not affected by the  $f_{\rm BW}$ , as the analysis results in Fig. 2.9 shows. Therefore, from the experimental results, it can be concluded that the self-synchronizing inverters have advantage in terms of the stability compared to the conventional PLL based inverters.

Figure 2.12: Experimental results comparison of (a) the conventional PLL based inverter, and (b) self-synchronizing inverter.

# 2.2 The architectures of DC-DC converter stage

The DC-DC converter stage of the smart home application is highlighted in Fig. 2.1 with the blue color. The DC bus voltage on the inverter side is higher than the DC input voltages. Therefore, a boost type DC-DC converter is used for the smart home applications [43–45]. Multiple sources and DC loads are connected to the input side of the multi-port DC-DC converter. The DC-DC converter has the capability to process the power between the DC sources and loads. The output side of the DC-DC converter is connected to the DC bus of the inverter. The architecture of the DC-DC converter can be categorized according to its power processing characteristics.

#### 2.2.1 Full power processing DC-DC converter architecture

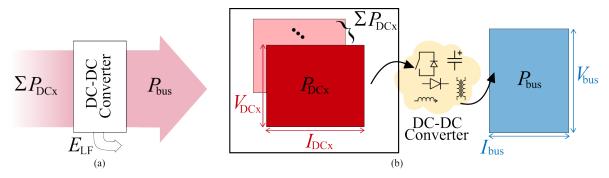

A full power processing (FPP) architecture is one of the most common power processing architectures in the industry. The power processing characteristics of FPP can be described by a power flow diagram and the volt-ampere (VA) area model are shown in Fig. 2.13.

The power flow diagram in Fig. 2.13 (a) shows the power processing of the DC-DC converters in the FPP architecture. Following the energy conservation principle, the relationship between the input and output power can be expressed as  $\Sigma P_{\text{DCx}} = P_{\text{bus}}$ , the relationship can be reorganized as:

Figure 2.13: Power processing nature of full power processing (FPP) architectures: (a) power flow diagram and (b) VA area model.

$$\Sigma V_{\rm DCx} I_{\rm DCx} = V_{\rm bus} I_{\rm bus} \tag{2.6}$$

The equation shows that the total power of the DC input ( $\Sigma P_{DCx}$ ) is processed by the DC-DC converters and delivered to the output. Therefore, in order to build the DC-DC converter that processes  $\Sigma P_{DCx}$ , the full voltage and full current rated semiconductor devices that have the same level as the system power are required. The DC-DC converter for the FPP is called a full power converter (FPC). The losses of the FPCs are caused by the power dissipation of the power electronics components. As shown in the figure, the losses ( $P_{LF}$ ) of FPCs are caused by the DC-DC converters processing  $\Sigma P_{DCx}$ .

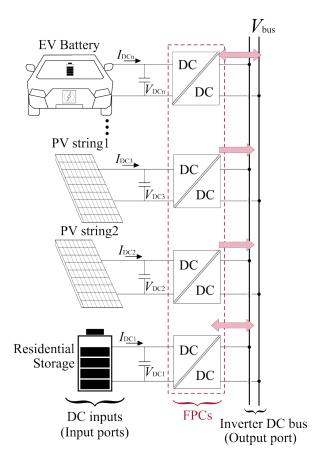

The first multi-port FPP architecture option is to use n-number of FPCs for each port, as shown in Fig. 2.14. The architecture shows that the multiple individual FPCs are connected to each DC input ( $V_{DCx}$ ). Therefore, the FPCs control the voltage and current for each connected renewable energy source and DC load. The output of each FPC is connected to the common DC bus on the inverter side. The architecture can use the different FPC topologies that are suitable for each DC input port requirements for the smart home applications [46]. Therefore, each converter function is limited by the designated DC inputs to which the converter is connected.

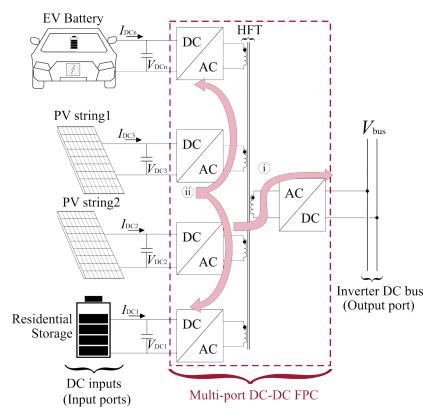

The second possible multi-port FPP architecture is to use multi-winding transformer, as depicted in Fig. 2.15. As shown in the figure, a multi-winding high frequency transformer (HFT) is used between the AC-DC and DC-AC converters on  $V_{\rm bus}$  and  $V_{\rm DCx}$  respectively. The DC-DC converter topology that using HFT can be used to build the multi-port FPC, which is either a resonant converter or an active bridge converter topology. The power from the DC inputs can be converted from  $V_{\rm bus}$  to  $V_{\rm DCx}$  or from  $V_{\rm DCx}$  to  $V_{\rm DCx}$ . For example, (i) the power generated by the PVs can be fed into the  $V_{\rm bus}$  or (ii) the the EV battery or the residential-ESSs can be charged by the power from the PVs. The advantage of the multi-winding transformer based FPC architecture is that it provides a high modularity by using the same cell for each DC input. Although, the power can flow into two different directions, the multi-winding transformers are not widely used in the industrial applications due to their design complexity.

In order to build the multi-port FPP architecture, the ratings of the DC-AC converter at the

Figure 2.14: Multi-port FPP architecture using multiple FPCs.

output port should be designed to process the total power from the input demand. Therefore, the capacity of the DC-AC converter on the output port should be designed with a higher ratings than the input port. However, recent studies figured out that the converter can process a part of the power from the input by using a partial power processing (PPP) architectures.

#### 2.2.2 Partial power processing DC-DC converter architectures

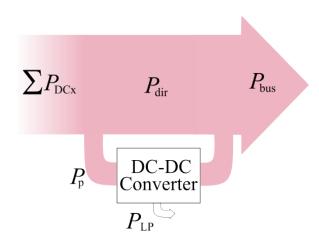

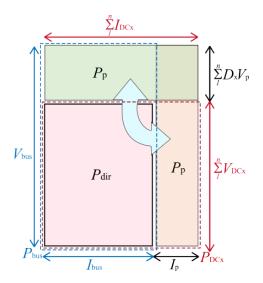

The PPP architectures have been introduced to reduce the voltage or current ratings of semi-conductor and passive devices [47–49]. The key difference of PPP between FPP is depicted in Fig. 2.16 by the power flow diagram.

The power flow diagram in Fig. 2.16 shows that the DC-DC converters in the PPP architecture process only the target partial power ( $P_p$ ). In the figure, the DC-DC converter processes  $P_p$  which is a part of  $P_{DCx}$ . The rest of the power  $P_{dir}$  is called a direct power ( $P_{dir}$ ) which is not processed by the DC-DC converter, and bypasses directly to  $V_{bus}$ . The power flow diagram shows that the DC-DC converter does not process full DC input power but the partial power, hence the architecture is called PPP. By using the PPP architecture, the lower power processing feature can provide the potential to build high efficiency, and high power density (PD) converters. Compared to FPP, the processed power on the DC-DC converter can be reduced due to processing partial power, which eventually can lead to a reduction in losses ( $P_{LP}$ ).

Figure 2.15: Multi-port FPP architecture using multi-winding transformer.

Figure 2.16: Power flow diagram of partial power processing (PPP) architectures.

In addition, the energy conservation equation of the PPP can be expressed by using the relationship in the diagram as:

$$\Sigma P_{\text{DCx}} = P_{\text{dir}} + P_{\text{p}} = P_{\text{bus}} \tag{2.7}$$

Considering the ideal power processing that ignores the losses, Fig. 2.16 and (2.7) shows that the energy conservation between  $P_{DCx}$  and  $P_{bus}$  of the PPP can be achieved by the summation of  $P_{dir}$  and  $P_p$ .

|              | PPP architecture |                        |                        |      |  |

|--------------|------------------|------------------------|------------------------|------|--|

| Topology     | DPC              | FRPC                   | PPC                    |      |  |

| Topology     |                  |                        | IPOS                   | ISOP |  |

|              | PV               | EV charging            | EV charging            |      |  |

| Applications |                  | PV                     | PV                     |      |  |

|              |                  | Residential<br>Storage | Residential<br>Storage |      |  |

Figure 2.17: Categorization of partial power processing (PPP) architectures.

The different types of the PPP architectures have been actively researched to improve the efficiency and PD for the different applications [50, 51]. The categorization of PPP architectures are depicted in Table. 2.17. The PPP architectures can be divided into three large categories: i) differential power converters (DPCs) [52–64], ii) fractional power converters (FRPCs) [65–71], and iii) Partial Power Converters (PPCs) [72–88]. The PPP concept of each architecture are visualized by the VA area model. The VA area model can be plotted by placing the voltage amplitude on the vertical and lying the current amplitude on the lateral [89]. In order to select the optimal PPP architecture for the smart home applications, the PPP architecture options have been investigated and compared.

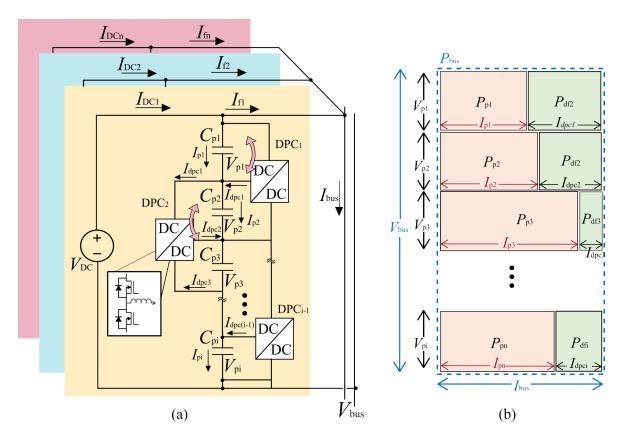

# Differential power converter

The architecture of differential power converters (DPC) is depicted in Fig. 2.18 (a). The input DC voltage  $V_{\rm DC}$  of the DPCs is separated by the multiple series capacitors ( $C_{\rm p1}$  to  $C_{\rm pi}$ ). The DPCs perform energy balancing between the sub-partial-DC voltages ( $V_{\rm p1}$  to  $V_{\rm pi}$ ) on  $C_{\rm p1}$  to  $C_{\rm pi}$ . Using the Kirchhoff's current law (KCL), the differential current processed on each DPCs can be expressed as follows:

$$I_{\text{dpc}_i} = I_{p_i} - I_{p_{i+1}} + D_{i-1}I_{\text{dpc}(i-1)} + (1 - D_{i+1})I_{\text{dpc}_{i+1}}$$

(2.8)

where  $D_i|_{i=1,2,\cdots,n}$  is the duty cycle of each DPC and  $I_{dpc_i}$  is current flowing through each DPCs.

The equation shows that the DPCs process the differential current between each converters. Therefore, the power processed on the DPCs can be achieved by the partial voltage  $(V_{p_i})$

Figure 2.18: Differential power converter (DPC): (a) schematics and (b) VA area model.

partial current  $(I_{dpc_i})$ . The total differential power processed on the DPCs can be written as:

$$\Sigma P_{\mathrm{df}_i} = V_{\mathrm{p}_i} I_{\mathrm{dpc}_i} \tag{2.9}$$

where  $P_{\mathrm{df}_i}$  is the differential power that  $i^{th}|_{i=1,2,\cdots,n}$  DPC processes,  $V_{\mathrm{p}_i}$  is the partial voltage on the series capacitor  $C_{\mathrm{pi}}$ , and  $I_{\mathrm{dpc}_i}$  is the differential current that  $i^{th}$  DPC processes.

The PPP of the DPCs can be visualized by the VA area model as shown in Fig. 2.18 (b). The VA area model shows that the total DPC shares the full input DC voltage  $V_{\rm DC}$ . However, the PPP can be achieved by processing the partial current which is  $I_{\rm dpc_i}$ . If there is the power imbalance between the  $C_{\rm pi}$ , the DPCs will compensate the differential power between each  $C_{\rm pi}$  with  $I_{\rm dpc_i}$ .

According to (2.8) and (2.9), the DPCs process the partial voltage and current which are  $V_{\rm pi}$  and  $I_{\rm dpci}$ . Therefore, the volume of the individual DPC can be reduced by using decreased rating active and passive elements. However, in order to build the DC-DC converter that considering the total i number of DPCs with n DC inputs, the DPCs have to use too many active and passive elements.

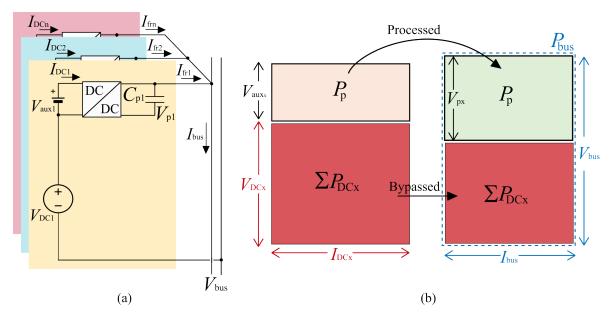

## Fractional power converter

The fractional power converters (FRPC) topology is shown in Fig. 2.19 (a). In order to build the FRPC, auxiliary partial DC voltage sources ( $V_{\text{aux}_x}|_{x=1,2,\cdots,n}$ ) should be used. The DC-DC

Figure 2.19: Fractional power converter (FRPC): (a) schematics and (b) VA area model.

converters process the optimum current for each input sources demands.

In Fig. 2.19 (b), the power processing characteristics of FRPC is described using the VA area model. The VA area model shows that the power processing of the FRPC is similar to the power processing of the FPP that shown in Fig. 2.13 (b). However,  $V_{\text{aux}_x}$  of the FRPC has the lower voltage than the input DC voltage which makes the partial voltages can be processed for each DC-DC converter of the FRPC. The rest of the power,  $\Sigma P_{\text{DC}x}$ , is bypassed directly to the bus side. Therefore, the FRPC can process partial power by controlling the required current,  $I_{\text{DC}x}$ , from the partial voltage of the auxiliary DC sources  $V_{\text{aux}_x}$ . Using the qualitative analysis in Fig. 2.19 (b), the relationship between input and output power can be expressed as follows:

$$V_{\text{bus}} \Sigma I_{\text{frx}} = \Sigma \underbrace{\left(V_{\text{DCx}} I_{\text{DCx}} + \underbrace{V_{\text{aux}_x} I_{\text{DCx}}}_{\text{Processed power}}\right)}_{\text{Bypassed power}}$$

(2.10)

where  $I_{frx}$  is the output current of each FRPC and  $V_{aux_x}$  is the auxiliary voltage of each input port.

The advantage of FRPC is that the conventional low voltage rating DC-DC converters that can process  $V_{\rm aux_x}$ , can be used. However, it is necessary to use auxiliary partial DC voltage sources. Therefore, the additional DC sources increase the cost and volume of the overall system.

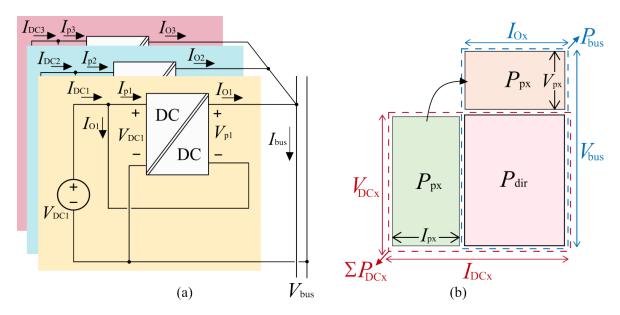

#### Partial power converter

A PPC topology of an input parallel output series partial power converter (IPOS PPC) is depicted in Fig. 2.20 (a). The DC-DC converter of the IPOS PPC is built by the isolated converter topology, which delivers the power from the input to the output port by phase shift modulation. The IPOS PPC has the parallel node on the input which connected to the

Figure 2.20: Input parallel-Output series partial power converter (IPOS PPC) architecture: (a) schematics and (b) VA area model.

negative port of the output and the positive node of the output port is connected in series to the inverter side DC bus. The full DC input voltage  $V_{\rm DCx}$  is applied to the input side of the IPOS PPC. Due to the parallel node on the input side, the following voltage and current relationship can be satisfied:

$$V_{\text{bus}} = V_{\text{DCx}} + V_{\text{px}}$$

$$I_{\text{Ox}} = I_{\text{DCx}} - I_{\text{px}}$$

(2.11)

Therefore, the power processed on the input side of the IPOS PPC can be expressed as  $V_{\rm DCx}I_{\rm px}$ . The processed power expression shows that the partial power on the input side of the IPOS PPC can be achieved by processing full voltage-partial current. The positive node of the output port of IPOS PPC is connected in series between  $V_{\rm bus}$ . A partial voltage  $V_{\rm p}$  is applied to the output of the IPOS PPC. The full output current  $I_{\rm Ox}$  is processed on the inverter DC bus side of the IPOS PPC. Hence, the power processed on the output side of the IPOS PPC is  $V_{\rm p}I_{\rm Ox}$ . This shows that partial power on the output side can be achieved by processing partial voltage-full current. Finally, on the bus side, the total output current of the IPOS PPC flows also can be expressed as  $I_{\rm bus} = \Sigma I_{\rm Ox}$ . Using the voltage applied on the input and output of the IPOS PPC, the processed partial power at the IPOS PPC can be written as follows:

$$P_{\rm px} = V_{\rm DCx}I_{\rm px} = V_{\rm px}I_{\rm Ox} \tag{2.12}$$

where  $P_{\rm px}$  is the partial power processed on the DC-DC converters.

Using (2.12), the energy conservation of input and output of the whole system can be expressed as:

$$V_{DCx}I_{DCx} = V_{DCx}(I_{px} + I_{Ox}) = V_{px}I_{Ox} + V_{DCx}I_{Ox} = V_{bus}I_{Ox}$$

(2.13)

The voltage and current relationship between the input and output of the IPOS PPC can be visualized by the VA area model that depicted in Fig. 2.20 (b). The VA area model of IPOS PPC shows the KCL on the parallel node at the input, where  $I_{\rm Ox}$  is formed by the subtraction between  $I_{\rm DCx}$  and  $I_{\rm px}$ . The figure also shows that the sum of  $V_{\rm DCx}$  and  $V_{\rm px}$  yields  $V_{\rm bus}$ . This means that the IPOS PPC is suitable for the application where  $V_{\rm DCx} < V_{\rm bus}$  (Boost applications). The relationship between the processed power of the IPOS PPC and the input-output power can be written as follows:

$$\underbrace{V_{\text{DCx}}I_{\text{px}} = V_{\text{px}}I_{\text{Ox}}}_{\text{processed power on the IPOS PPC}} < \underbrace{V_{\text{DCx}}I_{\text{DCx}} = V_{\text{bus}}I_{\text{Ox}}}_{\text{System power}}$$

(2.14)

Equation (2.14) shows that the processed power on the IPOS PPC is lower than the inputoutput power. Therefore, the IPOS PPC can use the devices with a lower power rating, resulting in reducing the size of the IPOS PPC. Finally, the rest of the power which is not processed on the IPOS PPC can be written as:

$$P_{\text{dir}} = V_{\text{DCx}}I_{\text{DCx}} - V_{\text{DCx}}I_{\text{Dx}} = V_{\text{DCx}}I_{\text{Ox}}$$

(2.15)

where  $P_{\text{dir}}$  is the unprocessed power which is the power directly bypassed to the  $V_{\text{bus}}$  without the power processing by the IPOS PPC.

Figure 2.21: Input series-Output parallel partial power converter (ISOP PPC): (a) schematics and (b) VA area model.

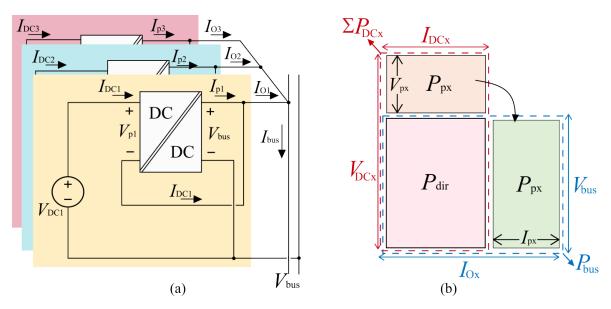

Another PPC topology called input series output parallel partial power converter (ISOP PPC) is depicted in Fig. 2.21 (a). The DC-DC converter of the ISOP PPC is also built by the isolated converter topology which delivers the power from the input to output as the same

manner of IPOS PPC. The ISOP PPC has symmetrical topology compared to the IPOS PPC where the converter has series connection between the DC inputs, and the parallel node on the output which connected to the negative port of the input. The voltage-current relationship at the parallel node of the ISOP PPC can be expressed as:

$$V_{\text{bus}} = V_{\text{DCx}} - V_{\text{px}}$$

$$I_{\text{Ox}} = I_{\text{DCx}} + I_{\text{px}}$$

(2.16)

On the input side of the ISOP PPC,  $V_p$  is applied with processing full input current  $I_{DCx}$ . On the bus side, the partial current  $I_{px}$  is processed with the full bus voltage  $V_{bus}$ . Eventually, the  $P_{px}$  processed on the single ISOP PPC can be expressed as follows:

$$P_{\rm px} = V_{\rm px}I_{\rm DCx} = V_{\rm bus}I_{\rm px} \tag{2.17}$$

The equation shows that the partial power on the input side is achieved by processing partial voltage-full current, and on the inverter bus side can be achieved by processing full voltage-partial current. Using (2.17), the energy conservation of the input and output of the ISOP applied system also can be written as follows:

$$V_{\text{bus}}I_{\text{Ox}} = V_{\text{bus}}(I_{\text{px}} + I_{\text{DCx}}) = V_{\text{px}}I_{\text{DCx}} + V_{\text{bus}}I_{\text{DCx}} = V_{\text{DCx}}I_{\text{Ox}}$$

(2.18)

The voltage and current relationship between the input and output of the ISOP PPC can be visualized by the VA area model that depicted in Fig. 2.21 (b). The VA area model shows the voltage and current flow of the ISOP PPC has the symmetric characteristic compared to the IPOS PPC which also means that the ISOP PPC is optimal for the buck applications. The relationship of the processed power on the ISOP PPC and the input-output power can be written as follows:

$$\underbrace{V_{\text{px}}I_{\text{DCx}} = V_{\text{bus}}I_{\text{px}}}_{\text{processed power on the ISOP PPC}} < \underbrace{V_{\text{DCx}}I_{\text{DCx}} = V_{\text{bus}}I_{\text{Ox}}}_{\text{System power}}$$

(2.19)

Equation (2.19) also shows that the processed power on the ISOP PPC is lower than the input-output power. Therefore, the ISOP PPC can use decreased power rating devices which yield the decrease of the converter size. Finally, the unprocessed power  $P_{\rm dir}$  can be written as:

$$P_{\text{dir}} = V_{\text{DCx}} I_{\text{DCx}} - V_{\text{p}} I_{\text{DCx}} = V_{\text{bus}} I_{\text{DCx}}$$

(2.20)

#### **Comparison of the PPP architectures**

The comparison of the PPP architectures are shown in Table. 2.2. In the table, 'n' represents the number of DC inputs and 'i' represents the number of series connected DC-DC

| Architecture | Transformer | V <sub>aux</sub> | Switches     | <i>P</i> <sub>p</sub> (p.u.) | cost | size |

|--------------|-------------|------------------|--------------|------------------------------|------|------|

| DPC          | X           | X                | $2n \cdot i$ | 0.15                         | -    | +    |

| FRPC         | X           | n                | 2 <i>n</i>   | 0.25                         | -    | -    |

| PPC          | n           | X                | 8 <i>n</i>   | 0.3                          | +    | -    |

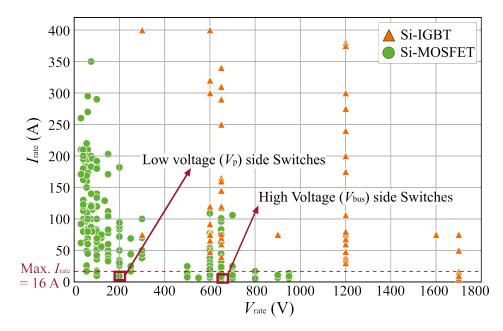

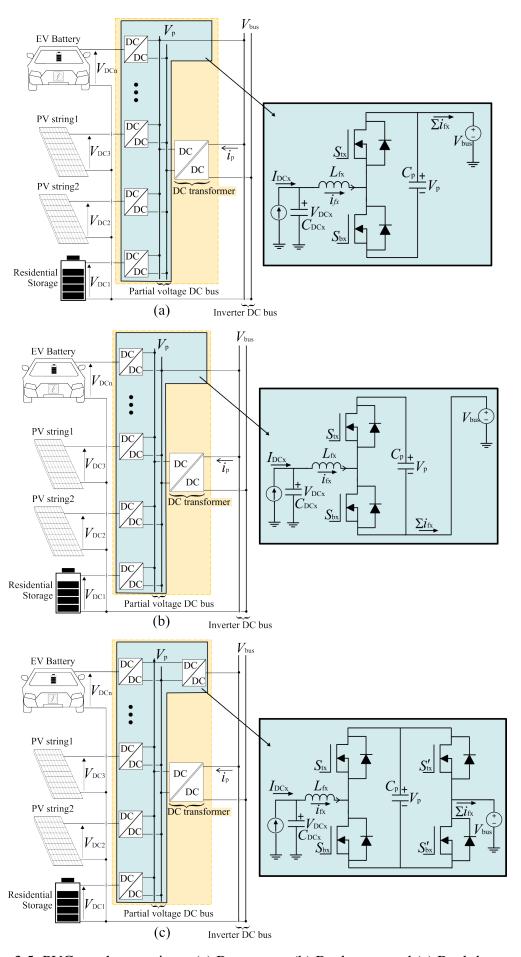

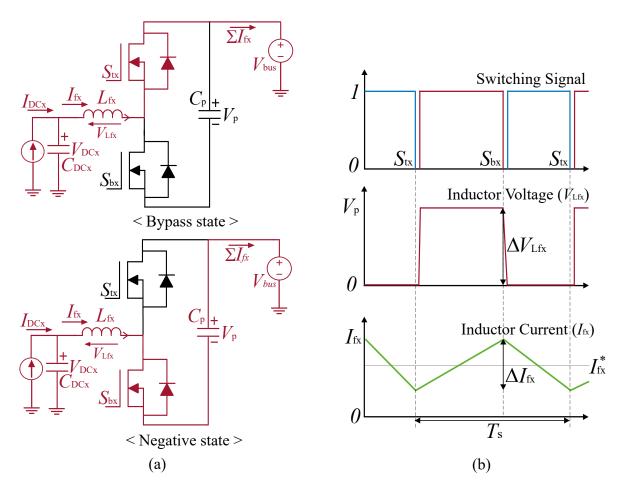

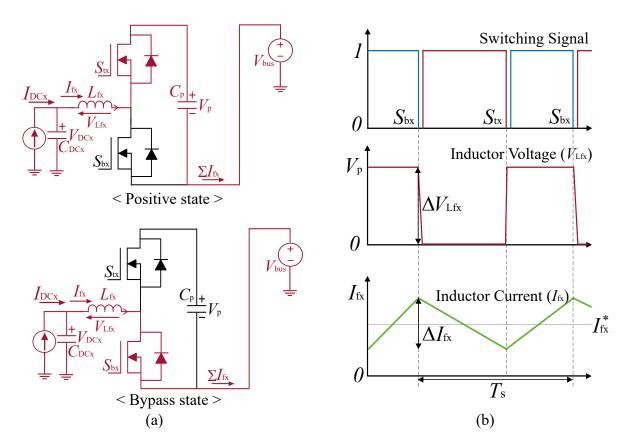

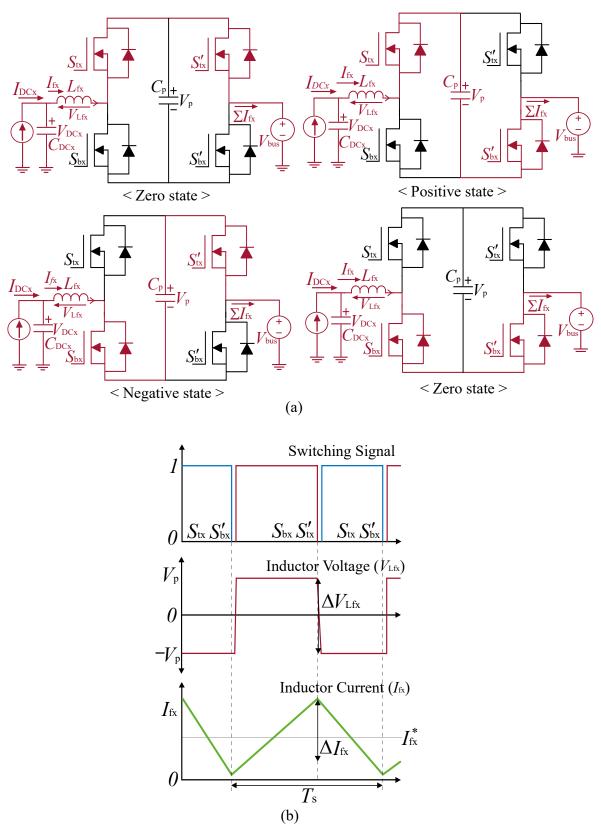

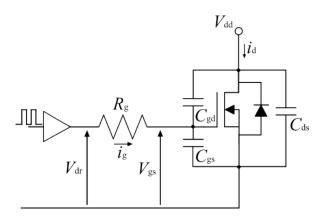

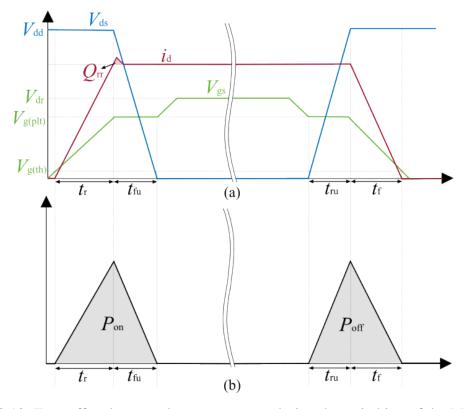

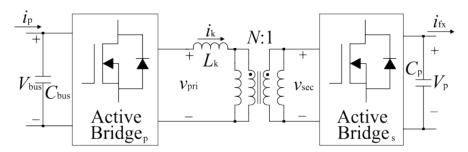

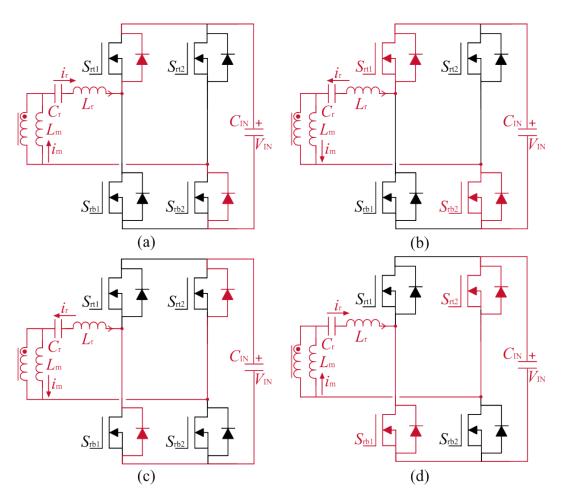

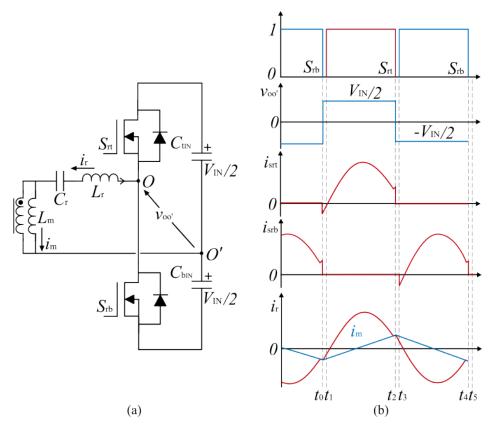

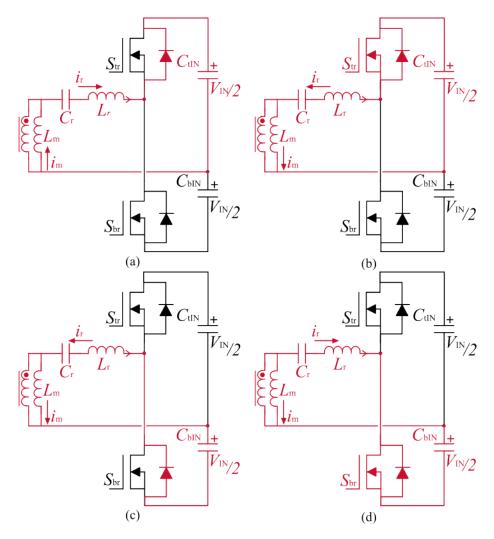

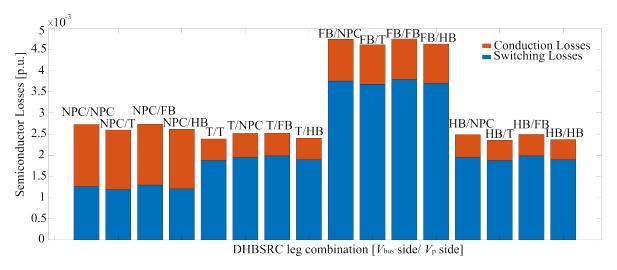

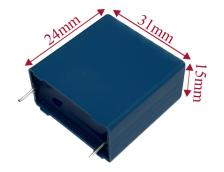

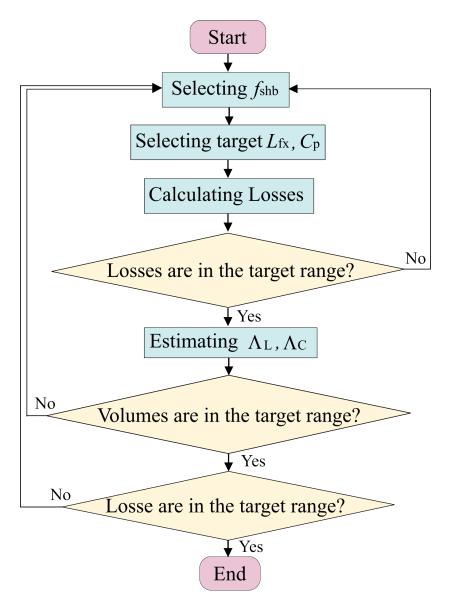

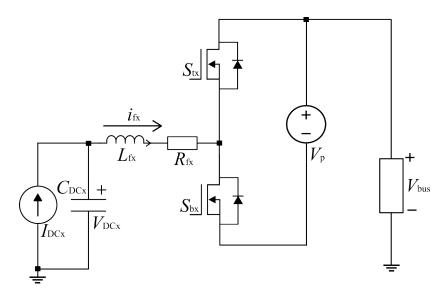

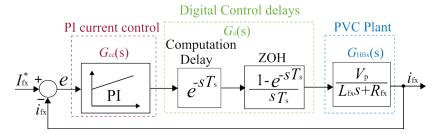

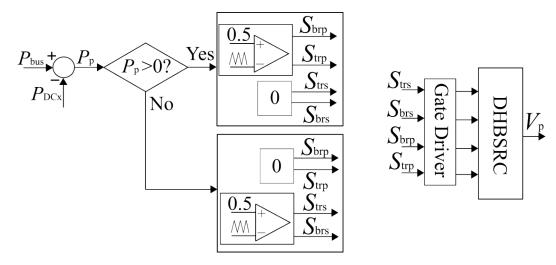

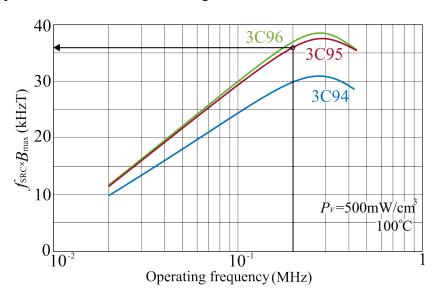

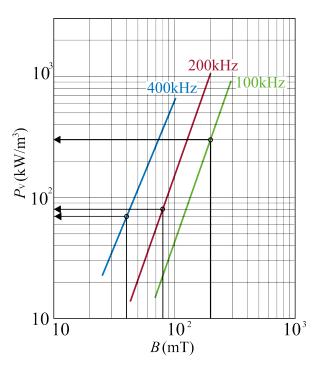

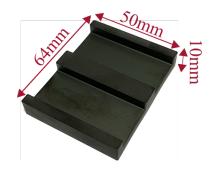

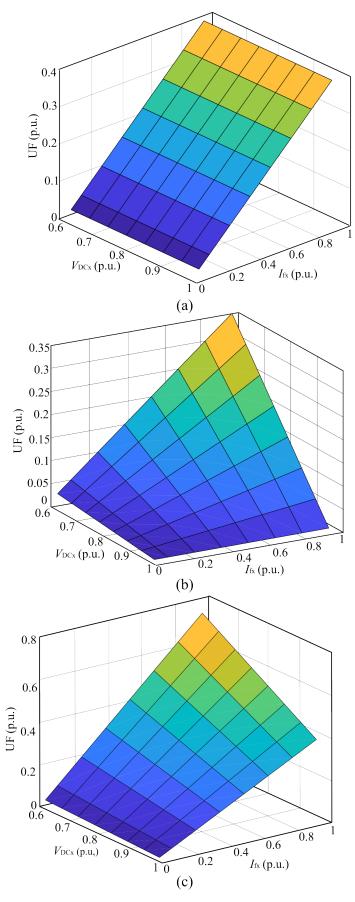

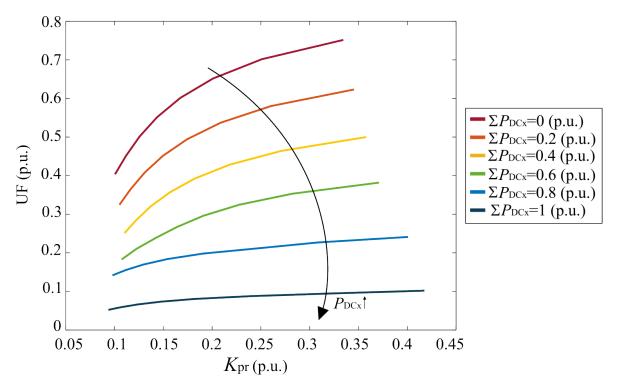

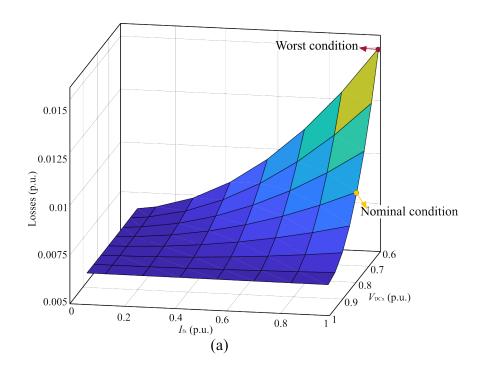

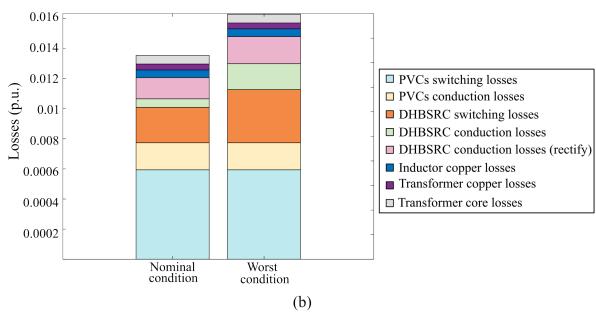

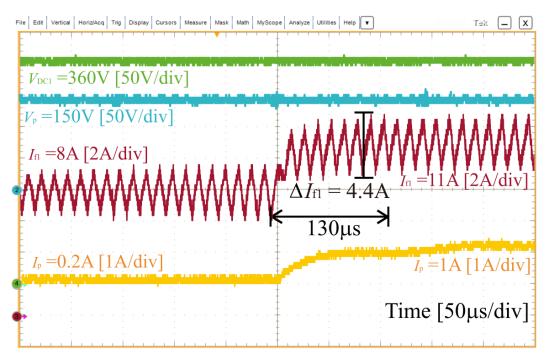

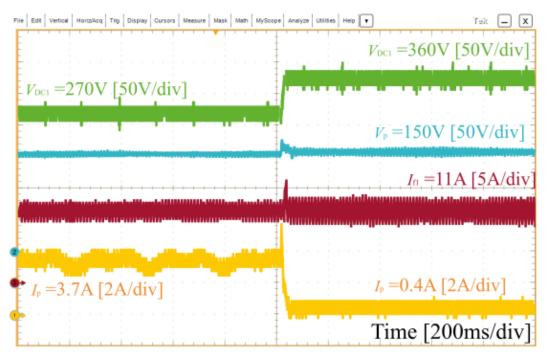

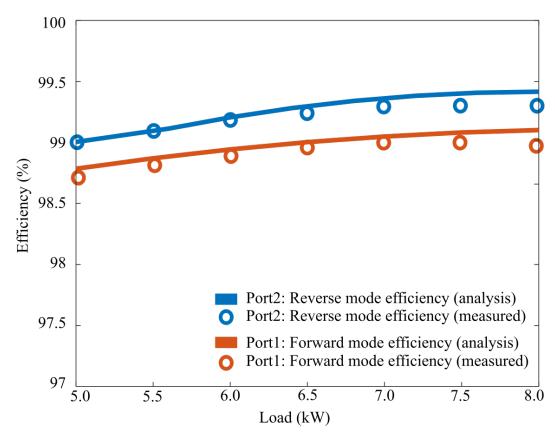

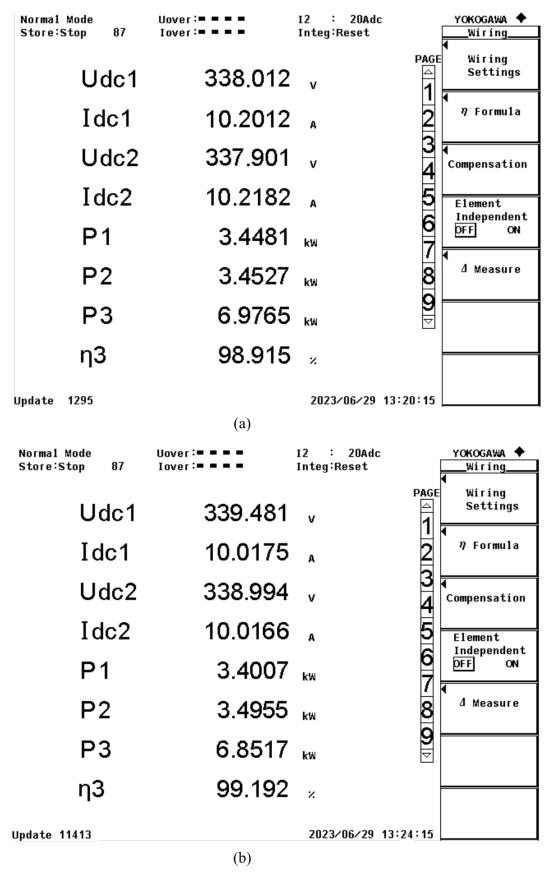

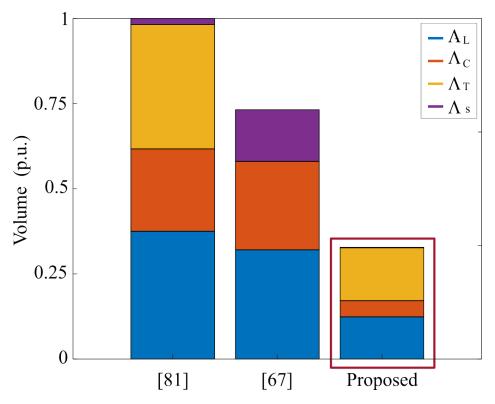

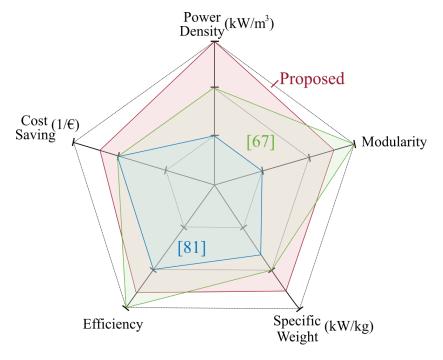

Table 2.2: Comparison of PPP architectures